Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

PCI и PCI-X

Шины PCI и PCI-X

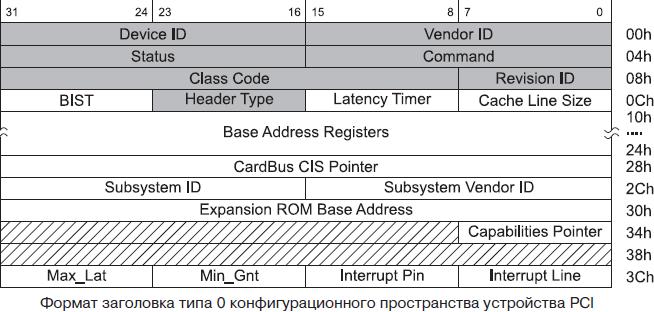

Конфигурационное пространство обычных устройств (тип 0)

Формат заголовка конфигурационного пространства приведен на рисунке ниже, серым цветом здесь выделены поля, обязательные для всех устройств; регистры, специфичные для устройства, могут занимать адреса конфигурационного пространства в пределах 40–FFh.

Перечисленные ниже поля идентификации допускают только чтение:

- Device ID — идентификатор устройства, назначаемый производителем;

- Vendor ID — идентификатор производителя микросхемы PCI, назначенный PCI SIG. Идентификатор FFFFh является недопустимым; это значение должно возвращаться при чтении конфигурационного пространства несуществующего устройства;

- Revision ID — версия продукта, назначенная производителем. Используется как расширение поля Device ID;

- Header Type — тип заголовка (биты [6:0]), определяющий формат ячеек в диапазоне 10–3Fh и несущий признак многофункционального устройства (если бит 7 установлен). На рисунке приведен формат заголовка типа 0, относящийся именно к устройствам PCI. Тип 01 относится к мостам PCI-PCI; тип 02 относится к мостам для CardBus;

- Class Code — код класса, определяющий основную функцию устройства, а иногда и его программный интерфейс (см. далее). Старший байт (адрес 0Bh) определяет базовый класс, средний — подкласс, младший — программный интерфейс (если он стандартизован).

Остальные поля заголовка являются регистрами устройств, допускающими как запись, так и чтение.

Регистр команд Command (RW) служит для управления поведением устройства на шине PCI. Регистр допускает как запись, так и чтение. После аппаратного сброса все биты регистра (кроме специально оговоренных исключений) обнулены.

Назначение бит регистра команд:

- бит 0 — IO Space — разрешение ответа на обращения к пространству вводавывода;

- бит 1 — Memory Space — разрешение ответа на обращения к пространству памяти;

- бит 2 — Bus Master — разрешение работы инициатором (в режиме прямого управления шиной); игнорируется в PCI-X при завершениях расщепленных транзакций;

- бит 3 — Special Cycles — разрешение реакции на специальные циклы;

- бит 4 — Memory Write& and Invalidate enable — разрешение использовать команды «запись с инвалидацией» при работе инициатором (если бит обнулен, то вместо этих команд должна использоваться обычная запись в память); игнорируется в PCI-X;

- бит 5 — VGA palette snoop — разрешение слежения за записью в регистр палитр;

- бит 6 — Parity Error Response — разрешение нормальной реакции (вырабатывать сигнал PERR#) на обнаруженную ошибку четности или ECC. Если бит обнулен, то устройство должно только фиксировать ошибку в регистре состояния и продолжать выполнение транзакции; при ECC-контроле данные об ошибке записываются в регистры ECC;

- бит 7 — Stepping Control — возможность пошагового переключения (address/data stepping) линий (если устройство никогда этого не делает, бит регистра «запаян» в «0», если делает всегда — в «1», устройство с такой возможностью по сбросу устанавливает этот бит в «1»). В версии 2.3 и PCI-X бит освобожден (в связи с отменой степинга);

- бит 8 — SERR# Enable — разрешение генерации сигнала ошибки SERR# (ошибка адреса сообщается, когда этот бит и бит 6 установлены);

- бит 9 — Fast Back-to-Back Enable (необязательный, игнорируется в PCI-X) — разрешение ведущему устройству использовать быстрые смежные обращения к разным устройствам (если бит обнулен, быстрые обращения допустимы лишь для транзакций с одним агентом);

- бит 10 Interrupt Disable —, запрет генерации сигнала прерываний по линиям INTx (по аппаратному сбросу и включению питания бит обнулен — прерывания разрешены). Бит определен начиная с PCI 2.3. Ранее был резервным;

- биты [11:15] — резерв.

Регистр Status служит для определения состояния и свойств устройства. Биты, помеченные как RO, допускают только считывание. Другие биты регистра могут быть программно модифицированы операцией записи, с помощью которой можно только обнулять биты, но не устанавливать. При записи в позиции обнуляемых бит устанавливаются единичные значения. Назначение бит регистра состояния:

- биты [0:2] — резерв;

- бит 3— Interrupt Status (RO), наличие запроса прерывания. Устанавливается в единицу перед подачей сигнала по линии INTx, независимо от значения бита Interrupt Disable. С прерываниями MSI не связан. Бит определен начиная с PCI 2.3, ранее был резервным. В PCI-X 2.0 бит обязателен;

- бит 4 — Capability List (RO, необязательный) — признак наличия указателя новых возможностей в регистре со смещением 34h;

- бит 5 — 66 MHz Capable (RO, необязательный) — признак поддержки частоты 66 МГц;

- бит 6 — резерв;

- бит 7 — Fast Back-to-Back Capable (RO, необязательный) — признак поддержки быстрых смежных транзакций (fast back-to-back) с разными устройствами;

- бит 8 — Master Data Parity Error (только для устройств с прямым управлением) — инициатор (запросчик) транзакции обнаружил неисправимую ошибку данных;

- биты [10:9] — DEVSEL Timing — скорость выборки: 00 — быстрая, 01 — средняя, 10 — низкая (определяет самую медленную реакцию DEVSEL# на все команды, кроме Configuration Read и Configuration Write);

- бит 11 — Signaled Target Abort — устанавливается целевым устройством, когда оно отвергает транзакцию;

- бит 12 — Received Target Abort — устанавливается инициатором, когда он обнаруживает отвергнутую транзакцию;

- бит 13 — Received Master Abort — устанавливается ведущим устройством, когда оно отвергает транзакцию (кроме специального цикла);

- бит 14 — Signaled System Error — устанавливается устройством, подавшим сигнал SERR#;

- бит 15 — Detected Parity Error — устанавливается устройством, обнаружившим ошибку данных.

Регистр Cache Line Size (RW) служит для задания размера строки кэша (0–128, допустимые значения 2n, иные трактуются как 0). По этому параметру инициатор определяет, какой командой чтения воспользоваться (обычное чтение, чтение строки или множественное чтение). Ведомое устройство использует этот параметр для поддержки пересечения границ строк при пакетных обращениях к памяти. По сбросу регистр обнуляется.

Регистр Latency Timer (RW) задает значение таймера, ограничивающего длину транзакции при снятии сигнала GNT# (см. главу 2). Значение указывается в виде числа тактов шины, часть битов может не допускать изменения (обычно младшие три бита неизменны, так что таймер программируется с дискретностью в 8 тактов).

Регистр BIST (RW) служит для управления встроенным самотестированием (BuiltIn Self Test). Назначение бит регистра:

- бит 7 — возможность BIST;

- бит 6 — запуск теста: запись единицы инициирует тест, по окончании устройство сбрасывает бит (тест должен быть завершен не более чем за 2 с);

- биты [5:4] — резерв (0);

- биты [3:0] — код завершения теста: 0 — тест прошел успешно.

Регистр Card Bus CIS Pointer (необязательный) содержит указатель на структуру описателя Card Bus для комбинированного устройства PCI + Card Bus.

Регистр Interrupt Line (RW) хранит номер входа контроллера прерывания для используемой линии запроса (0–15 — IRQ0–IRQ15, в системах с APIC может иметь и большее значение; 255 — неизвестный вход или не используется).

Регистр Interrupt Pin (RO) задает линию, используемую для запроса прерывания: 0 — не используется, 1 — INTA#, 2 — INTB#, 3 — INTC#, 4 — INTD#, 5–FFh — резерв.

Регистр Min_GNT (RO) задает минимальное время, на которое ведущему устройству должно предоставляться управление шиной из расчета на частоту 33 МГц, в интервалах по 0,25 мкс.

Регистр Max_Lat (RO) задает максимально допустимую задержку предоставления ведущему устройству доступа к шине, в интервалах по 0,25 мкс (0 — нет специальных требований).

Регистры Subsystem ID (RO, задается производителем) и Subsystem Vendor ID (RO, производитель получает в PCI SIG) хранят идентификаторы, позволяющие точно идентифицировать карты и устройства (в системе могут быть установлены несколько карт с совпадающими идентификаторами устройства и производителя Device ID и Vendor ID). В поле 2Ch ставится идентификатор производителя карты PCI (может совпадать со значением в поле 0, если фирма выпускает и микросхемы, и карты).

Регистр Capability Pointer (CAP_PTR) содержит указатель на цепочку блоков регистров свойств функции, представленных в конфигурационных регистрах. Каждый блок представляет собой набор регистров, начинающийся с границы двойного слова (в указателе биты [1:0] сброшены). Каждый блок начинается с байта идентификатора типа свойства (CAP_ID, определенный PCI SIG), за которым следует указатель на следующий блок (нулевой указатель является признаком конца списка блоков), после чего расположены байты описаний самих свойств. Через CAP_PTR, например, отыскиваются регистры управления энергопотреблением (если есть), регистры AGP, некоторые регистры хост-контроллера USB 2.0 и ряд других.

Регистры Base Address Registers (BAR) описывают области памяти и портов ввода-вывода. Программными манипуляциями с регистрами можно определить размеры областей. Для областей памяти и портов описания различаются:

- область памяти (размером не более 2 Гбайт) описывается следующим образом:

---бит 0 = 0 — признак памяти;

---биты [2:1] — тип адресации: 00 — 32-битная адресация, 10 — 64-битная (в этом

случае регистр расширяется следующим за ним 4-байтным словом, 64-битная адресация обязательна для PCI-X), 01 и 11 — резерв (01 в прежних версиях предназначались для памяти в пределах первого мегабайта);

---бит 3 (Prefetchable) — признак «настоящей» памяти, то есть допускающей предвыборку;

---биты [31:4] — базовый адрес памяти; - область портов (размером до 256 байт) описывается следующим образом:

---бит 0 = 1 — признак области портов;

---бит 1 = 0 (резерв);

---биты [31:2] — базовый адрес блока портов.

Регистр Expansion ROM Base Address управляет адресацией ПЗУ программной поддержки устройства. Размер ПЗУ определяется так же, как и в регистрах базовых адресов (см. выше). Обращение к ПЗУ возможно лишь при разрешенном использовании памяти (бит 1 в регистре команд). Назначение бит регистра:

- бит 0 — разрешение использования ПЗУ;

- биты [1:10] — резерв;

- биты [11:31] — базовый адрес.

Карты PCMCIA: интерфейсы PC Card, CardBus

В начале 90-х годов организация PCMCIA (Personal Computer Memory Card International Association — Международная ассоциация производителей карт памяти для персональных компьютеров) начала работы по стандартизации шин расширения блокнотных компьютеров, в первую очередь предназначенных для расширения памяти. Первым появился стандарт PCMCIA Standard Release 1.0/JEIDA 4.0 (июнь 1990 года), в котором был описан 68-контактный интерфейсный разъем и два типоразмера карт: Type I и Type II PC Card. Поначалу стандарт касался электрических и физических требований только для карт памяти. Был введен метаформат информационной структуры карты CIS (Card Information Structure), в которой описываются характеристики и возможности карты, — ключевой элемент взаимозаменяемости карт и обеспечения механизма PnP.

Следующая версия PCMCIA 2.0 (1991 год) для того же разъема определила интерфейс операций ввода-вывода, двойное питание для карт памяти, а также методики тестирования. В версии 2.01 были добавлены спецификация PC CardATA, новый типоразмер Type III, спецификация автоиндексируемой массовой памяти AIMS (Auto-Indexing Mass Storage) и начальный вариант сервисной спецификации (Card Services Specification). В версии 2.1 (1994 год) расширили спецификации сервисов карт и сокетов (Card and Socket Services Specificaiton) и развили структуру CIS.

Стандарт PC Card (1995 год) явился продолжением предыдущих; в нем введены дополнительные требования для улучшения совместимости и новые возможности: питание 3,3 В, поддержка DMA, а также 32-битной шины PCI — CardBus. В дальнейшем в стандарт были введены и другие дополнительные возможности.

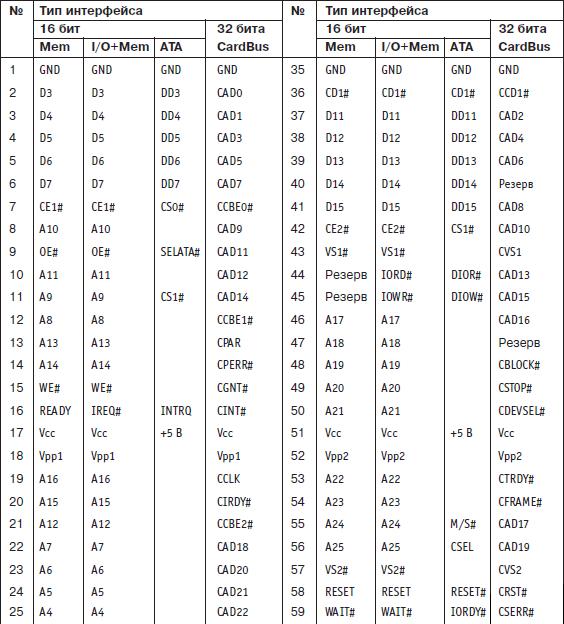

Все карты PCMCIA и PC Card имеют 68-контактный разъем, назначение контактов у которого варьирует в зависимости от типа интерфейса карты. Тип интерфейса «заказывается» картой при установке ее в слот, который, естественно, должен поддерживать требуемый интерфейс. Интерфейс памяти обеспечивает 8- и 16-битные обращения с минимальным временем цикла 100 нс, что дает максимальную производительность 10 и 20 Мбайт/с соответственно. Интерфейс ввода-вывода имеет минимальную длительность цикла 255 нс, что соответствует 3,92/7,84 Мбайт/с для 8-/16-битных обращений. Интерфейс CardBus поддерживает протокол обмена PCI; тактовая частота 33 МГц, разрядность 32 бита. Здесь используется та же система автоматического конфигурирования, что и в PCI (через регистры конфигурационного пространства). В интерфейс заложены дополнительные возможности для цифровой передачи аудиосигнала, причем как в традиционной форме ИКМ (PCM), так и в новой (забытой старой) форме ШИМ (PWM). Для дисковых устройств ATA в формате PC Card имеется специальная спецификация интерфейса.

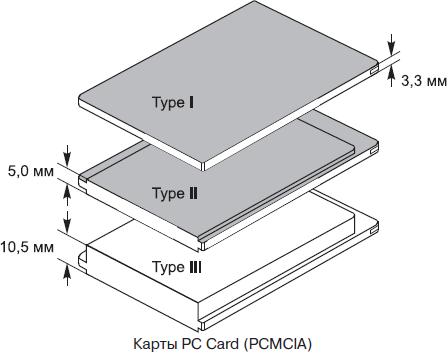

Существует несколько конструктивных типов PC Card: у них у всех размер в плане 54×85,5 мм, но разная толщина (меньшие адаптеры встают в большие гнезда):

- PC Card Type I — 3,3 мм — карты памяти;

- PC Card Type II — 5 мм — карты устройств ввода-вывода, модемы, адаптеры локальных сетей;

- PC Card Type III — 10,5 мм — дисковые устройства хранения;

- PC Card Type IV — 16 мм.

Есть еще и маленькие карты Small PC Card размером 45×42,8 мм с тем же коннектором и теми же типами по толщине.

Большинство карт PC Card выпускается с поддержкой технологии PnP и предусматривает «горячее» подключение — интерфейсные карты могут вставляться и выниматься без выключения компьютера. Для этого контакты шин питания имеют большую длину, чем сигнальные, обеспечивая их упреждающее подключение и запаздывающее отключение. Два контакта обнаружения карты CD1# и CD2# (Card Detect) короче остальных — их замыкание для хоста означает, что карта полностью вставлена в слот. Несмотря на возможность динамического конфигурирования, в некоторых случаях при изменении конфигурации требуется перезагрузка системы.

Первоначально карты и хост-системы использовали напряжение питания логики +5 В. Для перехода на низковольтное питание (3,3 В) был введен механический ключ, не допускающий установки карты на 3,3 В в слот, дающий только 5 В. Кроме того, были определены контакты 43 (VS1#) и 57 (VS2#) для выбора питающего напряжения. На картах с питанием 5 В они оба свободны; на картах 3,3 В контакт VS1# заземлен, а VS2# свободен. По этим линиям хост, допускающий оба варианта напряжения питания, определяет потребности установленной карты и подает соответствующее напряжение. Если хост не способен обеспечить требуемый номинал, он должен не подавать питание, а выдать сообщение об ошибке подключения. Карты обычно поддерживают управление энергопотреблением (APM), что особо актуально при автономном питании компьютера.

В стандарте PC Card выпускают самые разнообразные устройства — память, устройства хранения, коммуникационные средства, интерфейсные порты, игровые адаптеры, мультимедийные устройства и т. п., правда, все они существенно дороже своих крупногабаритных аналогов. Через слот PC Card портативные компьютеры могут подключаться к док-станциям, в которые может быть установлена обычная периферия. Недостаточно строгое следование производителей стандарту иногда приводит к проблемам совместимости.

Слоты PC Card подключаются к системной шине блокнотного ПК через мост; для компьютеров с внутренней шиной PCI это будет мост PCI–PC Card. В блокнотных ПК могут быть и слоты Small PCI (SPCI, см. выше), но они недоступны без вскрытия корпуса и не допускают «горячей» замены устройств.

Настольный ПК можно снабдить слотами PC Card с помощью специальной карты адаптера-моста, устанавливаемой в слот PCI или ISA. Сами слоты PC Card(1–2 штуки) оформляются в корпус трехдюймового устройства и выводятся на лицевую панель ПК; этот корпус соединяется с картой-мостом ленточным кабелем-шлейфом.

Таблица. Разъем PC Card (PCMCIA)

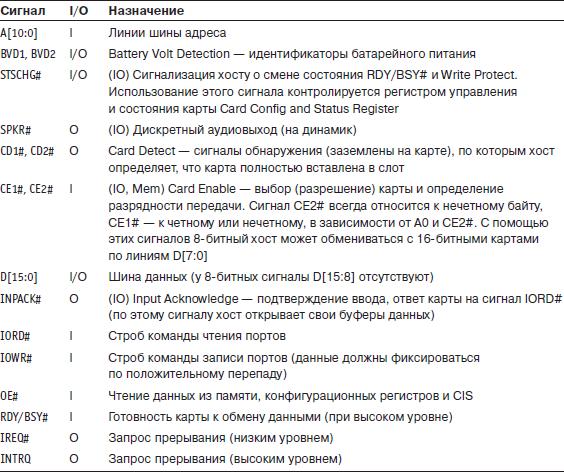

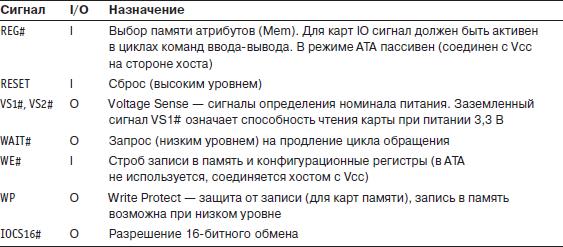

Таблица. Назначение сигналов карт памяти и ввода-вывода

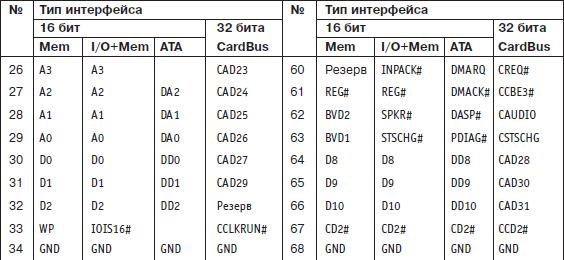

Продолжение таблицы

Интерфейс карт памяти и ввода-вывода прост — он практически совпадает с интерфейсом статической асинхронной памяти. Карта выбирается сигналами CE#, действующими одновременно с установленным адресом. Чтение памяти и конфигурационных регистров выполняется по сигналу OE#, запись — по сигналу WE#. Признаком, разделяющим в этих обращениях основную память и конфигурационные регистры, принадлежащие области памяти атрибутов карты, является сигнал REG#, действующий одновременно с CE# и адресом. Для обращения к портам ввода-вывода служат отдельные сигналы IORD# и IOWR#; во время их действия должен быть активен и сигнал REG#. В процессе обращения к портам карта может выдать признак возможности 16-битных обращений сигналом IOSC16# (как на шине ISA). Чтение порта устройство должно подтверждать сигналом INPACK#, устанавливаемым и снимаемым картой по сигналу CE#. Благодаря этому сигналу хост может убедиться в том, что он читает не пустой слот.

Для мультимедийных карт имеется возможность переключения интерфейса в специальный режим ZV Port (Zoomed Video), в котором организуется отдельный двухточечный интерфейс передачи данных между картой и хост-системой. По смыслу интерфейс напоминает коннектор VFC графических карт — выделенная шина для передачи видеоданных, не связанная с остальными шинами (и не загружающая их), но имеет иной протокол. В режиме ZV Port адресные линии A[25:4], а также линии BVD2/SPKR#, INPACK# и I0IS16# получают иное назначение — по ним передаются видеоданные и 4 цифровых аудиоканала. Для обычного интерфейса остаются лишь 4 адресные линии, позволяющие адресоваться к 16 байтам общей памяти и атрибутов карты.

Интерфейс порта ZV соответствует временным диаграммам CCIR601, что позволяет декодеру NTSC в реальном времени доставлять видеоданные с карты в экранный буфер VGA. Видеоданные могут поступать на карту как с внешнего видеовхода, так и с декодера MPEG.

Карты имеют специальное выделенное пространство памяти атрибутов, в котором находятся конфигурационные и управляющие регистры карты, предназначенные для автоконфигурирования. Стандартом описан формат информационной структуры карты (Card Information Structure, CIS). Карты могут быть многофункциональными (например, комбинация модема и сетевого адаптера). В спецификации MFPC (Multiple Function PC Cards) для каждой функции предусматриваются отдельные конфигурационные регистры и определяются правила разделения (совместного использования) линии запроса прерывания.

Для устройств внешней памяти стандарт описывает форматы хранения данных, совместимые с FAT MS-DOS, а также ориентированные на флэш-память как основной носитель информации. Для непосредственного исполнения модулей ПО, хранящихся в ПЗУ карты, имеется спецификация XIP (eXecute In Place), описывающая программный интерфейс вызова этих модулей (вместо загрузки ПО в ОЗУ).

Стандарт описывает программный интерфейс сервисов карт (Card Services), обеспечивающий унификацию взаимодействия его клиентов (драйверов, прикладного ПО и утилит) с устройствами. Имеется также и интерфейс сервисов сокета (Socket Services), с помощью которого выполняются операции, связанные с обнаружением фактов подключения-отключения карт, их идентификации, конфигурирования питания и аппаратного интерфейса.

В стандарте имеются описания специфических особенностей, свойственных двум организациям, ведущим стандарт PC Card:

- PCMCIA описывает автоиндексируемую массовую память (AIMS) для хранения больших массивов данных (изображений, мультимедийных данных) на блочно-ориентированных устройствах. Имеется также спецификация 15-контактного экранированного разъема для подключения модемов и адаптеров локальной сети (15-pin Shielded Modem I/O connector) и 7-контактного для подключения модемов (7-pin Modem I/O connector);

- JEDIA для карт памяти предлагает формат файлов Small Block Flash Format, упрощающий файловую систему. Формат SISRIF (Still Image, Sound and Related Information Format) предназначен для записи изображений и звука на карты памяти. Имеется и спецификация для карт динамической памяти.

Взаимодействие устройств

С программной точки зрения устройство PCI может иметь следующие компоненты:

- конфигурационные регистры, используемые для идентификации и начального конфигурирования устройства при инициализации системы. Для всех устройств предусмотрен обязательный набор конфигурационных регистров, остальные регистры могут использоваться для текущего управления;

- операционные регистры (необязательные), отображенные на пространство памяти и/или ввода/вывода; эти регистры используются для текущего управления и взаимодействия с устройством;

- локальная память (необязательная), отображенная на выделенные области физических адресов системной памяти;

- источники запросов на прерывания;

- мастер шины, обеспечивающий прямой доступ к системной памяти (DMA) и взаимодействие с другими устройствами.

С устройством PCI, когда оно является целевым, можно взаимодействовать несколькими способами:

- командами обращения к памяти и портам ввода/вывода; эти команды адресуются к областям, выделенным устройству при конфигурировании;

- командами обращения к конфигурационным регистрам; эти команды адресуются по идентификатору — номеру шины, устройства и функции (компонента многофункционального устройства PCI);

- специальными широковещательными сообщениями, передаваемыми для всех устройств выбранной шины;

- командами пересылки сообщений; команды адресуются по идентификатору устройства (эта возможность появилась в PCI-X 2.0);

Для обращений к пространству памяти используется 32-битная или 64-битная адресация, причем разрядность адресации не зависит от разрядности шины. Таким образом, шина позволяет адресовать до 232 (4 Гбайт) или 264 (более 16 тыс. Пбайт) байт памяти. На шине PCI фигурирует физический адрес памяти. Для адресации портов ввода/вывода используется 32-битная адресация; в компьютерах на базе процессоров x86 из них используются только 16 младших бит. В системе адресации ввода/вывода имеется поддержка особенностей, связанных с адресацией портов в PC-совместимых компьютерах с шиной ISA. Для устройств PCI и PCI-X рекомендуется по возможности избегать использования портов ввода/вывода; операционные регистры устройств рекомендуется отображать на пространство памяти (Memory-Mapped I/O).

Конфигурационные регистры устройств PCI расположены в обособленном пространстве адресов (отдельном от пространства адресов памяти и ввода/вывода). Каждому устройству (точнее, каждой функции сложного устройства) выделяется 256-байтный блок конфигурационных регистров; в спецификации PCI-X 2.0 размер блока увеличен до 4096 байт. Частью этого блока является обязательный набор конфигурационных регистров, с помощью которых осуществляются идентификация устройств, их конфигурирование и управление их свойствами. В конфигурационных регистрах, в частности, указываются адреса, отведенные устройству (как целевому); через них разрешается работа в роли инициатора и целевого устройства, конфигурируются прерывания. Конфигурационные регистры обеспечивают возможность автоматической настройки всех устройств шины PCI. К этим регистрам система обращается на этапе конфигурирования — переучета обнаруженных устройств, выделения им неперекрывающихся ресурсов (областей памяти и пространства ввода/вывода) и назначения номеров аппаратных прерываний. При дальнейшей регулярной работе взаимодействие прикладного ПО с устройствами осуществляется преимущественно путем обращений по назначенным в процессе конфигурирования адресам памяти и ввода/вывода. Конфигурационные же регистры в регулярной работе используются для системных целей: настройки параметров, описывающих поведение устройства на шине, обработки ошибок, идентификации источника прерываний.

Обращения к регистрам и памяти устройств PCI выполняются командами шины PCI. Команды может подавать любой инициатор: как хост (главный мост) по командам центрального процессора, так и рядовое устройство PCI. Возможность распространения ряда команд зависит от взаимного расположения инициатора и целевого устройства на «ветвях» дерева шин PCI. Однако хост может безусловно подавать любую команду любому устройству PCI. Только хост всегда (и по начальному включению) имеет доступ к конфигурационным регистрам всех устройств (и мостов), поэтому он и должен заниматься конфигурированием. После конфигурирования любое устройство PCI может безусловно обратиться к системной памяти, то есть реализовать прямой доступ к памяти (DMA).

Устройства PCI могут вырабатывать запросы аппаратных прерываний:

- обычных маскируемых — для сигнализации событий в устройстве; эти прерывания могут сигнализироваться как традиционным способом — по специальным сигнальным линиям, так и передачей сообщений (MSI);

- немаскируемых — для сигнализации о серьезных ошибках;

- прерываний системного управления (SMI) — для сигнализации о событиях в системе управления энергопотреблением и некоторых системных целей (например, эмуляции работы стандартного контроллера клавиатуры с помощью устройств USB).

Наиболее эффективно возможности шины PCI используются при применении активных устройств — мастеров шины (PCI Bus Master). Только эти устройства могут обеспечить скорость передачи данных, приближающуюся к декларированной пиковой пропускной способности. Максимальная производительность обменов по шине PCI достигается только в пакетных транзакциях значительной длины. Транзакции по инициативе программы, исполняемой на ЦП, проводимые главным мостом, как правило, являются одиночными (или очень короткими пакетными). По этой причине программно-управляемый обмен данными с устройствами PCI по производительности значительно уступает обмену, выполняемому устройством-мастером. Таким образом, применение активных устройств дает двойной эффект: разгружает центральный процессор и обеспечивает лучшее использование пропускной способности шины.

Адресация памяти

На шине PCI передается физический адрес памяти; в процессорах x86 (и других) он получается из логического посредством постраничной табличной трансляции блоком MMU.

В командах обращения к памяти на шине PCI адрес, выровненный по границе двойного слова, передается по линиям AD[31:2]; линии AD[1:0] задают порядок адресов в пакете:

- 00 — линейное инкрементирование; адрес последующей фазы отличается от предыдущего на число байтов шины (4 для 32-битной и 8 для 64-битной шины);

- 10 — сворачивание адресов с учетом длины строки кэш-памяти (Cacheline Wrap mode). В транзакции адрес для очередной фазы увеличивается до достижения границы строки кэша, после чего переходит на начало этой строки и увеличивается до адреса, предшествующего начальному. Если транзакция длиннее строки кэша, то она продолжится в следующей строке с того же смещения, что и началась. Так, при длине строки 16 байт и 32-битной шине транзакция, начавшаяся с адреса xxxxxx08h, будет иметь последующие фазы данных, относящиеся к адресам xxxxxx0Ch, xxxxxx00h, xxxxxx04h; и далее к xxxxxx18h, xxxxxx1Ch, xxxxxx10h, xxxxxx14h. Длина строки кэша прописывается в конфигурационном пространстве устройства. Если устройство не имеет регистра Cache Line Size, то оно должно прекратить транзакцию после первой фазы данных, поскольку порядок чередования адресов оказывается неопределенным;

- 01 и 11 — зарезервированы, могут использоваться как указание на отключение (Disconnect) после первой фазы данных.

Если требуется доступ к адресам свыше 4 Гбайт, то используется двухадресный цикл, передающий младшие 32 бита полного 64-битного адреса для последующей команды, вместе с которой передаются старшие биты адреса. В обычных командах подразумевается нулевое значение бит [63:32] полного адреса.

В PCI-X передается полный адрес памяти — используются все линии AD[31:0]. В пакетных транзакциях адрес определяет точное положение начального байта пакета, и всегда подразумевается линейный нарастающий порядок адресов. В пакетной транзакции участвуют все байты, начиная с данного и до последнего (по счетчику байтов). Запреты отдельных байтов в пакете (как в PCI) для транзакций PCI-X недопустимы. В одиночных транзакциях (DWORD) биты адреса AD[1:0] определяют байты, которые могут быть разрешены сигналами C/BE[3:0]#1: При AD[1:0] = 00 допустимо C/BE[3:0]# = xxxx (могут быть разрешены любые байты), при AD[1:0] = = 01 — C/BE[3:0]# = xxx1, при AD[1:0] = 10 — C/BE[3:0]# = xx11, при AD[1:0] = 11 — — C/BE[3:0]# = x111 (передается лишь байт 3 или ни один байт не разрешен).

«Продвинутый» контроллер прерываний — APIC

Контроллер APIC в первую очередь предназначен для симметричных мультипроцесорных систем (SMP), описанных в документе Intel «MultiProcessor Specification» (MPS), в Сети доступна версия 1.4, 1997 год. Здесь симметрия рассматривается в двух аспектах:

- симметрия памяти — все процессоры пользуются общей памятью, работают с одной копией ОС;

- симметрия ввода/вывода — все процессоры разделяют общие устройства ввода/вывода и общие контроллеры прерываний.

Система может быть симметричной по памяти, но асимметричной по прерываниям от ввода/вывода, если для них используется выделенный процессор. В x86 симметрию по прерываниям обеспечивает APIC. Система с APIC состоит из локальных контроллеров, установленных в процессорах, и контроллеров прерываний от ввода/вывода (одного или нескольких). Все контроллеры APIC соединены между собой локальной шиной, по которой они обмениваются друг с другом сообщениями. Задача каждого локального контроллера (Local APIC) — трансляция сообщений, принятых по локальной шине, в сигналы, вызывающие все аппаратные прерывания своего процессора — маскируемые (INTR), немаскируемые (NMI) и прерывания системного обслуживания (SMI). Кроме того, локальные APIC позволяют каждому процессору генерировать прерывания для других процессоров. Локальный контроллер имеет внутренний интервальный таймер, позволяющий вырабатывать прерывания через программируемый интервал времени. Контроллер прерываний от ввода/вывода (I/O APIC) преобразует запросы аппаратных прерываний от устройств в сообщения протокола локальной шины APIC. В мультипроцессорном режиме он отвечает за распределение прерываний по процессорам, для чего может использоваться статическое или динамическое распределение. В случае статического распределения для каждого номера прерывания указывается номер процессора, который его обслуживает. В случае динамического распределения каждое прерывание направляется наименее приоритетному в данный момент процессору. Этот же контроллер отвечает за распространение сигналов о системных событиях (NMI, INIT, SMI) и межпроцессорных прерываний. Прерывания в мультипроцессорных системах подробно рассмотрены в документе «Intel Architecture Software Developer’s Manual Volume 3: System Programming Guide», доступном на сайте http://www.intel.com. Здесь же ограничимся описаниями возможностей, предоставляемыми для сигнализации прерываний ввода/вывода контроллерами APIC. Контроллер I/O APIC является частью чипсета системной платы, например, он входит в хабы ICH2 и ICH3 чипсетов Intel. В специфкации MPS определено три режима обработки прерываний:

- режим PIC (PIC Mode) — эмуляция пары PIC 8259A с традиционной передачей сигналов прерывания одному процессору (загрузочному, BSP Bootstrap Processor) по линиям INTR и NMI;

- режим «виртуальных проводов» (Virtual Wire Mode) — то же, но с подачей сигналов прерывания по локальной шине APIC. При этом I/O APIC может работать совместно с PIC 8259A, обеспечивая дополнительные возможности (в частности, дополнительные входы запросов прерываний);

- симметричный режим (Symmetric I/O Mode) — сообщения о прерываниях от устройств генерирует APIC; прерывания могут доставляться любому процессору; каждый вход запроса индивидуально программируется с помощью таблицы перенаправления прерываний (I/O Redirection Table).

Первые два режима обеспечивают полную совместимость с системой прерываний PC/AT, с программной точки зрения они эквивалентны, различия лежат в области схемотехники. По аппаратному сбросу (и включении питания) система начинает работать в одном из этих режимов. Когда система подготовится к переходу в MP-режим, APIC переводится в симметричный режим и активизирует таблицу перенаправлений прерываний (предварительно программно инициализированную).

В MP-системе присутствует таблица описаний ее компонентов; к прерываниям в этой таблице относятся описатели всех I/O APIC, а также описатели назначений всех используемых источников прерываний, связанных с I/O APIC и локальными APIC. В описателе назначения для каждого источника прерываний указывается:

- тип прерывания: векторное с передачей вектора через APIC, векторное с внешней передачей вектора (от PIC 8259A), NMI или SMI;

- полярность сигнала и его тип (уровень или перепад);

- идентификатор шины, на которой расположен источник;

- идентификатор запроса на этой шине;

- идентификатор и номер входа APIC, к которому подключен данный запрос.

Согласно MPS, для симметричных систем допустимы векторы в диапазоне 10h — FEh. Уровень приоритета прерывания определяется номером его вектора, деленным на 16. Самый приоритетный уровень — нулевой.

Выделение для сообщений APIC отдельной локальной шины позволяет освободить системную шину процессора от трафика, связанного с обслуживанием прерываний (подачи подтверждений прерываний для получения вектора). В современных процессорах используется локальная шина, состоящая из трех сигнальных линий: PICD[1:0] — двунаправленная шина данных и PICCLK — сигнал синхронизации (тактовая частота). Протокол шины обеспечивает распределенный механизм арбитража: в любой момент времени каждый APIC (локальный и I/O APIC) имеет уникальное значение приоритета арбитража (0–15), которое динамически меняется после успешной передачи сообщения. При попытке одновременного начала передачи сообщения несколькими APIC после фазы арбитража остается единственный победитель. Получатель сообщения подтверждает успешный прием; в случае неудачи сообщение передается повторно (обеспечивается надежная доставка). Сообщения, передаваемые по локальной шине APIC, программно-невидимы; реализация и протокол шины могут быть изменены производителями процессоров и чипсетов системных плат, но это не отразится на ПО.

Контроллер I/O APIC позволяет вырабатывать значительное число запросов прерываний; каждому запросу соответствует свой элемент в таблице перенаправлений, находящейся в APIC. Каждый элемент определяет способ реакции на свой запрос, вектор прерывания и процессор (процессоры) назначения, которые должны его обработать. С запросами связаны индивидуальные входы INTINn; определенный уровень или перепад сигнала на этих входах вызывает соответствующие запросы. Чувствительность и вектор (следовательно, и приоритет) для каждого запроса программируется индивидуально. Более совершенные модели I/O APIC позволяют вызывать прерывание и записью номера входа в регистр контроллера, что, например, используются для поддержки прерываний MSI на шине PCI. При этом возможна и экономия сигнальных входов: APIC может иметь входы INTINn не для всех номеров запросов, посылаемых через запись в этот регистр. Однако число запросов всегда ограничивается размером таблицы перенаправлений. Регистры контроллеров APIC отображаются на пространство памяти. Все локальные контроллеры APIC используют один и тот же диапазон адресов (по умолчанию базовый адрес FEE0 0000h) — к их регистрам обращаются только программы, исполняемые на их же процессорах, и эти обращения не выводятся на системную шину. Контроллеры I/O APIC доступны всем процессорам, по умолчанию базовый адрес первого I/O APIC — FEC0 0000h, базовые адреса остальных контроллеров (если таковые имеются) назначаются последовательно с шагом 1000h. Часть регистров адресуется непосредственно, большая часть регистров, включая и таблицу перенаправлений, адресуется косвенно.

Таблица. Непосредственно адресуемые регистры APIC

| Адрес | Размер, бит | Тип | Назначение |

| FEC0_0000h | 8 | R/W | Index Register, индекс для доступа к косвенно адресуемым регистрам |

| FEC0_0010h | 32 | R/W | Data Register, данные для обращений к косвенно адресуемым регистрам |

| FECO_0020h | 8 | WO | IRQ Pin Assertion Register, регистр программной установки запросов прерываний (запись числа 0–23 эквивалентна подаче сигнала на соответствующий вход INTINn) |

| FECO_0040h | 8 | WO | EOI Register — регистр завершения прерываний для входов, чувствительных к уровню. Запись байта — вектора прерывания — вызывает сброс бита Remote_IRR для всех входов, которым назначен данный вектор (аналогичное действие IOAPIC выполняет по сообщению EOI, полученному по локальной шине) |

Таблица. Косвенно-адресуемые регистры APIC

| Адрес | Размер, бит | Тип | Назначение |

| 00h | 32 | R/W | ID (биты 24:27) — идентификатор (физический номер), программно назначаемый данному APIC. Остальные биты — резерв |

| 01h | 32 | RO | Version — версия (возможности IOAPIC): биты 23:16 — максимальный номер элемента в таблице перенаправления; бит 15 (PRQ) — признак наличия регистра программной установки запросов прерываний; биты 7:0 — номер версии; остальные биты — резерв |

| 02h | 32 | RO | Arbitration ID (биты 24:27) — текущее значение приоритета арбитража. Остальные биты — резерв |

| 03h | 32 | R/W | Boot Configuration — конфигурация: бит 0 — DT (Delivery Type), управление механизмом доставки сообщений: 0 — через локальную шину APIC, 1 — через сообщения по системной шине (режим I/O(x)APIC) |

| 03-0Fh | RO | Резерв | |

| 10-11h | 64 | R/W | Redirection Table 0 — первый элемент таблицы перенаправления |

| ..... | ..... | ..... | ..... |

| 3E-3Fh | 64 | R/W | Redirection Table 23 — последний элемент таблицы перенаправления |

| 40-FFh | RO | Резерв |

Таблица. Формат элемента таблицы перенаправлений

| Биты | Назначение |

| 63:56 | Destination (R/W), идентификатор назначения. Если используется физическая адресация (бит 11 = 0), то биты [59:56] задают идентификатор локального APIC (биты 63:59 должны быть нулевыми). При логической адресации (бит 11 = 1) биты [63:56] задают логический адрес набора процессоров |

| 55:17 | Резерв (нули) |

| 16 | Mask (R/W) — маска запроса: 1 — прерывание замаскировано (но запрос не сбрасывается) |

| 15 | Trigger Mode (R/W) — чувствительность входа: 0 — к перепаду, 1 — к уровню |

| 14 | Remote IRR (R/W), удаленное подтверждение запроса прерывания (только для линий, чувствительных к уровню). Устанавливается, когда локальный APIC принимает этот запрос от IOAPIC; сбрасывается, когда IOAPIC получает команду EOI с соответствующим номером вектора |

| 13 | Interrupt Input Pin Polarity (R/W), полярность сигнала запроса: 0 — активный уровень высокий, 1 — низкий |

| 12 | Delivery Status (RO), состояние доставки: 0 — нет активности, 1 — запрос пришел, но по шине APIC еще не доставлен адресату |

| 11 | Destination Mode (R/W), адресация сообщения: 0 — физическая (по APIC ID), 1 — логическая (по идентификатору набора процессоров) |

| 10:8 | Delivery Mode (R/W) — режим доставки |

| 7:0 | Vector (R/W) — вектор прерывания |

Таблица. Режимы доставки сообщений

| Режим | Описание |

| 000 | Доставка сигнала на входы INTR процессора (или группы) в соответствии с адресатом назначения |

| 001 | Доставка сигнала на вход INTR одного процессора из адресованной группы, выполняющего самую низкоприоритетную задачу. Если несколько процессоров выполняют задачи с одинаково низким приоритетом, сообщение получит тот, чей APIC выиграет в этот момент арбитраж на локальной шине |

| 010 | SMI/PMI (System Management Interrupt, Power Management Interrupt), прерывание системного управления и системы управления энергопотреблением, только для входов, чувствительных к перепаду. Вектор игнорируется (но должен быть нулевым) |

| 011 | Резерв |

| 100 | NMI, немаскируемое прерывание, доставляется на входы NMI всех адресованных процессоров. Должно использоваться для входов, чувствительных к перепаду |

| 101 | INIT, «мягкая» инициализация всех адресованных процессоров. Должна использоваться для входов, чувствительных к перепаду |

| 110 | Резерв |

| 111 | ExtINT, внешнее прерывание, вектор которого доставляется от внешнего контроллера PIC по команде INTA. Доставляется на входы INTR всех адресованных процессоров. Должно использоваться для входов, чувствительных к перепаду |

Кроме использования последовательной локальной шины есть и иной вариант доставки сообщений к локальным APIC, использущий обращения к пространству памяти. Для этого локальные APIC настраиваются на отслеживание операций записи по определенным адресам. Источник сообщений выполняет операцию записи в пространство памяти, в которой и адрес и данные несут информацию о событии прерывания (см. следующую таблицу). В качестве источника сообщений может выступать расширенный контроллер, называемый I/O(x)APIC. Вышеупомянутый хаб ICH3 имеет возможность работы в режиме I/O(x)APIC.

Таблица. Формат сообщения о прерывании, передаваемого по системной шине

| Бит | Назначение |

| Назначение бит адреса | |

| 31:20 | Всегда FEEh |

| 19:12 | Destination ID, идентификатор получателя, аналогично битам 63:56 элемента таблицы перенаправлений |

| 11:4 | Резерв (0) |

| 3 | Redirection Hint, признак перенаправления: 0 — сообщение доставляется агенту (процессору), идентификатор которого указан в битах 19:12; 1 — сообщение доставляется агенту с минимальным приоритетом прерываний |

| 2 | Destination Mode, режим назначения, используется только при единичном признаке перенаправления. Если биты 2 и 3 имеют единичное значение, то сообщение направляется по логическому идентификатору группы процессоров |

| 1:0 | Всегда 00 |

| 31:16 | Всегда 0000 |

| 15 | Trigger Mode, режим чувствительности: 1 — уровень, 0 — перепад |

| 14 | Delivery Status, признак для прерываний по уровню: 1 — установка активного уровня, 0 — снятие (для прерываний по перепаду всегда 1) |

| 13:12 | Всегда 00 |

| 11 | Destination Mode, режим назначения: 1 — логический, 0 — физический |

| 10:8 | Delivery Mode, режим доставки |

| 7:0 | Вектор прерывания |

Еще статьи...

Подкатегории

-

Протокол, команды и транзакции шин PCI и PCI-X

- Кол-во материалов:

- 12

-

Общая информация

- Кол-во материалов:

- 4

-

Электрический интерфейс и конструктивы для шин PCI

- Кол-во материалов:

- 8

-

Конфигурирование и BIOS устройств PCI и PCI-X

- Кол-во материалов:

- 10

-

Мосты PCI и PCI-X

- Кол-во материалов:

- 10

-

Прерывания PCI: INTx#, PME#, MSI и SERR#

- Кол-во материалов:

- 7

На https://isiktimsm.date широкий выбор девушек на любой вкус. https://kuybyshevsm.date обеспечивает конфиденциальность ваших встреч.