Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

https://tentony.ru/pergola.html перголы.

PCI и PCI-X

Конфигурационное пространство обычных устройств (тип 0)

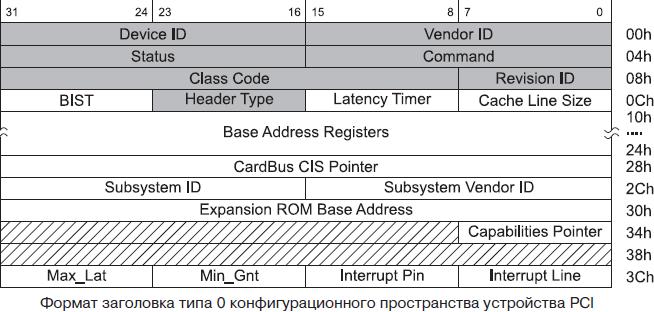

Формат заголовка конфигурационного пространства приведен на рисунке ниже, серым цветом здесь выделены поля, обязательные для всех устройств; регистры, специфичные для устройства, могут занимать адреса конфигурационного пространства в пределах 40–FFh.

Перечисленные ниже поля идентификации допускают только чтение:

- Device ID — идентификатор устройства, назначаемый производителем;

- Vendor ID — идентификатор производителя микросхемы PCI, назначенный PCI SIG. Идентификатор FFFFh является недопустимым; это значение должно возвращаться при чтении конфигурационного пространства несуществующего устройства;

- Revision ID — версия продукта, назначенная производителем. Используется как расширение поля Device ID;

- Header Type — тип заголовка (биты [6:0]), определяющий формат ячеек в диапазоне 10–3Fh и несущий признак многофункционального устройства (если бит 7 установлен). На рисунке приведен формат заголовка типа 0, относящийся именно к устройствам PCI. Тип 01 относится к мостам PCI-PCI; тип 02 относится к мостам для CardBus;

- Class Code — код класса, определяющий основную функцию устройства, а иногда и его программный интерфейс (см. далее). Старший байт (адрес 0Bh) определяет базовый класс, средний — подкласс, младший — программный интерфейс (если он стандартизован).

Остальные поля заголовка являются регистрами устройств, допускающими как запись, так и чтение.

Регистр команд Command (RW) служит для управления поведением устройства на шине PCI. Регистр допускает как запись, так и чтение. После аппаратного сброса все биты регистра (кроме специально оговоренных исключений) обнулены.

Назначение бит регистра команд:

- бит 0 — IO Space — разрешение ответа на обращения к пространству вводавывода;

- бит 1 — Memory Space — разрешение ответа на обращения к пространству памяти;

- бит 2 — Bus Master — разрешение работы инициатором (в режиме прямого управления шиной); игнорируется в PCI-X при завершениях расщепленных транзакций;

- бит 3 — Special Cycles — разрешение реакции на специальные циклы;

- бит 4 — Memory Write& and Invalidate enable — разрешение использовать команды «запись с инвалидацией» при работе инициатором (если бит обнулен, то вместо этих команд должна использоваться обычная запись в память); игнорируется в PCI-X;

- бит 5 — VGA palette snoop — разрешение слежения за записью в регистр палитр;

- бит 6 — Parity Error Response — разрешение нормальной реакции (вырабатывать сигнал PERR#) на обнаруженную ошибку четности или ECC. Если бит обнулен, то устройство должно только фиксировать ошибку в регистре состояния и продолжать выполнение транзакции; при ECC-контроле данные об ошибке записываются в регистры ECC;

- бит 7 — Stepping Control — возможность пошагового переключения (address/data stepping) линий (если устройство никогда этого не делает, бит регистра «запаян» в «0», если делает всегда — в «1», устройство с такой возможностью по сбросу устанавливает этот бит в «1»). В версии 2.3 и PCI-X бит освобожден (в связи с отменой степинга);

- бит 8 — SERR# Enable — разрешение генерации сигнала ошибки SERR# (ошибка адреса сообщается, когда этот бит и бит 6 установлены);

- бит 9 — Fast Back-to-Back Enable (необязательный, игнорируется в PCI-X) — разрешение ведущему устройству использовать быстрые смежные обращения к разным устройствам (если бит обнулен, быстрые обращения допустимы лишь для транзакций с одним агентом);

- бит 10 Interrupt Disable —, запрет генерации сигнала прерываний по линиям INTx (по аппаратному сбросу и включению питания бит обнулен — прерывания разрешены). Бит определен начиная с PCI 2.3. Ранее был резервным;

- биты [11:15] — резерв.

Регистр Status служит для определения состояния и свойств устройства. Биты, помеченные как RO, допускают только считывание. Другие биты регистра могут быть программно модифицированы операцией записи, с помощью которой можно только обнулять биты, но не устанавливать. При записи в позиции обнуляемых бит устанавливаются единичные значения. Назначение бит регистра состояния:

- биты [0:2] — резерв;

- бит 3— Interrupt Status (RO), наличие запроса прерывания. Устанавливается в единицу перед подачей сигнала по линии INTx, независимо от значения бита Interrupt Disable. С прерываниями MSI не связан. Бит определен начиная с PCI 2.3, ранее был резервным. В PCI-X 2.0 бит обязателен;

- бит 4 — Capability List (RO, необязательный) — признак наличия указателя новых возможностей в регистре со смещением 34h;

- бит 5 — 66 MHz Capable (RO, необязательный) — признак поддержки частоты 66 МГц;

- бит 6 — резерв;

- бит 7 — Fast Back-to-Back Capable (RO, необязательный) — признак поддержки быстрых смежных транзакций (fast back-to-back) с разными устройствами;

- бит 8 — Master Data Parity Error (только для устройств с прямым управлением) — инициатор (запросчик) транзакции обнаружил неисправимую ошибку данных;

- биты [10:9] — DEVSEL Timing — скорость выборки: 00 — быстрая, 01 — средняя, 10 — низкая (определяет самую медленную реакцию DEVSEL# на все команды, кроме Configuration Read и Configuration Write);

- бит 11 — Signaled Target Abort — устанавливается целевым устройством, когда оно отвергает транзакцию;

- бит 12 — Received Target Abort — устанавливается инициатором, когда он обнаруживает отвергнутую транзакцию;

- бит 13 — Received Master Abort — устанавливается ведущим устройством, когда оно отвергает транзакцию (кроме специального цикла);

- бит 14 — Signaled System Error — устанавливается устройством, подавшим сигнал SERR#;

- бит 15 — Detected Parity Error — устанавливается устройством, обнаружившим ошибку данных.

Регистр Cache Line Size (RW) служит для задания размера строки кэша (0–128, допустимые значения 2n, иные трактуются как 0). По этому параметру инициатор определяет, какой командой чтения воспользоваться (обычное чтение, чтение строки или множественное чтение). Ведомое устройство использует этот параметр для поддержки пересечения границ строк при пакетных обращениях к памяти. По сбросу регистр обнуляется.

Регистр Latency Timer (RW) задает значение таймера, ограничивающего длину транзакции при снятии сигнала GNT# (см. главу 2). Значение указывается в виде числа тактов шины, часть битов может не допускать изменения (обычно младшие три бита неизменны, так что таймер программируется с дискретностью в 8 тактов).

Регистр BIST (RW) служит для управления встроенным самотестированием (BuiltIn Self Test). Назначение бит регистра:

- бит 7 — возможность BIST;

- бит 6 — запуск теста: запись единицы инициирует тест, по окончании устройство сбрасывает бит (тест должен быть завершен не более чем за 2 с);

- биты [5:4] — резерв (0);

- биты [3:0] — код завершения теста: 0 — тест прошел успешно.

Регистр Card Bus CIS Pointer (необязательный) содержит указатель на структуру описателя Card Bus для комбинированного устройства PCI + Card Bus.

Регистр Interrupt Line (RW) хранит номер входа контроллера прерывания для используемой линии запроса (0–15 — IRQ0–IRQ15, в системах с APIC может иметь и большее значение; 255 — неизвестный вход или не используется).

Регистр Interrupt Pin (RO) задает линию, используемую для запроса прерывания: 0 — не используется, 1 — INTA#, 2 — INTB#, 3 — INTC#, 4 — INTD#, 5–FFh — резерв.

Регистр Min_GNT (RO) задает минимальное время, на которое ведущему устройству должно предоставляться управление шиной из расчета на частоту 33 МГц, в интервалах по 0,25 мкс.

Регистр Max_Lat (RO) задает максимально допустимую задержку предоставления ведущему устройству доступа к шине, в интервалах по 0,25 мкс (0 — нет специальных требований).

Регистры Subsystem ID (RO, задается производителем) и Subsystem Vendor ID (RO, производитель получает в PCI SIG) хранят идентификаторы, позволяющие точно идентифицировать карты и устройства (в системе могут быть установлены несколько карт с совпадающими идентификаторами устройства и производителя Device ID и Vendor ID). В поле 2Ch ставится идентификатор производителя карты PCI (может совпадать со значением в поле 0, если фирма выпускает и микросхемы, и карты).

Регистр Capability Pointer (CAP_PTR) содержит указатель на цепочку блоков регистров свойств функции, представленных в конфигурационных регистрах. Каждый блок представляет собой набор регистров, начинающийся с границы двойного слова (в указателе биты [1:0] сброшены). Каждый блок начинается с байта идентификатора типа свойства (CAP_ID, определенный PCI SIG), за которым следует указатель на следующий блок (нулевой указатель является признаком конца списка блоков), после чего расположены байты описаний самих свойств. Через CAP_PTR, например, отыскиваются регистры управления энергопотреблением (если есть), регистры AGP, некоторые регистры хост-контроллера USB 2.0 и ряд других.

Регистры Base Address Registers (BAR) описывают области памяти и портов ввода-вывода. Программными манипуляциями с регистрами можно определить размеры областей. Для областей памяти и портов описания различаются:

- область памяти (размером не более 2 Гбайт) описывается следующим образом:

---бит 0 = 0 — признак памяти;

---биты [2:1] — тип адресации: 00 — 32-битная адресация, 10 — 64-битная (в этом

случае регистр расширяется следующим за ним 4-байтным словом, 64-битная адресация обязательна для PCI-X), 01 и 11 — резерв (01 в прежних версиях предназначались для памяти в пределах первого мегабайта);

---бит 3 (Prefetchable) — признак «настоящей» памяти, то есть допускающей предвыборку;

---биты [31:4] — базовый адрес памяти; - область портов (размером до 256 байт) описывается следующим образом:

---бит 0 = 1 — признак области портов;

---бит 1 = 0 (резерв);

---биты [31:2] — базовый адрес блока портов.

Регистр Expansion ROM Base Address управляет адресацией ПЗУ программной поддержки устройства. Размер ПЗУ определяется так же, как и в регистрах базовых адресов (см. выше). Обращение к ПЗУ возможно лишь при разрешенном использовании памяти (бит 1 в регистре команд). Назначение бит регистра:

- бит 0 — разрешение использования ПЗУ;

- биты [1:10] — резерв;

- биты [11:31] — базовый адрес.