Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

Читайте реальные тинькофф страхование осаго отзывы и узнайте больше о плюсах и минусах.

Процессор

Процессор

Процессор — аппаратный уровень. Операционные устройства

- Подробности

- Родительская категория: Процессор

- Категория: Процессор — аппаратный уровень.

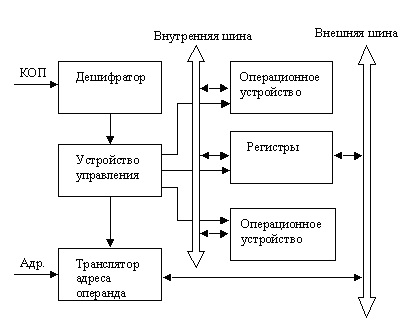

Процессор — это ядро и мотор компьютера, обеспечивает как выполнение операций, так и функционирование всех узлов. Обычно простой процессор включает в себя декодер команд, арифметико-логическое устройство (АЛУ), регистры, транслятор адресов операндов и устройство управления. Отдельные элементы связаны внутренней шиной. Связь с внешними устройствами осуществляется через внешнюю шину.

Структура процессора

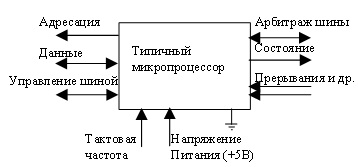

Все перечисленные элементы могут помещаться в одной микросхеме — микропроцессоре. Они доступны через выводы микросхемы при выполнении команд, загружаемых из ОЗУ. На следующем рисунке показаны выводы типичного микропроцессора. Рассмотрим как работает процессор изнутри, на аппаратном и микропрограммном уровне. Далее будет представлено рассмотрение конкретного процессора i8086.

Типичный процессор

Аппаратный уровень процессора в настоящее время не является ни программно доступным, ни даже наблюдаемым, однако представление о нем помогает пониманию таких вопросов, как скорость выполнения команд, возможность конвейеризации и т.д.

Для того чтобы понять как выполняются команды в процессоре рассмотрим работу операционных устройств. В машине фон Неймана в качестве операционного устройства применяется АЛУ. Учитывая разнообразие выполняемых операций и обрабатываемых данных, можно говорить не об одном устройстве, а о целом комплексе специализированных операционных устройств, каждое из которых выполняет свое подмножество операций (команд). Следует выделить операционные устройства:

- целочисленной арифметики;

- логических операций;

- десятичной арифметики;

- чисел с плавающей запятой.

Кроме указанных устройств процессоры в зависимости от их назначения могут иметь и другие операционные устройства: управления потреблением, графических операций, упаковки/распаковки изображений и др. В минимальном варианте операционное устройство целочисленной арифметики (АЛУ) должно содержать аппаратуру для реализации лишь основных логических операций, сдвигов, инвертирования, а также сложения чисел в формате с фиксированной запятой. Опираясь на этот набор, можно программным способом обеспечить выполнение остальных арифметических и логических операций как для чисел с фиксированной запятой, так и для других форм представления информации. Следует отметить, что подобный вариант не позволяет добиться высокой скорости вычислений, поэтому по мере расширения технологических возможностей доля аппаратных средств в составе АЛУ постоянно возрастает. Набор элементов, на основе которых строятся структуры различных операционных устройств, называется структурным базисом. Структурный базис операционных устройств включает в себя:

- регистры, обеспечивающие хранение слов данных;

- шины, связывающие регистры и предназначенные для передачи слов данных;

- комбинационные схемы, реализующие вычисления по управляющим сигналам от устройства управления.

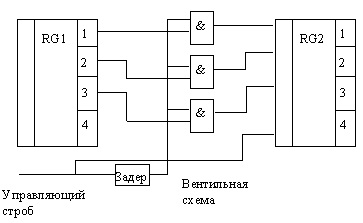

Выполнение команды может быть сведено к нескольким (одновременно или последовательно во времени) операциям пересылки из регистра в регистр(на рисунке). Возможно с промежуточным преобразованием пересылаемых двоичных слов на комбинационных логических схемах. В следующей теме подробно рассмотрим регистры.

Регистры операционного устройства

Устройство управления. Микропрограммный автомат

- Подробности

- Родительская категория: Процессор

- Категория: Устройство управления. Микропрограммный автомат

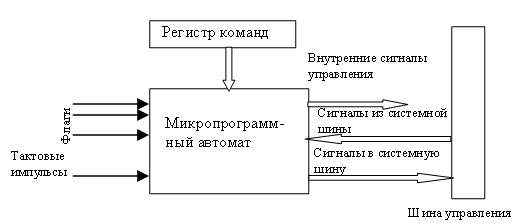

Устройство управления (УУ) ЭВМ реализует функции управления ходом вычислительного процесса, обеспечивая автоматическое выполнение команд программы (см. рисунок). Входной информацией для УУ служат:

- тактовые импульсы — с каждым импульсом УУ выполняет одну или несколько микроопераций;

- код операции — поступает из регистра команды и используется, чтобы определить, какие микроопераций должны выполняться;

- флаги — требуются для оценки состояния процессора, что необходимо для выполнения команд условного перехода;

- сигналы из системной шины — обслуживание прерывания, прямого доступа в память. В свою очередь УУ, а точнее микропрограммный автомат, формирует следующую выходную информацию:

- внутренние сигналы управления — перемещают операнды из регистра в регистр и инициируют работу операционных устройств;

- сигналы в системную шину — управляющие сигналы в память или в устройства ввода-вывода.

Модель устройства управления

Как отмечалось, процесс функционирования ЭВМ состоит из последовательности элементарных действий в ее узлах. Такие элементарные действия, выполняемые в течение одного такта сигналовсинхронизации, называются микрооперациями. Совокупность одновременно выполняемых микроопераций образует микрокоманду.

Последовательность микрокоманд, определяющая порядок реализации машинного цикла, составляет микропрограмму. Микропрограммный автомат определяет микропрограмму как последовательность выполнения микроопераций. В общей структуре УУ можно выделить две части: управляющую и адресную. Управляющая часть предназначена для координирования работы операционного блока, адресной части, основной памяти и др. Адресная часть обеспечивает формирование адресов команд и адресов операндов в основной памяти. Состав управляющей части: регистр команды, микропрограммный автомат, узел прерываний и приоритетов. Микропрограммный автомат на основе декодирования команды вырабатывает определенную последовательность микрокоманд. В зависимости от способа формирования микрокоманд различают микропрограммные автоматы с жесткой и программируемой логикой. Адресная часть УУ включает в себя: операционный узел устройства управления (ОПУУ), регистр адреса, счетчик команд. Регистр адреса используется для хранения исполнительных адресов операндов, а счетчик команд — для выработки и хранения адресов команд. Их содержимое посылаются в регистр адреса основной памяти. ОПУУ обрабатывает адресные части команд, формируя исполнительные адреса операндов, а также подготавливает адрес следующей команды при выполнении команд перехода. Иногда ОПУУ совмещают с основным операционным устройством. Ниже будет рассмотрена схема ОПУУ процессора i8086.

Конвейер команд. Конвейеризация — способ обеспечения параллельности выполнения команд

- Подробности

- Родительская категория: Процессор

- Категория: Конвейер команд

Первым шагом на пути обеспечения параллельности уровня команд явилось создание конвейера команд. Идея конвейера команд была предложена в 1956 году С.А. Лебедевым. Команда подразделяется на несколько этапов, каждый из которых выполняется своей частью аппаратуры, причем, эти части могут работать параллельно. Если на выполнение каждого этапа расходуется одинаковое время (один такт), то на выходе процессора в каждый такт появляется результат очередной команды. Производительность при этом возрастает благодаря тому, что одновременно на различных ступенях конвейера выполняется несколько команд. Конвейерная обработка такого рода широко применяется во всех современных быстродействующих процессорах. Количество этапов, на которые конструкторы разбивают выполнение процессорной команды, может быть различным (в разных моделях процессоров х86 колеблется от 2 i8088 до 20 Pentium IV).

Конвейеризация — способ обеспечения параллельности выполнения команд

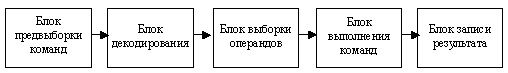

Выполнение типичной команды можно разделить на следующие этапы:

- выборка команды — IF (по адресу, заданному счетчиком команд, из памяти извлекается команда);

- декодирование команды / выборка операндов из регистров — ID;

- выполнение операции / вычисление эффективного адреса памяти — EX;

- обращение к памяти — MEM;

- запоминание результата — WB.

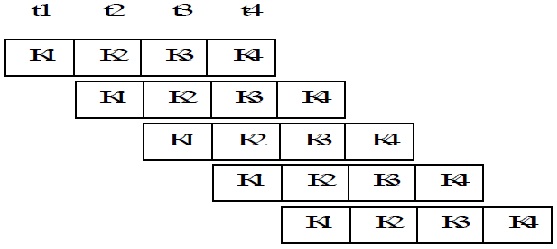

В зависимости от типа команды и способа адресации, время выполнения команды сильно варьируется. Дольше всего выполняются этапы, связанные с обращением к памяти. На рисунках показаны блоки и конвейер команд гипотетического процессора, имеющего пять блоков исполнения команд и соответственно пять этапов (ступеней). Изображены выполняемые команды, номера тактов и этапы выполнения команд. На первом такте считывается первая команда. На втором, пока декодируется первая команда, считывается вторая. На пятом такте в процессоре одновременно находятся пять команд, каждая в своем узле.

Блоки прохождения команды в процессоре

Пятиступенчатая схема конвейера

Конвейеризация увеличивает пропускную способность процессора (количество команд, завершающихся в единицу времени), но она не сокращает время выполнения отдельной команды. Имеются некоторые накладные расходы на конвейеризацию, возникающие в результате несбалансированности задержки на каждой его ступени. Частота синхронизации (такт синхронизации) не может быть выше, чем время, необходимое для работы наиболее медленной ступени конвейера. Конвейер не всегда представляет собой линейную цепочку этапов. В ряде ситуаций оказывается выгодным, когда функциональные блоки соединены между собой не последовательно, а в соответствии с логикой обработки. Отдельные блоки в цепочке могут пропускаться, а другие — образовывать циклические процедуры. Это позволяет с помощью одного конвейера вычислять более одной функции.

Поток команд — естественная последовательность команд, проходящая по конвейеру процессора. Процессор может поддерживать несколько потоков команд (суперпроцессоры 5 и 6 поколения), если для каждого потока и каждого этапа есть исполнительные элементы.

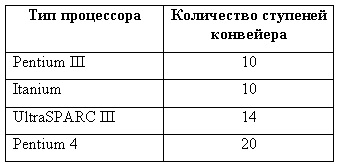

Суперконвейер команд — разбиение каждой ступени на подступени при одновременном увеличении тактовой частоты внутри конвейера; включение в состав процессора многих конвейеров, работающих с перекрытием. Дробление ступеней позволяет поднять тактовые частоты процессора. К суперконвейерным относятся процессоры, в которых число ступеней больше шести (см. таблицу).

Суперконвейер

Cуперконвейер ведет не только к увеличению скорости вычислений, но и к возникновению дополнительных сложностей. Возрастает вероятность конфликтов. Дороже встает ошибка предсказания перехода — приходится сбрасывать весь длинный конвейер, на что требуется дополнительное время. Усложняется логика взаимодействия ступеней. Однако за счет использования новых архитектур удается справиться с большинством проблем. При рассмотрении современных процессоров будут описаны новые идеи: исполнения команд с изменением последовательности, переименования регистров, спекулятивного исполнения и другие.

Способы адресации. Функции способов адресации (и механизма трансляции адреса)

- Подробности

- Родительская категория: Процессор

- Категория: Способы адресации

Способы адресации

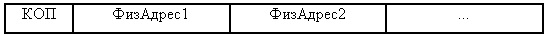

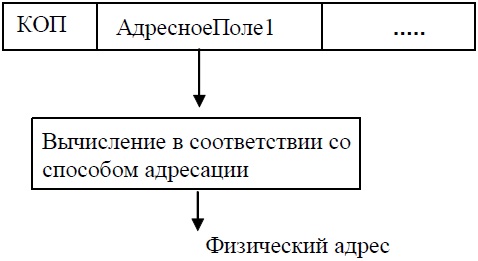

Простейшая структура адресной части команды:

Адресные поля содержат физические адреса.

1) Для ЭВМ 1 — .2 поколений были характерны небольшой обьем ОЗУ (4...32 Кслов) и значительная длина машинного слова (40...64 и более бит). Длина слова выбиралась обычно достаточной для представления числа с инженерной точностью в плавающем формате. При этом в поле адреса мог поместиться полный физический адрес (для маленького объема ОЗУ он был коротким).

2) В ходе развития ЭВМ

•увеличивался обьем ОЗУ, а, следовательно, и длина требуемого физического адреса;

•желательно было вычислять / модифицировать адреса. Это давало возможность одному участку программы обрабатывать данные, расположенные в разных адресах.

Перешли к следующей структуре (см. рисунок ниже):

Двухуровневая схема трансляции адреса

Простейший вариант: физический адрес содержится в адресном регистре, а адресное поле содержит имя (код, номер) адресного регистра плюс код, обозначающий способ адресации (в данном случае косвенно-регистровую адресацию — см. далее). Длина такого поля адреса, могла быть гораздо меньше длины адреса. Например, если процессор содержит восемь регистров общего назначения и использует не более 8 разных способов адресации, длина номера регистра = 3 бита, длина кода способа адресации — также 3 бита. Адресное поле в команде будет содержать всего 6 бит.

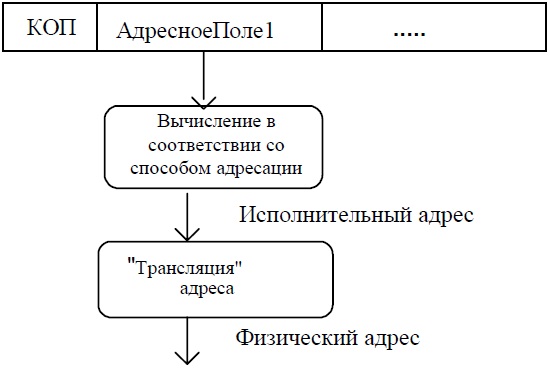

3) При дальнейшем развитии ЭВМ — увеличивается размер адресного пространства.

При 32-разрядном адресе размер адресного пространства = 4 ГБайт. В то же время реальный обьем ОЗУ составляет 16...128 МБайт (длина физического адреса: 24...27 разрядов). Таким образом, имеет место несовпадение диапазона логических адресов (в частности, тех чисел, которые могут храниться в адресных регистрах процессора) и диапазона физических адресов, нумерующих реально существующие ячейки ОЗУ. Поэтому все более широко используется следующая схема преобразования адресов (см. следующий рисунок):

Трехуровневая схема трансляции адреса

В результате вычисления в соответствии со способом адресации формируется объект, называемый исполнительным (executive) или эффективным (так переводят английский термин effective, хотя более правильным является перевод “исполнительный” или “действующий” адрес). Это понятие уровня языка ассемблера почти эквивалентно используемому в языках высокого уровня понятию указатель(pointer). Все перечисленные в данном абзаце понятия — прежде всего суть понятия логические (логические адреса).

Логические адреса требуется отображать на физические адреса фактически имеющейся памяти. В простейшем случае можно это делать "один в один", начиная (размещая, загружая) всю программу целиком в определенное место памяти. В то же время, как увидим далее, такое взаимно-однозначное отображение адресов не всегда удобно, а иногда даже и невозможно.

Понятие "Способ адресации" включает:

•1)Способ кодирования адреса в адресном поле команды;

•2)Условное обозначение (синтаксис) способа адресации при записи команды на языке ассемблера;

•3)Алгоритм вычисления исполнительного адреса по информации, содержащейся в адресном поле, а также в других элементах процессора, имеющих отношение к вычислению адреса (хранящих адресную информацию, компоненты адреса).

Функции способов адресации (и механизма трансляции адреса)

1. Обеспечить удобство вычисления логических адресов при отображении на память компонентов сложных структур данных (массив, структура и поля ее записей, список и т.п.) Это одно из свойств, которые обычно имеют в виду, когда говорят, что "микропроцессор оснащен средствами для программирования на языках высокого уровня".

2. Обеспечить переход от содержимого адресного поля команды к логическому адресу и отображение пространства логических адресов на пространство физических адресов.

3. Обеспечить перемещаемость программных модулей (для легкости компоновки из этих модулей большой программы) или обеспечения позиционной независимости программы.

Под термином "перемещаемость" могут иметь в виду одно из двух различных свойств программы. Статическая перемещаемостьсостоит в том, что оттранслированную программу можно, без модификации адресных частей команд, загружать, начиная с различных адресов, при этом программа сохраняет работоспособность. Динамическая перемещаемость — более сильное свойство, состоящее в том, что загруженную и выполняющуюся программу можно в любой точке остановить, переместить, как единое целое, в другое место памяти и затем успешно продолжить выполнение с точки останова.

4. Для настройки на реально существующую в системе физическую память.

5. Обеспечить возможность многозадачного режима работы, когда в памяти одновременно находятся и выполняются несколько программ: надо разрешить этим программам обмениваться информацией, но защитить их друг от друга (чтобы одна программа не имела возможности испортить другую).

Что такое "многозадачность"?

В простейшем случае есть две задачи: программа пользователя ПрП и операционная система ОС. ПрП не должна иметь возможности испортить ОС.

Другой пример: кроме ОС, две ПрП, из которых одна работает в фоновом режиме. Например, основная задача — текстовый процессор, с которым работает человек, редактируя текст. В паузах, когда человек думает, какую клавишу нажать, работает фоновая задача, например, распечатывается на принтере другой текст. Еще более сложный случай — многопользовательская система, когда на одном процессоре работает несколько пользователей одновременно, они разделяют процессорное время, пространства памяти и другие ресурсы. Механизм трансляции адреса позволяет отображать логические адреса программ, выполняемых на вычислительной системе именно в тот диапазон физических адресов, который соответствует реально установленной памяти.

Архитектуры системы команд

- Подробности

- Родительская категория: Процессор

- Категория: Архитектуры системы команд

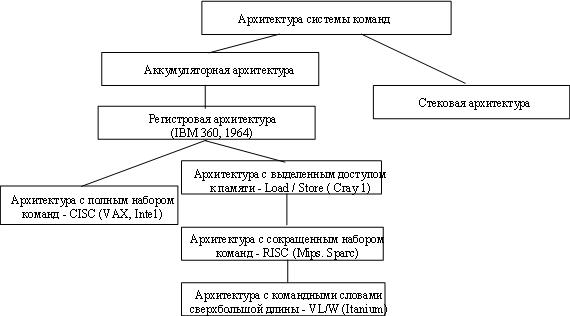

С развитием вычислительной техники появлялись различные архитектуры системы команд (АСК), некоторые из них становились основными на каком-то этапе. Сложившуюся на настоящий момент ситуацию в области архитектуры команд иллюстрирует рисунок.

При анализе/выборе архитектуры команд существенны два момента. Первый — это состав операций, выполняемых вычислительной машиной, и их сложность. Второй — место хранения операндов, что влияет на количество и длину адресов в адресной части команды.

Современная технология программирования ориентирована на языки высокого уровня (ЯВУ), главная цель которых — облегчить процесс программирования. Переход к ЯВУ, однако, породил серьезную проблему: сложные операторы, характерные для ЯВУ, существенно отличаются от простых машинных операций, реализуемых в большинстве вычислительных машин. Проблема получила название семантическою разрыва, а ее следствием становится недостаточно эффективное выполнение программ на ЭВМ. Пытаясь преодолеть семантический разрыв, разработчики вычислительных машин в настоящее время выбирают один из трех подходов и, соответственно, один из трех типов АСК:

- архитектуру с полным набором команд: CISC (Complex Instruction Set Соmputer);

- архитектуру с сокращенным набором команд: RISC (Reduced Instruction Set Compllter);

- архитектуру с командными словами сверхбольшой длины: VLIW (Vегу Long Instruction Word)

В вычислительных машинах типа CISC проблема семантического разрыва решается за счет расширения системы команд, дополнения ее сложными командами, семантически аналогичными операторам ЯВУ.

Основоположником СISС-архитектуры считается компания IBM, которая начала применять данный подход с семейства машин IBM 360 и продолжает его в своих мощных современных универсальных ЭВМ, таких, как IBM ES/9000. Аналогичный подход характерен и для компании Intel в ее микропроцессорах серии 8086 и Pentium. Эта архитектура является практическим стандартом для рынка микрокомпьютеров.

Для СISС-архитектуры типичны:

- наличие в процессоре сравнительно небольшого числа регистров общего назначения;

- большое количество машинных команд, некоторые из них аппаратно реализуют сложные операторы ЯВУ;

- широкое использование микропрограммирования;

- разнообразие способов адресации операндов;

- разная временная структура выполнения команд;

- множество форматов команд различной разрядности (Pentium — длина команды 1-10 байт);

- преобладание двухадресного формата команд;

- наличие команд, где обработка совмещается с обращением к памяти.

Рассмотренный способ решения проблемы семантического разрыва вместе с тем ведет к усложнению аппаратуры ЭВМ, главным образом, устройства управления, что, в свою очередь, негативно сказывается на производительности ЭВМ в целом. Это заставило более внимательно проанализировать программы, получаемые после компиляции с ЯВУ. Был предпринят комплекс исследований, в результате которых обнаружилось, что доля дополнительных команд, эквивалентных операторам ЯВУ, в общем объеме программ не превышает 10-20%, а для некоторых наиболее сложных команд даже 0,2%. В то же время объем аппаратных средств, требуемых для реализации дополнительных команд, возрастает весьма существенно. Так, емкость микропрограммной памяти при поддержании сложных команд может увеличиваться на 60%.

Детальный анализ результатов упомянутых исследований привел к появлению RISC-архитектуры. Термин RISC впервые был использован Д. Паттерсоном и Д. Дитцелем в 1980 году. Идея заключается в ограничении списка команд ЭВМ наиболее часто используемыми простейшими командами, оперирующими данными, размещенными только в регистрах процессорах. Сложные команды ЯВУ выполняются набором простых, число которых больше чем в СISC, но время их выполнения меньше.

Основные особенности RISC-архитектуры:

- небольшое число команд с простым декодированием;

- резко уменьшено количество форматов команд;

- почти все команды выполняются за один такт;

- ограничено количество способов адресации;

- длинный регистровый файл, что позволяет большему объему данных храниться в регистрах на процессорном кристалле большее время и упрощает работу компилятора по распределению регистров под переменные;

- обращение к памяти допускается лишь с помощью специальных команд чтения и записи;

- используются трехадресные команды, что помимо упрощения дешифрации дает возможность сохранять большее число переменных в регистрах без их последующей перезагрузки

- эффективно загружен конвейер команд.

Элементы RISС-архитектуры впервые появились в вычислительных машинах CDC 6600 и супер-ЭВМ компании Сгау Research. Однако окончательно понятие RISC в современном его понимании сформировалось на базе трех исследовательских проектов компьютеров: процессора 801 компании IBM, процессора RISC университета Беркли и процессора MIPS Стенфордского университета.

Разработка экспериментального проекта компании IBM началась еще в конце 70-х годов, но его результаты никогда не публиковались и компьютер на его основе в промышленных масштабах не изготавливался. В 1980 году Д.Паттерсон со своими коллегами из Беркли начали свой проект и изготовили две машины, которые получили названия RISC-I и RISC-II. Главными идеями этих машин было отделение медленной памяти от высокоскоростных регистров и использование регистровых окон. В 1981году Дж.Хеннесси со своими коллегами опубликовал описание стенфордской машины MIPS, основным аспектом разработки которой была эффективная реализация конвейерной обработки посредством тщательного планирования компилятором его загрузки.

Достаточно успешно реализуется RISС-архитектура и в современных ВМ, например в процессорах Alpha серии РА фирмы Hewlett-Packard, семействе PowerPC и т. п. Отметим, что в последних микропроцессорах фирмы Intel и AMD широко используются идеи, свойственные RISС- архитектуре, так что многие различия между CISC и RISC постепенно стираются.

Концепция архитектуры команд cо словами сверхбольшой длины (VLIW) базируется на RISС-архитектуре, где несколько простых RISC- команд объединяются в одну сверхдлинную команду и выполняются параллельно. См. процессоры Itanium, Transmeta.

Важную роль в выборе АСК играет ответ на вопрос о том, где могут храниться операнды и каким образом к ним осуществляется доступ. С этих позиций различают следующие виды архитектур системы команд:

- стековую;

- аккумуляторную;

- регистровую;

- с выделенным доступом к памяти.

Еще статьи...

Подкатегории

-

Кодирование команд в процессоре х86

- Кол-во материалов:

- 2

-

Управление вычислительным процессом

- Кол-во материалов:

- 8

-

Способы адресации

- Кол-во материалов:

- 2

-

Система команд процессора

- Кол-во материалов:

- 6

-

Архитектуры системы команд

- Кол-во материалов:

- 5

-

Конвейер команд

- Кол-во материалов:

- 1

-

Устройство управления. Микропрограммный автомат

- Кол-во материалов:

- 2

-

Процессор — аппаратный уровень.

- Кол-во материалов:

- 4