Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

В Нижнем Новгороде лупа измерительная ЛИ 3 10х представлена у компании "Рентгенсервис".

Процессор

Архитектуры системы команд

Архитектуры системы команд

- Подробности

- Родительская категория: Процессор

- Категория: Архитектуры системы команд

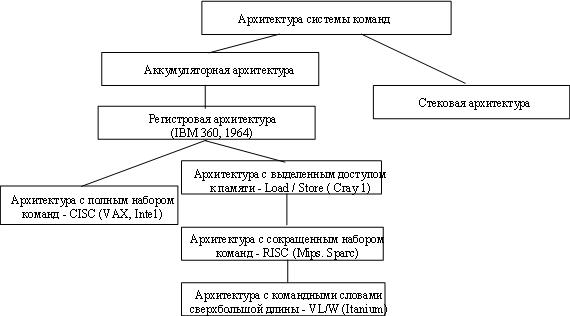

С развитием вычислительной техники появлялись различные архитектуры системы команд (АСК), некоторые из них становились основными на каком-то этапе. Сложившуюся на настоящий момент ситуацию в области архитектуры команд иллюстрирует рисунок.

При анализе/выборе архитектуры команд существенны два момента. Первый — это состав операций, выполняемых вычислительной машиной, и их сложность. Второй — место хранения операндов, что влияет на количество и длину адресов в адресной части команды.

Современная технология программирования ориентирована на языки высокого уровня (ЯВУ), главная цель которых — облегчить процесс программирования. Переход к ЯВУ, однако, породил серьезную проблему: сложные операторы, характерные для ЯВУ, существенно отличаются от простых машинных операций, реализуемых в большинстве вычислительных машин. Проблема получила название семантическою разрыва, а ее следствием становится недостаточно эффективное выполнение программ на ЭВМ. Пытаясь преодолеть семантический разрыв, разработчики вычислительных машин в настоящее время выбирают один из трех подходов и, соответственно, один из трех типов АСК:

- архитектуру с полным набором команд: CISC (Complex Instruction Set Соmputer);

- архитектуру с сокращенным набором команд: RISC (Reduced Instruction Set Compllter);

- архитектуру с командными словами сверхбольшой длины: VLIW (Vегу Long Instruction Word)

В вычислительных машинах типа CISC проблема семантического разрыва решается за счет расширения системы команд, дополнения ее сложными командами, семантически аналогичными операторам ЯВУ.

Основоположником СISС-архитектуры считается компания IBM, которая начала применять данный подход с семейства машин IBM 360 и продолжает его в своих мощных современных универсальных ЭВМ, таких, как IBM ES/9000. Аналогичный подход характерен и для компании Intel в ее микропроцессорах серии 8086 и Pentium. Эта архитектура является практическим стандартом для рынка микрокомпьютеров.

Для СISС-архитектуры типичны:

- наличие в процессоре сравнительно небольшого числа регистров общего назначения;

- большое количество машинных команд, некоторые из них аппаратно реализуют сложные операторы ЯВУ;

- широкое использование микропрограммирования;

- разнообразие способов адресации операндов;

- разная временная структура выполнения команд;

- множество форматов команд различной разрядности (Pentium — длина команды 1-10 байт);

- преобладание двухадресного формата команд;

- наличие команд, где обработка совмещается с обращением к памяти.

Рассмотренный способ решения проблемы семантического разрыва вместе с тем ведет к усложнению аппаратуры ЭВМ, главным образом, устройства управления, что, в свою очередь, негативно сказывается на производительности ЭВМ в целом. Это заставило более внимательно проанализировать программы, получаемые после компиляции с ЯВУ. Был предпринят комплекс исследований, в результате которых обнаружилось, что доля дополнительных команд, эквивалентных операторам ЯВУ, в общем объеме программ не превышает 10-20%, а для некоторых наиболее сложных команд даже 0,2%. В то же время объем аппаратных средств, требуемых для реализации дополнительных команд, возрастает весьма существенно. Так, емкость микропрограммной памяти при поддержании сложных команд может увеличиваться на 60%.

Детальный анализ результатов упомянутых исследований привел к появлению RISC-архитектуры. Термин RISC впервые был использован Д. Паттерсоном и Д. Дитцелем в 1980 году. Идея заключается в ограничении списка команд ЭВМ наиболее часто используемыми простейшими командами, оперирующими данными, размещенными только в регистрах процессорах. Сложные команды ЯВУ выполняются набором простых, число которых больше чем в СISC, но время их выполнения меньше.

Основные особенности RISC-архитектуры:

- небольшое число команд с простым декодированием;

- резко уменьшено количество форматов команд;

- почти все команды выполняются за один такт;

- ограничено количество способов адресации;

- длинный регистровый файл, что позволяет большему объему данных храниться в регистрах на процессорном кристалле большее время и упрощает работу компилятора по распределению регистров под переменные;

- обращение к памяти допускается лишь с помощью специальных команд чтения и записи;

- используются трехадресные команды, что помимо упрощения дешифрации дает возможность сохранять большее число переменных в регистрах без их последующей перезагрузки

- эффективно загружен конвейер команд.

Элементы RISС-архитектуры впервые появились в вычислительных машинах CDC 6600 и супер-ЭВМ компании Сгау Research. Однако окончательно понятие RISC в современном его понимании сформировалось на базе трех исследовательских проектов компьютеров: процессора 801 компании IBM, процессора RISC университета Беркли и процессора MIPS Стенфордского университета.

Разработка экспериментального проекта компании IBM началась еще в конце 70-х годов, но его результаты никогда не публиковались и компьютер на его основе в промышленных масштабах не изготавливался. В 1980 году Д.Паттерсон со своими коллегами из Беркли начали свой проект и изготовили две машины, которые получили названия RISC-I и RISC-II. Главными идеями этих машин было отделение медленной памяти от высокоскоростных регистров и использование регистровых окон. В 1981году Дж.Хеннесси со своими коллегами опубликовал описание стенфордской машины MIPS, основным аспектом разработки которой была эффективная реализация конвейерной обработки посредством тщательного планирования компилятором его загрузки.

Достаточно успешно реализуется RISС-архитектура и в современных ВМ, например в процессорах Alpha серии РА фирмы Hewlett-Packard, семействе PowerPC и т. п. Отметим, что в последних микропроцессорах фирмы Intel и AMD широко используются идеи, свойственные RISС- архитектуре, так что многие различия между CISC и RISC постепенно стираются.

Концепция архитектуры команд cо словами сверхбольшой длины (VLIW) базируется на RISС-архитектуре, где несколько простых RISC- команд объединяются в одну сверхдлинную команду и выполняются параллельно. См. процессоры Itanium, Transmeta.

Важную роль в выборе АСК играет ответ на вопрос о том, где могут храниться операнды и каким образом к ним осуществляется доступ. С этих позиций различают следующие виды архитектур системы команд:

- стековую;

- аккумуляторную;

- регистровую;

- с выделенным доступом к памяти.

Стековая архитектура

- Подробности

- Родительская категория: Процессор

- Категория: Архитектуры системы команд

Стеком называется память, состоящая из взаимосвязанных ячеек, взаимодействующих по принципу "последним вошел — первым вышел" (LIFO, Last In First Out).

Верхнюю ячейку называют вершиной стека. Для работы со стеком предусмотрены две операции: рush (проталкивание данных в стек) и рор (выталкивание данныx из стека). Запись возможна только в верхнюю ячейку стека, при этом вся хранящаяся в стеке информация предварительно проталкивается на одну позицию вниз. Чтение допустимо также только из вершины стека. Извлеченная информация удаляется из стека, а оставшееся его содержимое продвигается вверх. В вычислительных машинах, где реализована АСК на базе стека (их обычно называют стековыми), операнды перед обработкой помещаются в две верхних ячейки стековой памяти. Результат операции заносится в стек.

В большинстве процессоров стек (т.е. память со стековым доступом) организован в участке обычной памяти с адресной организацией. Для этого в процессоре имеется специальный регистр — указатель стека (Stack Pointer SP). Этот регистр содержит адрес памяти того участка, в который будет осуществляться стековый доступ, а, говоря более точно, адрес "верхушки стека". Указатель стека обычно программно доступен, то есть к нему можно производить обращение как к любому другому регистру.

При описании вычислений с использованием стека обычно используется иная форма записи математических выражений, известная как обратная польская запись (обратная польская нотация), которую предложил польский математик Я. Лукашевич. Особенность ее в том, что в выражении отсутствуют скобки, а знак операции располагается не между операндами, а следует за ними (постфиксная форма). Последовательность операций определяется их приоритетами. Выражение а = а + b + а х с в постфиксной форме будет записано в виде: а = а b + а с х +.

АСК на основе стека долгое время считался неперспективным. Однако в послнеднее время возрождается интерес к стековой архитектуре ВМ. Это связано с популярностью языкa Java и расширением сферы применения языка Forth, семантике которых наиболее близка именно стековая архитектура.

Аккумуляторная архитектура

- Подробности

- Родительская категория: Процессор

- Категория: Архитектуры системы команд

Архитектура на базе аккумулятора исторически возникла одной из первых. В ней для хранения одного из операндов арифметической или логической операции в процессоре имеется выделенный регистр — аккумулятор. В этот же регистр заносится и результат операции. Поскольку адрес одного из операндов предопределен, в командах обработки достаточно явно указать местоположение только второго операнда. Изначально оба операнда хранятся в основной памяти, и до выполнения операции один из них нужно загрузить в аккумулятор. После выполнения команды обработки результат находится в аккумуляторе и, если он не является операндом для последующей команды, его требуется сохранить в ячейке памяти.

Для загрузки в аккумулятор содержимого ячейки х предусмотрена команда загрузки load х. По этой команде информация считывается из ячейки памяти х, выход памяти подключается к входам аккумулятора и происходит занесение считанных данных в аккумулятор. Запись содержимого аккумулятора в ячейку х осуществляется командой сохранения store х, при выполнении которой выходы аккумулятора подключаются шине, после чего информация записывается в память. Для выполнения операции в АЛУ производится считывание одного из операндов из памяти в регистр данных. Второй операнд находится в аккумуляторе. Выходы регистра данных и аккумулятора подключаются к соответствующим входам АЛУ. По окончании предписанной операции результат с выхода АЛУ заносится в аккумулятор.

Достоинствами аккумуляторной АСК можно считать короткие команды и простоту декодирования команд. Однако наличие всего одного регистра порождает многократные обращения к основной памяти.

Регистровая архитектура

- Подробности

- Родительская категория: Процессор

- Категория: Архитектуры системы команд

В машинах данного типа процессор включает в себя массив регистров (регистровый файл), известных как регистры общего назначения (РОН). Эти регистры в каком-то смысле можно рассматривать как явно управляемый КЭШ для хранения недавно использовавшихся данных.

Размер регистров обычно фиксирован и совпадает с размером машинного слова. К любому регистру можно обратиться, указав его номер. Количество РОН в архитектурах типа CISC обычно невелико (от 8 до 32), и для представления номера конкретного регистра необходимо не более пяти разрядов, благодаря чему в адресной части команд обработки допустимо одновременно указать номера двух, а зачастую и трех регистров (двух регистров операндов и регистра результата). RISС-архитектура предполагает использование существенно большего числа РОН (до нескольких сотен), однако типичная для таких ВМ длина команды (обычно 32 разряда) позволяет определить в команде до трех регистров.

Регистровая архитектура допускает расположение операндов в одной из двух запоминающих сред: основной памяти или регистрах. С учетом возможного размещения операндов в рамках регистровых АСК выделяют три подвида команд обработки: регистр-регистр; регистр- память; память-память. Вариант "регистр-регистр" характеризуется простотой реализации, фиксированной длиной команды, быстрым выполнением команды, но большой длиной кода; он является основным в вычислительных машинах типа RISC. Команды типа "регистр-память" имеют компактный код, простое декодирование, но для них характерны длинное место адреса в коде и потеря операнда при записи (СISC-машины). Вариант "память-память" считается неэффективным, хотя и остается в некоторых моделях класса СISC.

К достоинствам регистровых АСК следует отнести: компактность получаемого кода, высокую скорость вычислений за счет замены обращений к памяти на обращения к регистрам. С другой стороны, данная архитектура требует более длинных инструкций по сравнению с аккумуляторной архитектурой. В наши дни именно регистровая архитектура является преобладающей.

Архитектура с выделенным доступом к памяти

- Подробности

- Родительская категория: Процессор

- Категория: Архитектуры системы команд

В архитектуре с выделенным доступом к памяти обращение к основной памяти возможно только с помощью двух специальных команд: load и store. По команде load информация считывается из ячейки памяти в регистр процессора. Запись из регистра в память происходит по команде store. Операнды во всех командах обработки могут находиться только в регистрах процессора (в регистрах общего назначения). Результат операции также заносится в регистр. В архитектуре отсутствуют команды обработки, допускающие прямое обращение к основной памяти. АСК с выделенным доступом к памяти характерна для всех вычислительных машин с RISC-архитектурой. Команды в таких ЭВМ, как правило, имеют длину 32 бита и трехадресный формат. Примеры процессоров: Sun SPARC, MIPS R10000, DEC Alpha, PowerPC и др.