Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

Процессор

Процессор

Арифметико логическое устройство (АЛУ)

- Подробности

- Родительская категория: Процессор

- Категория: Процессор — аппаратный уровень.

Общие сведения об арифметико логическом устройстве

Арифметико логическое устройство - это комбинационная схема, (т.е. она не содержит внутри элементов памяти), выполняющая следующие функции:

- принимающая на два входа два операнда (например, содержимое двух регистров);

- формирующая на выходе результат операции.

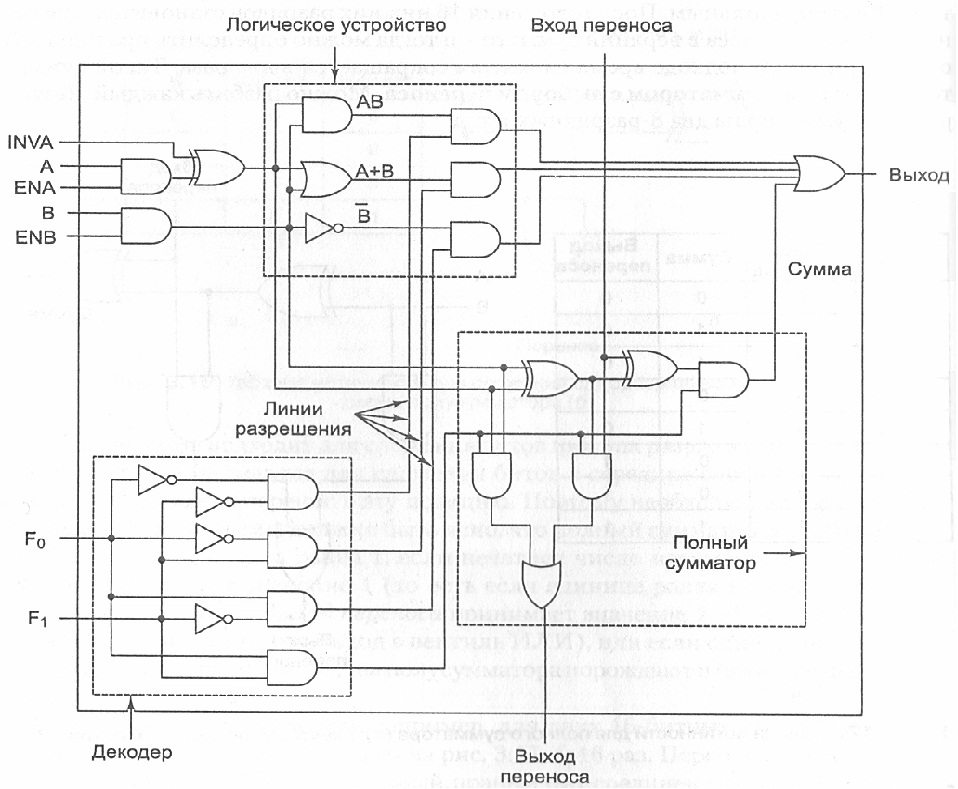

Большинство компьютеров содержат одну общую схему для выполнения операций И, ИЛИ и сложения над двумя машинными словами. Обычно такая схема для n-битных слов состоит из n идентичных схем для индивидуальных битовых позиций. На рисунке изображена схема одноразрядного АЛУ. Это устройство может вычислять одну из 4 следующих функций: А И В, А ИЛИ В, В- и А + В. Выбор функции зависит от того, какие сигналы поступают на линии F0 и F1: 00, 01, 10 или 11 (в двоичной системе счисления). Отметим, что здесь А+В означает арифметическую сумму А и В, а не логическую операцию И. В левом нижнем углу схемы находится двухразрядный декодер, который порождает сигналы включения для четырех операций. Выбор операции определяется сигналами управления F0 и F1. В зависимости от значений F0 и F1 выбирается одна из четырех линий разрешения, и тогда выходной сигнал выбранной функции проходит через последний вентиль ИЛИ. В верхнем левом углу схемы находится логическое устройство для вычисления А И В, А ИЛИ В и В-, но по крайней мере, один из этих результатов проходит через последний вентиль ИЛИ в зависимости от того, какую из разрешающих линий выбрал декодер. Так как ровно один из выходных сигналов декодера будет равен 1, то и запускаться будет ровно один из четырех вентилей И.

Схема одноразрядного АЛУ

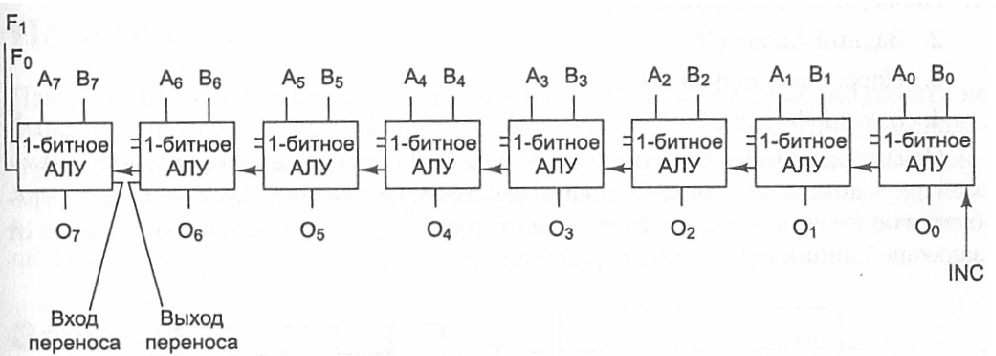

Остальные три вентиля будут выдавать 0 независимо от значений А и В.АЛУ может выполнять не только логические и арифметические операции над А и В, но и делать их равными нулю, отрицая ENA (сигнал разрешения А) или ENB (сигнал разрешения В). Можно также получить А-, установив INV А (инверсию А). При нормальных условиях и ENA, и ENB равны 1, чтобы разрешить поступление обоих входных сигналов, а сигнал INV А равен 0. В этом случае А и В просто поступают в логическое устройство без изменений. В нижнем правом углу находится полный сумматор для подсчета суммы А и В и для осуществления переносов. Переносы необходимы, поскольку несколько таких схем могут быть соединены для выполнения операций над целыми словами. Одноразрядные схемы, подобные той, которая изображена выше, называются разрядными микропроцессорными секциями. Они позволяют разработчику сконструировать АЛУ любой желаемой ширины. АЛУ можно представить как комбинационную схему, имеющую две входные шины (туда подаются два операнда) и одну выходную (на ней получается результат). Кроме того, АЛУ имеет несколько управляющих входов, сигналы на которых определяют выполняемую операцию(рисунок ниже).

Схема восьмиразрядного АЛУ и его обозначение

Аккумуляторная архитектура

- Подробности

- Родительская категория: Процессор

- Категория: Архитектуры системы команд

Архитектура на базе аккумулятора исторически возникла одной из первых. В ней для хранения одного из операндов арифметической или логической операции в процессоре имеется выделенный регистр — аккумулятор. В этот же регистр заносится и результат операции. Поскольку адрес одного из операндов предопределен, в командах обработки достаточно явно указать местоположение только второго операнда. Изначально оба операнда хранятся в основной памяти, и до выполнения операции один из них нужно загрузить в аккумулятор. После выполнения команды обработки результат находится в аккумуляторе и, если он не является операндом для последующей команды, его требуется сохранить в ячейке памяти.

Для загрузки в аккумулятор содержимого ячейки х предусмотрена команда загрузки load х. По этой команде информация считывается из ячейки памяти х, выход памяти подключается к входам аккумулятора и происходит занесение считанных данных в аккумулятор. Запись содержимого аккумулятора в ячейку х осуществляется командой сохранения store х, при выполнении которой выходы аккумулятора подключаются шине, после чего информация записывается в память. Для выполнения операции в АЛУ производится считывание одного из операндов из памяти в регистр данных. Второй операнд находится в аккумуляторе. Выходы регистра данных и аккумулятора подключаются к соответствующим входам АЛУ. По окончании предписанной операции результат с выхода АЛУ заносится в аккумулятор.

Достоинствами аккумуляторной АСК можно считать короткие команды и простоту декодирования команд. Однако наличие всего одного регистра порождает многократные обращения к основной памяти.

Команды обработки

- Подробности

- Родительская категория: Процессор

- Категория: Система команд процессора

Арифметические команды

Минимальный набор арифметических команд очень мал. Это (например):

- сложение — ADD;

- инвертирование — COM / NOT (такая ЭВМ действительно была: PDP-8 (DEC));

- прибавление "единицы" — INC.

Все остальное можно сделать, комбинируя эти команды.

Однако в современном микропроцессоре арифметических команд обычно больше:

- SUB — вычитание;

- CMP — сравнение операндов. Эта команда выполняет вычитание операндов, по результату изменяет флаги, после чего результат теряется (команда предназначена для проверки условий);

- NEG — смена знака операнда;

- ASR, ASL, SAR, SAL — арифметические сдвиги операнда (Arithmetic Shift to Right/Left);

- INC, DEC — увеличение или уменьшение операнда на 1;

- ADC, SBC/SBB - операции с переносом C (carry-bit) — для выполнения действий с повышенной точностью, когда операнд занимает несколько слов;

- SXT, SEX, CBW, CWD, CDQ — расширение знака (преобразование в формат с повышенной разрядностью);

- MUL, DIV — умножение и деление беззнаковых и знаковых чисел.

- Набор операций с плавающей точкой, включающий обычно значительное количество команд (несколько десятков), в которые часто входят команды вычисления элементарных функций — Sin, Cos, Log, Exp и т.п.

Логические команды

Логические команды — это команды побитовой обработки.

- OR — поразрядное логическое сложение. Фактически это команда побитовой установки (т.е. записи "единицы" в заданные биты операнда). Пример:

or opr, 0Ch ;Установка в 1 битов в позициях 2 и 3 в операнде al

Если исходно в al содержался, например, операнд 1101 10012, то после выполнения команды в al будет содержаться: 1101 1101 (отмечены установленные биты). Второй операнд — обычно константа, задавая которую, программист указывает, какие биты следует установить (он на жаргоне программистов носит название "маска").

Можно описать действие команды OR следующим образом: команда безусловно устанавливает в "единицу" биты в тех позициях первого операнда, которые отмечены "единицами" во втором операнде (в маске), оставляя прочие биты первого операнда неизменными.

- AND — поразрядное логическое умножение. Это команда побитового сброса (записи в заданные биты "нулей"). Пример:

and bh, 0Fh ;Сброс старшей тетрады (старшего ниббла) в байтовом операнде.

Если, например, исходно в регистре bh содержался операнд 1101 10012, то после выполнения команды в регистре bh будет содержаться 0000 10012 (отмечены очищенные биты). Действие команды AND можно описать следующим образом: команда безусловно сбрасывает в 0 биты в тех позициях первого операнда, которые отмечены "нулями" в маске, оставляя прочие биты первого операнда неизменными.

- XOR — поразрядное исключающее ИЛИ, eXclusive OR (иногда на русском эту операцию называют "ЛИБО"). Эта двухоперандная команда фактически выполняет выборочное инвертирование битов. Например:

xor cl,0F0h ;Инвертирование битов старшей тетрады

Если исходно в cl содержалось 1101 10012, то после выполнения команды в cl будет содержаться 0010 10012 (отмечены проинвертированные биты). Действие команды xor можно описать так: команда инвертирует в первом операнде биты в позициях, которые отмечены в маске "единицами", оставляя прочие биты неизменными.

- TEST — проверка битовых полей. Команда чаще всего двухоперандная, выполняет поразрядное логическое умножение операндов и по результату операции изменяет состояние флагов "нуля" zf и "знака" sf, после чего результат операции теряется.

- NOT, COM — инвертирование операнда (замена значения каждого бита на противоположное). Это однооперандная команда.

Сдвиги

Операция сдвига состоит в одновременном перемещении содержимого операнда в разрядной сетке. Существует 3 разновидности операции сдвигов, которые различаются тем, что происходит с битами, выходящими за пределы разрядной сетки с одного "конца" операнда, и с освобождающимися позициями на другом его "конце".

- ROR, ROL, RCR, RCL — циклические сдвиги. При циклическом сдвиге то, что выходит за границу разрядной сетки, помещается в освобождающуюся позицию на другом конце операнда.

- ASR, ASL/SAR, SAL — арифметические сдвиги. Эта разновидность сдвига осуществляется таким образом, что результат оказывается эквивалентен умножению (при сдвиге влево) или делению (при сдвиге вправо) операнда на основание системы счисления, т.е. на 2. Сравните: если "сдвинуть" цифры в десятичном числе на разряд влево, результат будет эквивалентен исходному числу, умноженному на 10 (12 и 120 после сдвига). Более подробно особенности арифметического сдвига обсуждаются при рассмотрении системы команд процессоров х86.

- SHL, SHR — логические сдвиги. При выполнении логических сдвигов биты, "выдвигаемые" из разрядной сетки, теряются, а противоположный конец операнда заполняется "нулями".

Каждая из упомянутых разновидностей может также иметь варианты.

Например, в составе системы команд х86 различают пять видов сдвигов.

Организация в программе циклических конструкций

- Подробности

- Родительская категория: Процессор

- Категория: Управление вычислительным процессом

В языках высокого уровня используется несколько разновидностей

циклов. Все они предусматривают следующие общие свойства:

- Если цикл не предусматривает специально бесконечного повторения, в последовательности команд должен быть фрагмент, проверяющий условие выхода из цикла.

- Если условие выхода из цикла не выполнено, производится передача управления на начало последовательности команд, образующих цикл.

Один из вариантов цикла предусматривает заранее (до начала выполнения цикла) определенное количество повторений. В этом случае:

- заводят специальную переменную;

- перед началом цикла заносят в нее требуемое количество повторений;

- выполняют команды цикла;

- в конце цикла уменьшают переменную цикла на 1;

- проверяют переменную цикла на равенство нулю и, если не равно, повторяют, начиная с п.3

В системе команд процессоров х86 есть команда организации цикла loop. Ее недостаток состоит в том, что она в качестве переменной-счетчика цикла позволяет использовать только регистр процессора ECX. Это ее свойство затрудняет организацию вложенных циклических конструкций.

Операционные устройства с плавающей запятой

- Подробности

- Родительская категория: Процессор

- Категория: Процессор — аппаратный уровень.

Операции над числами с плавающей запятой имеют существенные отличия от операций целочисленной арифметики, поэтому их реализуют с помощью самостоятельного операционного устройства (ОП). Минимальный набор операций этого устройства включает четыре действия: сложение, вычитание, умножение и деление. Операции выполняются над числами в формате IEEE 754. Особенностью ОП является то, что операции над тремя составляющими чисел с ПЗ (знаками, мантиссами и порядками операндов) выполняются раздельно:

- блоком обработки знаков;

- блоком обработки порядков;

- блоком обработки мантисс.

Для хранения операндов и результата предусмотрены соответствующие регистры. В арифметике с плавающей запятой сложение и вычитание — более сложные операции, чем умножение и деление. Это обусловлено тем, что необходимо выравнивать порядки операндов. Алгоритм сложения включает следующие этапы:

- Подготовительный этап.

- Определение операнда, имеющего меньший порядок, и сдвиг его мантиссы вправо на число разрядов, равное разности порядков операндов.

- Приравнивание порядка результата большему из порядков операндов.

- Сложение мантисс.

- Проверка на переполнение.

- Заключительный этап.

Подготовительный этап осуществляет "распаковку" чисел с ПЗ, загрузку трех составляющих. В старший разряд мантиссы восстанавливается единица. Здесь может быть выполнена проверка на равенство нулю одного или обоих операндов. Это позволяет исключить ненужные операции. Действия на заключительном этапе сводятся к выявлению нулевого значения мантиссы, нормализации мантиссы, выявлению отрицательного переполнения порядка (появляется денормализованный операнд), "упаковке" составляющих результата. В отличие от целочисленной арифметики, в операциях с ПЗ сложение и вычитание производятся приближенно, так как при выравнивании порядков происходит потеря младших разрядов одного из слагаемых. В этом случае погрешность всегда отрицательна и может доходить до единицы младшего разряда. Умножение чисел с ПЗ включает следующую последовательность этапов:

- Подготовительный этап.

- Проверка на равенство нулю одного из сомножителей. Если один из них ноль, то в качестве результата выдается нуль в формате чисел с ПЗ.

- Сложение порядков. Если используется смещенный порядок, то из полученной суммы вычитается величина смещения. Проводится анализ переполнения и антипереполнения поля порядка (возникает прерывание по особому случаю).

- Перемножение мантисс с учетом знака. Результат округляется до длины поля мантиссы.

- Заключительный этап.

Еще статьи...

Подкатегории

-

Кодирование команд в процессоре х86

- Кол-во материалов:

- 2

-

Управление вычислительным процессом

- Кол-во материалов:

- 8

-

Способы адресации

- Кол-во материалов:

- 2

-

Система команд процессора

- Кол-во материалов:

- 6

-

Архитектуры системы команд

- Кол-во материалов:

- 5

-

Конвейер команд

- Кол-во материалов:

- 1

-

Устройство управления. Микропрограммный автомат

- Кол-во материалов:

- 2

-

Процессор — аппаратный уровень.

- Кол-во материалов:

- 4