Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

PCI и PCI-X

Шины PCI и PCI-X

Прерывания сообщениями — MSI

На шине PCI имеется прогрессивный механизм оповещения об асинхронных событиях, основанный на передаче сообщений MSI (Message Signaled Interrupts). Здесь для сигнализации запроса прерывания устройство запрашивает управление шиной и, получив его, посылает сообщение. Сообщение выглядит как обычная запись двойного слова в ячейку памяти, адрес (32-битный или 64-битный) и шаблон сообщения на этапе конфигурирования устройств записываются в конфигурационные регистры устройства (точнее, функции). В сообщении старшие 16 бит всегда нулевые, а младшие 16 бит несут информацию об источнике прерывания. Устройство (функция) могут нуждаться в сигнализации нескольких типов запросов; в соответствии с его потребностями и своими возможностями система указывает устройству (функции), сколько различных типов запросов оно может вырабатывать.

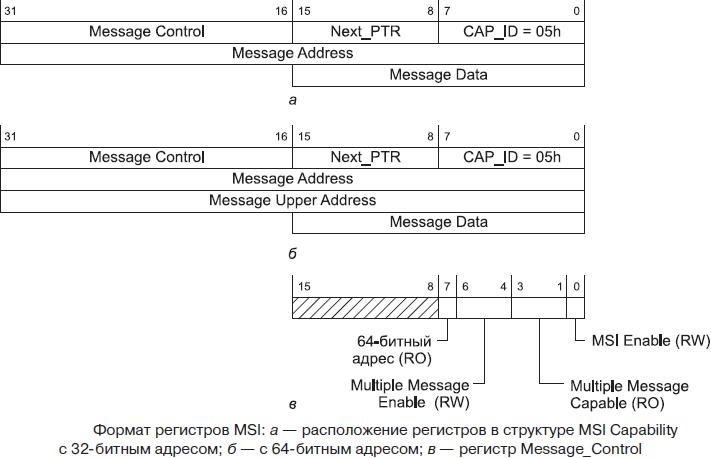

Возможность использования MSI описывается в конфигурационном пространстве структурой MSI Capability (CAP_ID = 05h), которая должна присутствовать в пространстве каждой функции, поддерживающей MSI. В структуре имеется 3 или 4 регистра (см. рисунок ниже):

- Message Address — 32-разрядный адрес памяти, по которому передается сообщение (биты [1:0] = 00). Если используется 64-битный адрес (установлен бит 7 в регистре Message Control), то его старшая часть располагается в регистре Message Upper Address. Значения в регистры адреса заносит системное ПО на этапе конфигурирования;

- Message Data — 16-битный шаблон данных, передаваемых в сообщении по линиям AD[15:0]. Значение шаблона записывается системным ПО на этапе конфигурирования. В сообщении, передаваемом функцией, для различения разных условий прерывания могут модифицироваться только несколько младших бит, количество которых определяется значением поля Multiple Message Enable. Остальные биты сообщения должны соответствовать шаблону; биты [31:16] всегда нулевые;

- Message Control — управление сообщениями (16 бит). Битом 7 функция сообщает о способности генерировать 64-битный адрес. В поле Multiple Message Capable функции задается ее способность генерировать различимые условия прерывания, в поле Multiple Message Enable система указывает функции допустимое число условий. Здесь значения 000–101 двоично кодируют число младших бит шаблона, которые устройство может модифицировать для идентификации источника прерывания: 000 — ни одного (устройству доступен лишь один идентификатор), 101 — пять, значения 110 и 111 зарезервированы. Бит MSI_Enable разрешает использование MSI.

По аппаратному сбросу MSI запрещен; его можно разрешить программно установкой бита MSI Enable (после программирования адреса и шаблона сообщения), и тогда генерация прерываний по линиям INTx# запрещается. Самая «богатая» прерываниями функция (для которой Multiple Message Enable = 101) при записи сообщения идентифицирует конкретное условие прерывания (одно из 32 возможных) по линиям AD[4:0].

Отметим, что быстрая посылка подряд двух и более одинаковых сообщений может быть воспринята системой как одно прерывание (из-за низкой реактивности). Если требуется обработка каждого из них, обработчик должен обеспечивать уведомление устройства, а оно не должно посылать следующее сообщение до получения уведомления, чтобы прерывания не терялись. Различающиеся сообщения друг другу не мешают.

Прерывания через MSI позволяют избежать бед разделяемости, обусловленной дефицитом линий запросов прерывания в PC. Кроме того, они решают проблему целостности данных: все данные, записываемые устройством до посылки MSI, дойдут до получателя гарантированно раньше начала обработки MSI. Прерывания через MSI от одних устройств в одной системе могут использоваться наряду с обычными INTx# от других устройств. Но каждое устройство (функция), использующее MSI, не должно использовать прерывания через линии INTx#.

Механизм MSI может использоваться на системных платах, имеющих «продвинутый» контроллер прерываний APIC. Правда, конкретная реализация поддержки MSI может потенциальные возможности облегчения идентификации большого числа запросов прерывания свести лишь к увеличению числа доступных запросов прерываний (и используемых ими векторов). Так, например, для системных плат на чипсетах с хабом ICH2 и ICH3 фирмы Intel поддержка MSI сводится к организации альтернативных путей подачи запросов IRQ[1:23] на входы APIC (запросы IRQ с номерами 0, 2, 8 и 13 через MSI не передаются). Всем устройствам PCI назначается один и тот же адрес сообщений (Message Address = FEC00020h), по которому в APIC находится регистр IRQ Pin assertion. В сообщении используются лишь младшие 5 бит, в которых указывается номер взводимого запроса прерывания в диапазоне 1–23 (исключая 2, 8 и 13). Линии запросов, используемые в MSI, программируются на чувствительность к перепаду (сообщения имитируют только фронт сигнала). По этой причине прерывания с номерами, используемыми в MSI, не могут использоваться совместно (разделяемо) с прерываниями, полученными другими способами (по линиям запросов от устройств PCI и от других устройств системной платы). Возможно, что в других платформах прерывания через MSI используются более эффективно.

Отложенные транзакции

Отложенные транзакции выполняются мостом PCI для всех команд обращения к вводу-выводу и конфигурационным регистрам, а также всех разновидностей чтения памяти. Отложенные транзакции выполняются в три фазы:

- запрос транзакции инициатором (обмена данными с целевым устройством еще нет);

- завершение целевым устройством;

- завершение инициатором.

Для того чтобы отложить транзакцию, мост должен поставить в очередь отложенный запрос (delayed request) и сигналом STOP# ввести условие Retry. На этом первая фаза отложенной транзакции завершается. В запросе содержатся зафиксированные значения адреса, команды, разрешенных байт, линий четности (и линии REQ64для 64-битных шин); для отложенных транзакций записи нужно сохранить еще и данные. Этой информации мосту достаточно, чтобы инициировать транзакцию на противоположном интерфейсе, — вторую фазу отложенной транзакции. Ее результатом будет преобразование в очереди отложенного запроса в отложенное завершение (delayed completion) — запрос вместе с ответом в виде состояния (и запрошенных данных чтения). Изначальный инициатор транзакции, получив условие Retry, должен через некоторое время повторить запрос, причем в точности совпадающий с первоначальным (иначе он мостом будет воспринят как новый). Если к этому моменту мост успел отработать данную транзакцию, то этот повторный запрос будет завершен нормальным образом (или отвергнут, если так ответило целевое устройство), а мост удалит отложенное завершение из своей очереди. Если транзакция еще не отработана, то мост снова запросит повтор, и инициатор должен будет повторять свой запрос до тех пор, пока мост не обеспечит нормального завершения. Это будет третьей, заключительной фазой отложенной транзакции.

Инициатор, получивший условие Retry, обязан в точности повторить тот же запрос транзакции, иначе мост будет накапливать невостребованные ответы. Конечно, и мост должен отслеживать невостребованные транзакции и через некоторое время (210 или 215 тактов шины, в зависимости от значений в регистре Bridge Control) удалять их из своей очереди, чтобы не переполнить ее по «забывчивости» инициатора.

Откладывание транзакций мостом заметно увеличивает время исполнения каждой из них (с точки зрения инициатора), однако оно позволяет обслуживать множество транзакций, находящихся в очередях мостов. В результате достигается увеличение суммарного объема произведенных транзакций на всех шинах PCI за единицу времени, то есть повышается производительность системы в целом. Мост, как держатель очереди транзакций, в принципе, может одновременно выполнять две транзакции, каждую на своем интерфейсе. Если бы транзакции не откладывались, а выполнялись непосредственно, то инициатору пришлось бы держать свою шину до тех пор, пока не освободится шина назначения (и все промежуточные шины, если транзакция проходит через несколько мостов). В результате число бесполезных тактов ожидания на всех шинах было бы недопустимо велико.

Транслируя транзакции чтения памяти (как отложенные запросы), мост в некоторых случаях может использовать предвыборку (prefetch, чтение про запас) с целью ускорения работы с памятью. Выполняя предвыборку, мост рискует считать из источника данных больше, чем инициатор заберет от него в данной транзакции. В фазе завершения транзакции инициатором лишние данные в буфере моста проще всего аннулировать, поскольку до возможного последующего востребования в их реальном источнике они могут быть уже модифицированы. Более сложный мост может отслеживать и эти изменения, аннулируя лишь модифицированные данные. Обращения командами обычного чтения памяти разрешают мосту считать только точно затребованное количество данных. При этом возможности ускорения передач меньше, но не возникнет побочных эффектов от лишних чтений. Лишние чтения совершенно недопустимы для регистров ввода-вывода, отображенных на память. Например, чтение управляющих регистров может изменять их состояние; лишнее (с неиспользуемым результатом) чтение регистров данных может привести к потере данных. Мост может смело выполнять предвыборку, когда отрабатывает запросы с командами чтения строк и множественного чтения, транслируемые в любом направлении. Применивший эти команды мастер отвечает за то, что для адресованных областей предвыборка допустима. Если у моста есть регистры, описывающие предвыбираемую память, то транзакции с командами простого чтения с первичного интерфейса, обращенные к предвыбираемой памяти на вторичном интерфейсе, при трансляции могут преобразовываться в команды чтения строк или множественного чтения. Мост может предположить также, что все транзакции к памяти с вторичного интерфейса имеют устройством назначения оперативную память и, следовательно, допускают предвыборку. Однако мост должен иметь специальный бит, запрещающий преобразование команд и предвыборку по этому предположению («слепая» предвыборка может порождать проблемы взаимодействия ПО и аппаратуры).

Классификация устройств PCI

Важной частью спецификации PCI является классификация устройств и указание кода класса в его конфигурационном пространстве (3 байта Class Code). Старший байт определяет базовый класс, средний — подкласс, младший — программный интерфейс (если он стандартизован). Код класса позволяет идентифицировать наличие определенных устройств в системе, это может быть сделано с помощью PCI BIOS. Для стандартизованных классов и интерфейсов (например, 01:01:80 — контроллер IDE или 07:00:01 — последовательный порт 16450) «заинтересованная» программа может найти требуемое устройство и выбрать подходящий вариант драйвера. Классификатор определяет организация PCI SIG, он регулярно обновляется на сайте http://www.pcisig.com. Нулевые значения полей, как правило, дают самые неопределенные описания. Значение подкласса 80h относится к «иным устройствам». Некоторые классы устройств приведены в таблице.

| Подкласс | Интерфейс | Назначение |

| Базовый класс | 00 | Устройства, разработанные до принятия классификации |

| 00 | 00 | Все, кроме VGA-совместимых |

| 01 | 00 | VGA-совместимый графический адаптер |

| Базовый класс | 01 | Контроллеры устройств хранения |

| 00 | 00 | Контроллер шины SCSI |

| 01 | xx | Контроллер IDE |

| 02 | 00 | Контроллер НГМД |

| 03 | 00 | Контроллер шины IPI |

| 04 | 00 | Контроллер RAID |

| Базовый класс | 02 | Сетевые контроллеры |

| 00 | 00 | Ethernet |

| 01 | 00 | Token Ring |

| 02 | 00 | FDDI |

| 03 | 00 | ATM |

| 04 | 00 | ISDN |

| Базовый класс | 03 | Дисплейные контроллеры |

| 00 | 00 | Совместимый с VGA (память 0A0000–0BFFFFh, порты 3B0–3BBh и 3C0–3DFh) |

| 00 | 01 | Совместимый с IBM-8514 (порты 2E8h, 2EAh-2EFh) |

| 01 | 00 | Контроллер XGA |

| 02 | 00 | Контроллер 3D |

| Базовый класс | 04 | Мультимедийные устройства |

| 00 | 00 | Видео |

| 01 | 00 | Аудио |

| 02 | 00 | Компьютерная телефония |

| Базовый класс | 05 | Контроллеры памяти |

| 00 | 00 | Контроллер памяти с произвольным доступом (RAM) |

| 01 | 00 | Контроллер флэш-памяти |

| Базовый класс | 06 | Мосты |

| 00 | 00 | Главный мост (Host bridge) |

| 01 | 00 | Мост PCI-ISA |

| 02 | 00 | Мост PCI-EIISA |

| 03 | 00 | Мост PCI-MCA |

| 04 | 00 | Мост PCI-PCI |

| 04 | 01 | Мост PCI-PCI с субтрактивным декодированием |

| 05 | 00 | Мост PCI-PCMCIA |

| 06 | 00 | Мост PCI-NuBus |

| 07 | 00 | Мост PCI-CardBus |

| 08 | xx | Мост PCI-RACEway |

| Базовый класс | 07 | Коммуникационные контроллеры |

| 00 | 00 | UART, совместимый с 8250 |

| 01 | UART, совместимый с 16450 | |

| 02 | UART, совместимый с 16550 | |

| ..... | ..... | |

| 06 | UART, совместимый с 16950 | |

| 01 | 00 | Стандартный LPT-порт |

| 01 | Двунаправленный LPT-порт | |

| 02 | Параллельный порт ECP 1.X | |

| 03 | Контроллер IEEE 1284 | |

| FEh | Целевое устройство IEEE 1284 | |

| 02 | 00 | Мультипортовый последовательный контроллер |

| 03 | 00 | Модем |

| 01 | Hayes-модем с интерфейсом 16450 | |

| 02 | Hayes-модем с интерфейсом 16550 | |

| 03 | Hayes-модем с интерфейсом 16650 | |

| 04 | Hayes-модем с интерфейсом 16750 | |

| Базовый класс | 08 | Системная периферия |

| 00 | 00 | Контроллер прерываний 8259 (PIC) |

| 01 | Контроллер прерываний ISA | |

| 02 | Контроллер прерываний EISA | |

| 10 | Контроллер прерываний I/O APIC | |

| 20 | Контроллер прерываний I/O(x) APIC | |

| 01 | 00 | Контроллер DMA 8237 |

| 01 | Контроллер DMA ISA | |

| 02 | Контроллер DMA EISA | |

| 02 | 00 | Системный таймер 8254 |

| 01 | Системный таймер ISA | |

| 02 | Системный таймер EISA | |

| 03 | 00 | Часы (RTC) |

| 01 | Часы (RTC) ISA | |

| 04 | 00 | Контроллер горячего подключения PCI |

| Базовый класс | 09 | Контроллеры устройств ввода |

| 00 | 00 | Контроллер клавиатуры |

| 01 | 00 | Дигитайзер (перо) |

| 02 | 00 | Контроллер мыши |

| 03 | 00 | Контроллер сканера |

| 04 | 00 | Игровой порт с фиксированным адресом |

| 01 | Игровой порт с перемещаемым адресом | |

| Базовый класс | Док-станции | |

| Базовый класс | Процессоры | |

| Базовый класс | Контроллеры последовательных шин | |

| 00 | 00 | Контроллер IEEE 1394 (FireWire) |

| 10 | Контроллер IEEE 1394 по спецификации OpenHCI | |

| 01 | 00 | Контроллер ACCESS.bus |

| 02 | 00 | Контроллер SSA |

| 03 | 00 | Контроллер USB по UHCI |

| 10h | Контроллер USB по OHCI | |

| 20h | Контроллер USB по EHCI | |

| FEh | Устройство USB | |

| Базовый класс | 0Dh | Контроллеры беспроводных интерфейсов |

| Базовый класс | 0Eh | Контроллеры интеллигентного ввода-вывода (I2O) |

| Базовый класс | 0Fh | Контроллеры спутниковых коммуникаций |

| Базовый класс | 10h | Контроллеры шифрования |

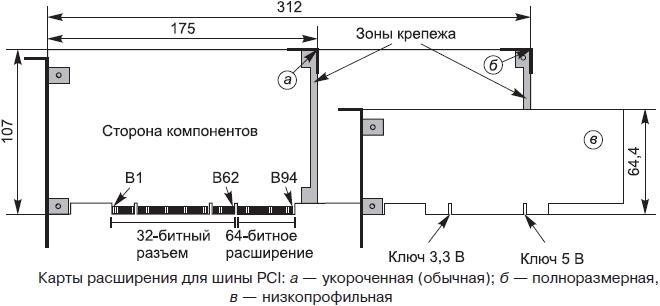

Стандартные слоты и карты PCI

Стандартные слоты PCI и PCI-X представляют собой щелевые разъемы, имеющие контакты с шагом 0,05 дюйма. Слоты расположены несколько дальше от задней панели, чем ISA/EISA или MCA. Компоненты карт PCI расположены на левой поверхности плат. По этой причине крайний PCI-слот обычно совместно использует посадочное место адаптера (прорезь на задней стенке корпуса) с соседним ISA-слотом. Такой слот называют разделяемым (shared slot), в него может устанавливаться либо карта ISA, либо PCI.

Карты PCI могут предназначаться для интерфейсных сигналов уровня 5 В и 3,3 В, а также быть универсальными. Слоты PCI имеют уровни сигналов, соответствующие питанию микросхем PCI-устройств системной платы (включая главный мост): либо 5 В, либо 3,3 В. Во избежание ошибочного подключения слоты имеют ключи, определяющие номинал напряжения. Ключами являются пропущенные ряды контактов 12, 13 и/или 50, 51:

- для слота на 5 В ключ (перегородка) расположен на месте контактов 50, 51 (ближе к передней стенке корпуса); такие слоты отменены в PCI 3.0;

- для слота на 3,3 В перегородка находится на месте контактов 12, 13 (ближе к задней стенке корпуса);

- на универсальных слотах перегородок нет;

- на краевых разъемах карт 5 В имеются ответные прорези только на месте контактов 50, 51; такие карты отменены в PCI 2.3;

- на картах 3,3 В прорези только на месте контактов 12, 13;

- на универсальных картах имеется оба ключа (две прорези).

Ключи не позволяют установить карту в слот с неподходящим напряжением питания. Карты и слоты различаются лишь питанием буферных схем, которое поступает с линий +V I/O:

- на слоте «5 В» на линии +V I/O подается + 5 В;

- на слоте «3,3 В» на линии +V I/O подается + (3,3–3,6) В;

- на карте «5 В» буферные микросхемы рассчитаны только на питание + 5 В;

- на карте «3,3 В» буферные микросхемы рассчитаны только на питание + (3,3– 3,6) В;

- на универсальной карте буферные микросхемы допускают оба варианта питания и будут нормально формировать и воспринимать сигналы по спецификациям 5 или 3,3 В, в зависимости от типа слота, в который установлена карта (то есть от напряжения на контактах + V I/O).

На слотах обоих типов присутствуют питающие напряжения + 3,3, + 5, + 12 и –12 В на одноименных линиях. В PCI 2.2 определена дополнительная линия 3.3Vaux — «дежурное» питание + 3,3 В для устройств, формирующих сигнал PME# при отключенном основном питании.

ПРИМЕЧАНИЕ!

Выше приведены положения из официальных спецификаций PCI. На современных системных платах пока чаще всего встречаются слоты, по ключу являющиеся 5вольтовыми. Однако при этом напряжение на линиях +V I/O и уровни сигналов интерфейса являются 3,3-вольтовыми. В этих слотах нормально работают все современные карты с 5-вольтовыми ключами — их интерфейсные схемы работают при питании как 3,3, так и 5 В. Интерфейс с 5-вольтовым питанием может работать только на частоте до 33 МГц. «Настоящие» 5-вольтовые системные платы были только для процессоров 486 и первых моделей Pentium.

Наибольшее распространение получили 32-битные слоты, заканчивающиеся контактами A62/B62. 64-битные слоты встречаются реже, они длиннее и заканчиваются контактами A94/B94. Конструкция разъемов и протокол позволяют устанавливать 64-битные карты как в 64-битные, так и в 32-битные разъемы, и наоборот, 34-битные карты как в 32-битные, так и в 64-битные разъемы. При этом разрядность обмена будет соответствовать слабейшему компоненту.

Для сигнализации об установке карты и потребляемой ею мощности на разъемах PCI предусмотрено два контакта — PRSNT1# и PRSNT2#, из которых хотя бы один соединяется на карте с шиной GND. С их помощью система может определить присутствие карты в слоте и ее энергопотребление. Кодирование потребляемой мощности приведено в таблице; здесь приведены значения и для малогабаритных карт Small PCI.

| Соединение контактов |

Потребляемая мощность | ||

| PRSNT1# | PRSNT2# | PCI | Small PCI |

| - | - | Нет карты | Нет карты |

| GND | - | 25 Вт макс | 10 Вт макс |

| - | GND | 15 Вт макс | 5 Вт макс |

| GND | GND | 7,5 Вт макс | 2 Вт макс |

Карты и слоты PCI-X по механическим ключам соответствуют 3,3-вольтовым картам и слотам; напряжение питания + V I/O для PCI-X Mode 2 устанавливается 1,5 В.

На рисунке изображены карты PCI в конструктиве PC/AT-совместимых компьютеров. Полноразмерные карты (Long Card, 107×312 мм) используются редко, чаще применяются укороченные платы (Short Card, 107×175 мм), но многие карты имеют и меньшие размеры. Карта имеет обрамление (скобку), стандартное для конструктива ISA (раньше встречались карты и с обрамлением в стиле MCA IBM PS/2). У низкопрофильных карт (Low Profile) высота не превышает 64,4 мм; их скобки также имеют меньшую высоту. Такие карты могут устанавливаться вертикально в 19-дюймовые корпуса высотой 2U (около 9 см).

Назначение выводов разъема карт PCI/PCI-X приведено в таблице ниже.

| Ряд B | № | Ряд A | Ряд B | № | Ряд A |

|---|---|---|---|---|---|

| -12В | 1 | TRST# | GND/M66EN1 | 49 | AD9 |

| TCK | 2 | +12 В | GND/Ключ 5 В/MODE2 | 50 | GND/Ключ 5 В |

| GND | 3 | TMS | GND/Ключ 5 В | 51 | GND/Ключ 5 В |

| TDO | 4 | TDI | AD8 | 52 | C/BE0# |

| +5 В | 5 | +5 В | AD7 | 53 | +3,3 В |

| +5 В | 6 | INTA# | +3,3 В | 54 | AD6 |

| INTB# | 7 | INTC# | AD5 | 55 | AD4 |

| INTD# | 8 | +5 В | AD3 | 56 | GND |

| PRSNT1# | 9 | ECC52 | GND | 57 | AD2 |

| ECC42 | 10 | +V I/O | AD1 | 58 | AD0 |

| PRSNT2# | 11 | ECC32 | +V I/O | 59 | +V I/O |

| GND/Ключ 3,3 В | 12 | GND/Ключ 3,3 В | ACK64#/ ECC1 | 60 | REQ64#/ ECC6 |

| GND/Ключ 3,3 В | 13 | GND/Ключ 3,3 В | +5 В | 61 | +5 В |

| ECC22 | 14 | 3.3Vaux3 | +5 В | 62 | +5 В |

| GND | 15 | RST# | Конец 32-битного разъема | ||

| CLK | 16 | +V I/O | Резерв | 63 | GND |

| GND | 17 | GNT# | GND | 64 | C/BE7# |

| REQ# | 18 | GND | C/BE6# | 65 | C/BE5# |

| +V I/O | 19 | PME#3 | C/BE4# | 66 | +V I/O |

| AD31 | 20 | AD30 | GND | 67 | PAR64/ECC72 |

| AD29 | 21 | +3,3 В | AD63 | 68 | AD62 |

| GND | 22 | AD28 | AD61 | 69 | GND |

| AD27 | 23 | AD26 | +V I/O | 70 | AD60 |

| AD25 | 24 | GND | AD59 | 71 | AD58 |

| +3,3 В | 25 | AD24 | AD57 | 72 | GND |

| C/BE3# | 26 | IDSEL | GND | 73 | AD56 |

| AD23 | 27 | +3,3 В | AD55 | 74 | AD54 |

| GND | 28 | AD22 | AD53 | 75 | +V I/O |

| AD21 | 29 | AD20 | GND | 76 | AD52 |

| AD19 | 30 | GND | AD51 | 77 | AD50 |

| +3.3 В | 31 | AD18 | AD49 | 78 | GND |

| AD17 | 32 | AD16 | +V I/O | 79 | AD48 |

| C/BE2# | 33 | +3,3 В | AD47 | 80 | AD46 |

| GND | 34 | FRAME# | AD45 | 81 | GND |

| IRDY# | 35 | GND | GND | 82 | AD44 |

| +3,3 В | 36 | TRDY# | AD43 | 83 | AD42 |

| DEVSEL# | 37 | GND | AD41 | 84 | +V I/O |

| PCIXCAP4 | 38 | STOP# | GND | 85 | AD40 |

| LOCK# | 39 | +3,3 В | AD39 | 86 | AD38 |

| PERR# | 40 | SMBCLK5 | AD37 | 87 | GND |

| +3,3 В | 41 | SMBDAT5 | +V I/O | 88 | AD36 |

| SERR# | 42 | GND | AD35 | 89 | AD34 |

| +3,3 В | 43 | PAR/ECC0 | AD33 | 90 | GND |

| C/BE1# | 44 | AD15 | GND | 91 | AD32 |

| AD14 | 45 | +3,3 В | Резерв | 92 | Резерв |

| GND | 46 | AD13 | Резерв | 93 | GND |

| AD12 | 47 | AD11 | GND | 94 | Резерв |

| AD10 | 48 | GND | Конец 64-битного разъема | ||

Примечание!

1 - Сигнал M66EN определен в PCI 2.1 только для слотов на 3,3 В.

2 — Сигнал введен в PCI-X 2.0 (прежде был резерв).

3 — Сигнал введен в PCI 2.2 (прежде был резерв).

4 — Сигнал введен в PCI-X (в PCI — GND).

5 — Сигналы введены в PCI 2.3. В PCI 2.0 и 2.1 контакты A40 (SDONE#) и A41 (SBOFF#) использовались для слежения за кэшем; в PCI 2.2 они были освобождены (для совместимости на системной плате эти цепи подтягивались к высокому уровню резисторами 5 кОм).

На слотах PCI имеются контакты для тестирования адаптеров по интерфейсу JTAG (сигналы TCK, TDI, TDO, TMS и TRST#). На системной плате эти сигналы задействованы не всегда, но они могут и организовывать логическую цепочку тестируемых адаптеров, к которой можно подключить внешнее тестовое оборудование. Для непрерывности цепочки на карте, не использующей JTAG, должна быть связь TDI–TDO.

На некоторых старых системных платах позади одного из слотов PCI встречается разъем Media Bus, на который выводятся сигналы ISA. Он предназначен для размещения на карте PCI звукового чипсета, предназначенного для шины ISA. Большинство сигналов PCI соединяются по чистой шинной топологии, то есть одноименные контакты слотов одной шины PCI электрически соединяются друг с другом. Из этого правила есть несколько исключений:

- сигналы REQ# и GNT# индивидуальны для каждого слота, они соединяют слот с арбитром (обычно — мостом, подключающим эту шину к вышестоящей);

- сигнал IDSEL для каждого слота соединяется (возможно, через резистор) с одной из линий AD[31:11], задавая номер устройства на шине;

- сигналы INTA#, INTB#, INTC#, INTD# циклически сдвигаются по контактам, обеспечивая распределение запросов прерываний;

- сигнал CLK заводится на каждый слот индивидуально от своего выхода буфера синхронизации; длина подводящих проводников выравнивается, обеспечивая синхронность сигнала на всех слотах (для 33 МГц допуск ± 2 нс, для 66 МГц — ± 1 нс).

Когда обычная системная плата используется в низкопрофильных корпусах, для подключения карт расширения можно использовать пассивный переходник (Riser Card), устанавливаемый в один из слотов PCI. Если в переходник устанавливается более одной карты, то для реализации вышеупомянутых исключений используют выносные разъемы PCI (маленькие печатные платы), с помощью которых вышеперечисленные сигналы берутся от других, свободных слотов PCI на системной плате. Переставляя эти разъемы, можно менять номера устройств на слотах переходника, а главное — их раскладку по линиям запросов прерывания. Беда такого подключения — длинные (10–15 см) шлейфы, соединяющие переходник со слотами. Все сигналы в этом шлейфе передаются по параллельным неперевитым проводам, что очень плохо для сигнала CLK: его форма искажается и вносится значительная задержка. Результатом могут быть внезапные «зависания» компьютера без всяких диагностических сообщений. В такой ситуации может помочь отделение провода CLK от общего шлейфа и встречное скручивание его свободного конца (это уменьшает индуктивность проводника). Остальные сигналы в шлейфе не так критичны к качеству разводки. Лучшим решением будет использование низкопрофильных карт PCI, устанавливаемых в системную плату без переходников. Проблема не возникала бы, если бы на переходнике была установлена микросхема источника синхронизации, раздающего синхросигнал на все слоты переходника. Однако это требует применения микросхем с ФАПЧ (PLL), привязывающих свой выходной сигнал к сигналу синхронизации от системной платы, что несколько удорожает переходник.

Обмен сообщениями между устройствами (команда DIM)

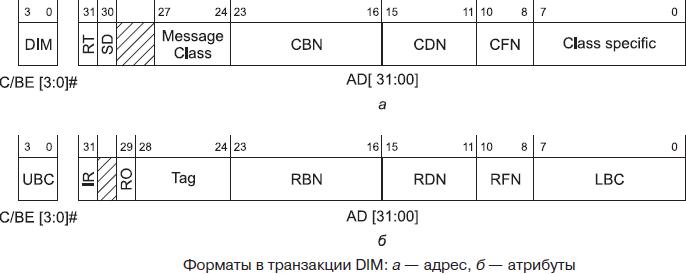

В PCI-X 2.0 введена возможность передачи информации (сообщений) устройству, адресуясь с помощью идентификатора (номера шины, устройства и функции). Для адресации и маршрутизации этих сообщений, которыми могут обмениваться любые устройства шины (включая и главный мост), не используется адресное пространство памяти или ввода/вывода. Сообщения передаются последовательностями, в которых используются команды DIM (Device ID Message), отличающиеся специфичностью адреса и атрибутов. В фазе адреса (рисунок ниже, а) передается идентификатор получателя сообщений (Completer ID) — номер его шины (CBN), устройства (CDN) и функции (CFN). Бит RT (Route Type) указывает тип маршрутизации сообщения: 0 — явная адресация с использованием вышеуказанного идентификатора, 1 — неявная адресация к главному мосту (при этом идентификатор не используется). Бит SD (Silent Drop) задает способ отработки ошибок при выполнении данной транзакции: 0 — обычный (как для записи в память), 1 — игнорирование некоторых типов ошибок (но не контроля четности или ECC). Поле Message Class задает класс сообщения, в соответствии с которым трактуется младший байт адреса. Транзакция может использовать и двухадресный цикл, при этом в первой фазе адреса по линиям C/BE[3:0]# передается код команды DAC, содержимое бит AD[31:00] соответствует рисунку, а. Во второй фазе адреса по линиям C/BE[3:0]# передается код команды DIM, а все биты AD[31:00] трактуются в зависимости от класса сообщения. Устройство, поддерживающее обмен сообщениями, декодировав команду DIM, проверяет поля идентификаторов получателя на соответствие своему собственному.

В фазе атрибутов (рисунок, б) передается идентификатор источника сообщения (RBN, RDN и RFN), тег сообщения (Tag), 12-битный счетчик байтов (UBC и LBC) идополнительные биты-признаки. Бит IR (Initial Request) является признаком начала сообщения, которое может быть разорвано на несколько частей инициатором, получателем или промежуточными мостами (во всех последующих частях бит обнулен). Бит RO (Relaxed Ordering) указывает на возможность неупорядоченной доставки данного сообщения по отношению к другим сообщениям и записям в память, распространяемым в том же направлении (порядок доставки фрагментов данного сообщения сохраняется всегда).

Тело сообщения, передаваемое в фазах данных, может иметь длину до 4096 байт (предел обусловлен 12-битным счетчиком длины). Содержимое тела определяется классом сообщения; класс 0 отдается на использование по воле производителя.

Сообщения с явной маршрутизацией маршрутизируются мостами на основе номера шины получателя. Проблемы передачи могут возникать только на главных мостах: если в системе имеется несколько главных мостов, то архитектурная связь между ними может быть очень сложной (например, через магистрали контроллера памяти). Передача сообщений с шины на шину через главные мосты желательна (это проще, чем передача транзакций всех типов), но не строго обязательна. Поддержка этой передачи дает больше свободы пользователю (не приходится при расстановке устройств принимать во внимание всю топологию шин). Сообщения с неявной маршрутизацией передаются только по направлению к хосту.

Поддержка DIM для устройств PCI-X необязательна; мосты PCI-X Mode 2 обязаны поддерживать DIM. Если сообщение DIM адресуется к устройству, находящемуся на шине, работающей в стандартном режиме PCI (или путь к нему ведет через PCI), мост либо просто аннулирует это сообщение (если SD = 1), либо отвергает транзакцию (Target Abort, если SD = 0).

Еще статьи...

Подкатегории

-

Протокол, команды и транзакции шин PCI и PCI-X

- Кол-во материалов:

- 12

-

Общая информация

- Кол-во материалов:

- 4

-

Электрический интерфейс и конструктивы для шин PCI

- Кол-во материалов:

- 8

-

Конфигурирование и BIOS устройств PCI и PCI-X

- Кол-во материалов:

- 10

-

Мосты PCI и PCI-X

- Кол-во материалов:

- 10

-

Прерывания PCI: INTx#, PME#, MSI и SERR#

- Кол-во материалов:

- 7