Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

bloody макросы валорант актуальны во все времена.

PCI и PCI-X

Шины PCI и PCI-X

Сигнализация событий управления энергопотреблением — PME#

Линия PME#, введенная в PCI 2.0, служит для сигнализации в системе управления энергопотреблением PM (Power Management): смены состояния устройств, генерации пробуждения системы по событию. Эта линия электрически доступна всем устройствам PCI; как и линии INTx#, PME# никак не обрабатывается мостами, а лишь доводится до всех абонентов. Логика сигнализации аналогична INTx#: устройство сигнализирует о событии, замыкая линию PME# на «землю», таким образом, сигналы о событиях логически собираются по функции ИЛИ. Обработчик этого прерывания может выявить устройство, подавшее сигнал, путем программных обращений к конфигурационным регистрам всех устройств, способных к генерации этого сигнала. Устройства (функции), имеющие отношение к управлению энергопотреблением, имеют в конфигурационном пространстве структуру с идентификатором Capability ID = 01 и набор регистров:

- PMC (Power Management Capabilities) — регистр возможностей PM: версия спецификации, какие состояния поддерживаются, в состояниях возможна генерация PME#, нужен ли сигнал CLK для генерации PME#, каково потребление по линии 3,3VAux;

- PMCSR (Power Management Control/Status Register) — регистр управления и состояния PM: признак введения PME#, его сброс и разрешение; состояние PM, управление данными, выводимыми через регистр Data;

- Data — регистр (необязательный), через который может выводиться, например, информация о потребляемой мощности;

- PMCSR_BSE (Bridge Support Extensions) — регистр расширенного управления мостом: признак поддержки мостом управления вторичной шиной в зависимости от состояния PM; состояние вторичной шины при переходе в состояние потребления D3 (останов синхронизации или еще и снятие питания).

Подробности управления энергопотреблением в PCI и форматы соответствующих конфигурационных регистров приведены в PCI PM 1.1.

Транслирование транзакций и буферизация

Транслирование транзакций — довольно сложная задача моста, и от способа ее решения зависит производительность системы в целом. Какие именно транзакции следует транслировать с одного интерфейса на другой, решает вышеописанная часть моста, занимающаяся маршрутизацией. При транслировании транзакции мост, как целевое устройство PCI, сразу отвечает ее инициатору, независимо от того, что происходит на другой стороне. Это позволяет мосту, как любому устройству PCI, соблюдать ограничения на время отклика и выполнения транзакций. Далее, мост запрашивает управление шиной на противоположной стороне и, получив управление, проводит эту транзакцию от своего имени. Если транслируется транзакция чтения, то мост должен принять ее результаты, чтобы далее переслать их истинному инициатору транзакции. Этот общий сценарий для различных команд реализуется по-разному, но «при всем богатстве выбора» у моста PCI есть всего два варианта ответа инициатору:

- отложить транзакцию, ответив условием Retry. Этот вариант называется отложенной транзакцией (delayed transaction); он заставит инициатора через некоторое время повторить попытку данной транзакции. За это время мост должен «провернуть» заказанную транзакцию на другой стороне интерфейса;

- сделать вид, что транзакция успешно завершена. Такой вариант, называемый отправленной записью (posted write), возможен только для операций записи в память. Реальная запись произойдет позже, когда мост сумеет получить управление шиной на противоположном интерфейсе.

Мост PCI-X для транзакций, транслируемых с шины, работающей в режиме PCI-X, должен вместо откладывания транзакции выполнять ее расщепление.

Чтобы ускорить выполнение транзакций, пришедших с первичной шины, мосту выгодно парковать вторичную шину на самого себя: если вторичная шина свободна, при трансляции транзакции мост не будет терять время на захват шины.

Программная генерация конфигурационных и специальных циклов

Поскольку конфигурационное пространство PCI обособлено, в главный мост приходится вводить специальный механизм доступа к нему командами процессора, инструкции которого «умеют» обращаться только к памяти или вводу-выводу. Этот же механизм используется и для генерации специальных циклов. Для PC-совместимых компьютеров предусмотрено два механизма, из которых в спецификации PCI 2.2 оставлен только первый (Configuration Mechanism #1) как более прозрачный. Номер механизма, которым пользуется конкретная системная плата, можно узнать путем вызова PCI BIOS. Для доступа к расширенному конфигурационному пространству устройств PCI-X эти механизмы непригодны (доступ к нему возможен только через прямое отображение на память).

Конфигурационные циклы адресуются к конкретному устройству (микросхеме PCI), расположенному на шине с известным номером. Декодированием номера шины и устройства, для которого должен быть сформирован сигнал выборки IDSEL (единичное значение), занимаются мосты. Номер функции и адрес регистра декодируется самим устройством.

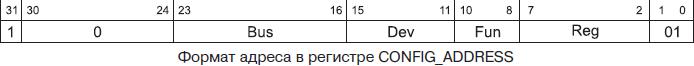

Для работы механизма № 1 в пространстве ввода-вывода зарезервированы 32-битные порты с адресами 0CF8h и 0CFCh, входящие в главный мост. Для обращения к конфигурационному пространству в порт CONFIG_ADDRESS (RW, адрес CF8h) заносят 32-разрядный адрес, декодируемый в соответствии с рисунком ниже. После занесения адреса обращением к порту CONFIG_DATA (RW, адрес CFCh) можно прочитать или записать содержимое требуемого конфигурационного регистра. В регистре CONFIG_ADDRESS бит 31 является разрешением формирования конфигурационных и специальных циклов. В зависимости от номера шины, указанного в этом регистре, главный мост генерирует конфигурационные циклы одного из двух типов:

- для обращения к устройству, находящемуся на нулевой шине (подключенной к главному мосту), используется цикл типа 0. В этом цикле в фазе адреса на линии AD[31:11] мост помещает позиционный код выбора устройства, на AD[10:8] — номер функции, на AD[7:2] — адрес регистра, а биты 1:0 = 00 являются признаком цикла типа 0. В PCI-X в фазе адреса на линии AD[15:11] помещается номер устройства; расширенное конфигурационное пространство через данный механизм не доступно;

- для обращения к устройству, находящемуся на ненулевой шине, используется цикл типа 1. Здесь главный мост передает всю адресную информацию из CONGIG_ADDRESS (номер шины, устройства, функции и регистра) на нулевую шину PCI, обнуляя старшие биты (31:24) и устанавливая в битах 1:0 признак типа «01».

Специальный цикл генерируется при записи в CONFIG_DATA, когда в регистре CONGIG_ADDRESS все биты [15:8], единичные, а биты [7:0] — нулевые; номер шины, на которой формируется цикл, задается битами [23:16]. В специальном цикле ад ресная информация не передается (он широковещательный), но путем задания номера шины можно управлять его распространением. Если хост генерирует специальный цикл, указав нулевой адрес шины, то этот цикл будет выполнен только на главной шине и всеми остальными мостами распространяться не будет. Если указан ненулевой адрес шины, то главный мост сформирует цикл конфигурационной записи типа 1, который в специальный цикл будет преобразован только мостом на шине назначения. Специальный цикл, генерируемый ведущим устройством шины, действует только на шине этого устройства и не распространяется через мосты. Если требуется сгенерировать этот цикл на другой шине, то ведущее устройство может это сделать посредством записей в регистры CONGIG_ADDRESS и CONFIG_DATA.

Для работы устаревшего и неудобного механизма № 2 в пространстве ввода-вывода зарезервированы два 8-битных порта с адресами 0CF8h и 0CFAh, входящие в главный мост. Этот механизм использует отображение конфигурационного пространства устройств PCI на область C000–CFFF пространства ввода-вывода. Поскольку этой области (4096 портов) недостаточно для отображения конфигурационного пространства всех устройств всех шин PCI, формирование адреса выполняется весьма замысловатым образом. В регистре CSE (Configuration Space Enable) с адресом 0CF8h биты 7:4 являются ключом разрешения отображения, а биты [3:1] несут номер функции, к пространству которой адресуются обращения. Бит 0 (SCE — Special Cycle Enable) при единичном значении вместо конфигурационных циклов вызывает формирование специального цикла. При нулевом ключе область портов C000–CFFFh остается нормальной частью пространства вводавывода, а при ненулевом на нее отображаются конфигурационные пространства указанных функций 16 возможных устройств2. При обращении к конфигурационному пространству устройств нулевой шины чтение или запись двойного слова в порт по адресу C000–CFFCh генерирует конфигурационный цикл, в котором из адреса порта биты [2:7] поступают на шину AD[2:7] как индекс регистра конфигурационного пространства, а биты [11:8] декодируются в позиционный код выбора устройства (линии IDSEL) на линиях AD[31:16]. Номер функции на линии AD[10:8] поступает из регистра CSE, линии AD[1:0] нулевые. Для обращения к устройствам ненулевой шины служит регистр перенаправления (Forward Register) с адресом 0CFAh, в который помещают номер шины (по сбросу этот регистр обнуляется). Если номер шины ненулевой, то генерируется цикл типа 1, в котором номер функции поступает из регистра CSE, младшие 4 бита номера устройства поступают с битов адреса (AD15 = 0), а номер шины — из регистра перенаправления (биты AD[1:0] = 01 и AD[31:24] = 0 формируются аппаратно).

Для генерации специального цикла по этому механизму в регистре CSE устанавливается ненулевой ключ, номер функции 111 и SCE = 1, после чего выполняется запись по адресу порта CF00h. В зависимости от содержимого регистра перенаправления будет сгенерирован специальный цикл или конфигурационный цикл типа 1, который на целевой шине будет преобразован в специальный.

Инициализация и определение режима работы шины PCI-X

Каждый сегмент PCI-X (физическая шина) должен работать в самом прогрессивном режиме, доступном всем его абонентам, включая и главный для этой шины мост. В стандартной шине PCI «прогрессивность» определяется только допустимой тактовой частотой (33 или 66 МГц), и свои способности карта сообщает по контакту B49 (M66EN, см. выше). В шине PCI-X появляются новые возможности: поддержка собственно протокола PCI-X (Mode 1 в терминах PCI-X 2.0) и ускоренных передач (Mode 2). Эти возможности карта сообщает через контакт B38 (PCIXCAP), который может быть подключен к шине GND через резистор определенного номинала или оставаться неподключенным (NC), как указано в первой таблице). Номиналы резисторов выбраны так, что мост может определить возможности карт в многослотовых шинах, когда цепи PCIXCAP всех карт соединяются параллельно (кроме резисторов на картах имеются и конденсаторы). Мост, которому подчиняется данная шина, проверяет состояние линий M66EN и PCIXCAP по началу сигнала сброса. В соответствии с увиденными возможностями (они будут соответствовать самому слабому абоненту) мост выбирает режим работы шины. Этот режим доводится до всех абонентов с помошью шаблона инициализации (PCI-X Initialization Pattern) — уровней сигналов PERR#, DEVSEL#, STOP# и TRDY# в момент окончания сигнала RST# (по его нарастающему фронту). К этому моменту на слоты уже подается соответствующее напряжение +VI/O. Возможные режимы шины и их шаблоны инициализации приведены во второй таблице.

Таблица №1

| Соединение на карте для контактов | Способности карты расширения | |

| B49 (M66EN) | B38 (PCIXCAP) | |

| GND | GND | PCI 33 МГц |

| NC | GND | PCI 66 МГц |

| GND или NC | GND через R1 | PCI-X 66 |

| GND или NC | NC | PCI-X 133 |

| GND или NC | GND через R2 | PCI-X 266 |

| GND или NC | GND через R3 | PCI-X 533 |

Таблица №2

| Сигнал | Режим шины (протокол) | Частота, МГц |

Контроль достоверности | |||

| PERR# | DEVSEL# | STOP# | TRDY# | |||

| H | H | H | H | PCI | 0-33 | Четность |

| H | H | H | H | PCI | 33-66 | Четность |

| H | H | H | L | PCI-X Mode1 | 50-66 | Четность |

| H | H | L | H | PCI-X Mode1 | 66-100 | Четность |

| H | H | L | L | PCI-X Mode1 | 100-133 | Четность |

| H | L | H | H | PCI-X Mode1 | Резерв | ECC |

| H | L | H | L | PCI-X Mode1 | 50-66 | ECC |

| H | L | L | H | PCI-X Mode1 | 66-100 | ECC |

| H | L | L | L | PCI-X Mode1 | 100-133 | ECC |

| L | H | H | H | PCI-X266 Mode2 | Резерв | ECC |

| L | H | H | L | PCI-X266 Mode2 | 50-66 | ECC |

| L | H | L | H | PCI-X266 Mode2 | 66-100 | ECC |

| L | H | L | L | PCI-X266 Mode2 | 100-133 | ECC |

| L | L | H | H | PCI-X266 Mode2 | Резерв | ECC |

| L | L | H | L | PCI-X266 Mode2 | 50-66 | ECC |

| L | L | L | H | PCI-X266 Mode2 | 66-100 | ECC |

| L | L | L | L | PCI-X266 Mode2 | 100-133 | ECC |

Особенности передачи данных в PCI-X 2.0

В PCI-X 2.0 вдобавок к вышеописанным изменениям протокола появился новый режим Mode 2, отличающийся ускорением блочной записи в память и применением ECC-контроля. Этот режим возможен только при низком (1,5 В) напряжении питания интерфейсных схем. Режим Mode 2 имеет следующие особенности:

- во всех транзакциях на 1 такт увеличено время декодирования адреса целевым устройством — задержки его ответа сигналом DEVSEL# на обращенную к нему команду. Этого лишнего такта требует ECC-контроль (устройство проверяет достоверность адреса и команды). По той же причине минимальное время покоя шины между транзакциями увеличено с 1 до 2 тактов;

- в транзакциях пакетной записи в память (команда Memory Write Block) используется удвоенная или учетверенная скорость передачи данных по отношению к тактовой частоте. В этих транзакциях сигналы BEx# используются для синхронизации от источника данных (по прямому назначению они не используются, поскольку подразумевается обязательное разрешение всех байтов). Каждая передача данных (32, 64 или 16 бит) сопровождается стробами, в качестве которых используются сигналы BEx#. Пары линий BE[1:0]# и BE[3:2]# передают дифференциальные стробирующие сигналы для линий данных AD[15:0] и AD[31:16] соответственно. В одном такте шины может быть две или четыре подфазы данных (data subphase), этим и обеспечиваются режимы PCI-X266 и PCI-X533 при частоте шины 133 МГц. Поскольку все управляющие сигналы синхронизируются по сигналу общей синхронизации (CLK), гранулярность передач становится равной двум или четырем подфазам данных. Для 32-разрядной шины это означает, что в транзакциях можно передавать (а также останавливать и приостанавливать передачи) данные порциями, кратными 8 или 16 байтам.

В 64-битном варианте шины линии AD[63:32] используются только в фазах данных; для адреса (даже 64-битного) и атрибутов используется только 32-битная шина.

Для устройств, работающих в Mode 2, вводится возможность использования 16-битной шины. При этом фазы адреса и атрибутов занимают по два такта, а фазы данных идут всегда парами (обеспечивая обычную гранулярность). В шине AD используются линии AD[16:31], по которым в первой фазе пары передаются биты [0:15], а во второй — [16:31]. По линиям C/BE[2:3]# в первой фазе передаются биты C/BE[0:1]#, а во второй — C/BE[2:3]#. Для ECC-контроля используются линии ECC[2:5], по которым в первой фазе передаются биты ECC[0, 1, 6] и специальный бит контроля E16, а во второй — ECC[2, 3, 4, 5]. 16-битная шина предназначена только для встроенных применений (слоты и карты расширения не предусматриваются).

Еще статьи...

Подкатегории

-

Протокол, команды и транзакции шин PCI и PCI-X

- Кол-во материалов:

- 12

-

Общая информация

- Кол-во материалов:

- 4

-

Электрический интерфейс и конструктивы для шин PCI

- Кол-во материалов:

- 8

-

Конфигурирование и BIOS устройств PCI и PCI-X

- Кол-во материалов:

- 10

-

Мосты PCI и PCI-X

- Кол-во материалов:

- 10

-

Прерывания PCI: INTx#, PME#, MSI и SERR#

- Кол-во материалов:

- 7