Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

Детальная информация купить оборудование для ресторана у нас.

PCI и PCI-X

Шины PCI и PCI-X

PCI в инструментальных системах: cPCI и PXI

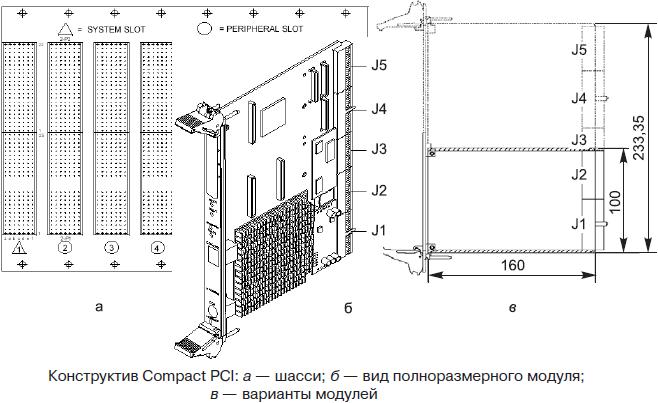

Для устройств промышленного назначения в начале 1995 года был принят стандарт Compact PCI. Шина Compact PCI (cPCI) разрабатывалась на основе спецификации PCI 2.1. Этот стандарт принят Организацией производителей промышленных компьютеров PCIMG (PCI Industrial Computer Manufacturers Group). Шина отличается поддержкой большого количества слотов: 8 против 4 в обычной PCI. Как и PCI, шина поддерживает 32-битный и 64-битный обмен. Шина обладает всеми возможностями автоконфигурирования, присущими PCI. Кроме того, шина дает возможность программного прочтения «географического адреса» модуля. Географическая адресация дает дополнительную возможность идентификации физического местоположения модуля (хотя его можно определить и по номерам шины и устройства, пользуясь стандартными конфигурационными функциями PCI). Конструктивно платы Compact PCI представляют собой еврокарты высотой 3U (100×160 мм) с двумя коннекторами (J1 и J2) или 6U (233,35×160 мм) с 4–5 коннекторами (J1…J5). На шасси разъемы обозначаются P1…P5; платы (модули) устанавливаются с шагом 20,32 мм (0,8 дюйма). Одно посадочное место (слот), как правило крайнее левое, отводится под системный модуль, остальные — под периферийные. В системный слот устанавливается контроллер шины, на который возлагаются функции арбитража и синхронизации. На его коннекторе шиной используется большее число контактов, чем на остальных. Вид шасси и модулей Compact PCI приведен на рисунке, на рисунке видно символическое обозначение места контроллера (номер системного слота — в треугольнике, периферийных — в круге). На шасси может быть несколько сегментов cPCI — независимых шин; если требуется, связь между ними организуется через модули-мосты, устанавливаемые в слоты. В каждом сегменте должен быть собственный контроллер шины.

Коннекторы — 7-рядные экранированные штырьковые разъемы с шагом 2 мм между контактами, на кросс-плате — вилка, на модулях — розетки. Поскольку модули (и разъемы) обычно устанавливаются вертикально, ряды удобнее назвать колонками, что и подразумевается ниже. Из 7 колонок контактов (z, a, b, c, d, e, f) только 5 (a–e) используются для сигнальных цепей, а колонки z и f — только для экрана (соединяются с шиной GND)1. Контакты коннекторов имеют разную длину: более длинные контакты цепей питания при установке модуля соединяются раньше, а при вынимании разъединяются позже, чем сигнальные. Такое решение позволяет производить «горячую» замену модулей. Собственно шина использует только коннекторы J1 и J2, плотно примыкающие друг к другу (они могут выглядеть как единый 47-позиционный разъем). Контакты J1 используются для сигналов 32-битной шины PCI; периферийная 32-битная плата может и не иметь разъема J2. Ряды 12– 14 используются как ключи для вариантов с уровнями сигналов 5В/3,3В. Здесь возможны универсальные платы, но не допускаются универсальные шасси. Разъем J2 используется по-разному: системный контроллер использует его для сигналов арбитража и синхронизации, разводящихся по периферийным слотам радиально. На периферийных платах он может и отсутствовать. В 64-разрядных системах J2 используется для расширения шины; в 32-разрядных он может использоваться для сигналов ввода-вывода, разводящихся через шасси. На этот же разъем выведены сигналы географической адресации (которые можно и не использовать). Назначение контактов разъемов J1 и J2 Compact PCI версии 2.1 приведено в таблице ниже. Разъемы J3…J5 отводятся для прикладного использования. Конструкция коннекторов позволяет применять для них специфические модификации (например, с разделяющим экраном и механическими ключами). В шине предусматривается наличие независимых источников питания + 5 В, + 3,3 В и ± 12 В.

| Разъем, контакт | № | Ряд | ||||

| a | b | c | d | e | ||

| J2 | 22 | GA4 | GA3 | GA2 | GA1 | GA0 |

| 21 | CLK6 | GND | RSV | RSV | RSV | |

| 20 | CLK5 | GND | RSV | GND | RSV | |

| 19 | GND | GND | RSV | RSV | RSV | |

| 18 | BRSVP2A18 | BRSVP2B18 | BRSVP2C18 | GND | BRSVP2E18 | |

| 17 | BRSVP2A17 | GND | PRST# | REQ6# | GNT6# | |

| 16 | BRSVP2A16 | BRSVP2B16 | DEG# | GND | BRSVP2E16 | |

| 15 | BRSVP2A15 | GND | FAL# | REQ5# | GNT5# | |

| 14 | AD35 | AD34 | AD33 | GND | AD32 | |

| 13 | AD38 | GND | V(I/O) | AD37 | AD36 | |

| 12 | AD42 | AD41 | AD40 | GND | AD39 | |

| 11 | AD45 | GND | V(I/O) | AD44 | AD43 | |

| 10 | AD49 | AD48 | AD47 | GND | AD46 | |

| 9 | AD52 | GND | V(I/O) | AD51 | AD50 | |

| 8 | AD56 | AD55 | AD54 | GND | AD53 | |

| 7 | AD59 | GND | V(I/O) | AD58 | AD57 | |

| 6 | AD63 | AD62 | AD61 | GND | AD60 | |

| 5 | C/BE5# | GND | V(I/O) | C/BE4# | PAR64 | |

| 4 | V(I/O) | BRSVP2B4 | C/BE7# | GND | C/BE6# | |

| 3 | CLK4 | GND | GNT3# | REQ4# | GNT4# | |

| 2 | CLK2 | CLK3 | SYSEN# | GNT2# | REQ3# | |

| 1 | CLK1 | GND | REQ1# | GNT1# | REQ2# | |

| J1 | 25 | 5V | REQ64# | ENUM# | 3.3V | 5V |

| 24 | AD1 | 5V | V(I/O) | AD0 | ACK64# | |

| 23 | 3.3V | AD4 | AD3 | 5V | AD2 | |

| 22 | AD7 | GND | 3.3V | AD6 | AD5 | |

| 21 | 3.3V | AD9 | AD8 | M66EN | C/BE0# | |

| 20 |

AD12 |

GND | V(I/O) | AD11 | AD10 | |

| 19 | 3.3V | AD15 | AD14 | GND | AD13 | |

| 18 | SERR# | GND | 3.3V | PAR | C/BE1# | |

| 17 | 3.3V | IPMB_SCL (SDONE)1 | IPMB_SDA (SBO#)1 | GND | PERR# | |

| 16 | DEVSEL# | GND | V(I/O) | STOP# | LOCK# | |

| 15 | 3.3V | FRAME# | IRDY# | BD_SEL# (GND)2 | TRDY# | |

| 12-14 | Зона ключа | - | - | - | - | |

| 11 | AD18 | AD17 | AD16 | GND | C/BE2# | |

| 10 | AD21 | GND | 3.3V | AD20 | AD19 | |

| 9 | C/BE3# | IDSEL | AD23 | GND | AD22 | |

| 8 | AD26 | GND | V(I/O) | AD25 | AD24 | |

| 7 | AD30 | AD29 | AD28 | GND | AD27 | |

| 6 | REQ# | GND | 3.3V | CLK | AD31 | |

| 5 | BRSVP1A5 | BRSVP1B5 | RST# | GND | GNT# | |

| 4 | IPMB_PWR (BRSVP1A4)1 | HEALTHY# (GND)1 | V(I/O) | INTP | INTS | |

| 3 | INTA# | INTB# | INTC# | 5V | INTD# | |

| 2 | TCK | 5V | TMS | TDO | TDI | |

| 1 | 5V | -12V | TRST# | +12V | 5V | |

1 — Назначение в скобках — для старых версий.

2 — На системном слоте — GND.

В основном сигналы Compact PCI совпадают с сигналами обычной шины PCI, назначение специфических сигналов приведено в следующей таблице.

| Сигнал | Назначение |

| BD_SEL# | Сигнал от модуля о том, что он установлен в слот и питание подано (подается через один из укороченных контактов, который соединяется после всех основных) |

| BRSVxxxx | Зарезервированные на будущее сигналы, шинно разведенные по слотам; xxxx обозначает позиционный номер контакта (BRSVP1A4 — на контакте A4 разъема P1) |

| CLK[0:6], GNT#[0:6], REQ#[0:6] | Сигналы, радиально разводящиеся от разъема J2 системного слота к периферийным (сигналы CLK0, GNT0# и REQ0# расположены на местах CLK, GNT# и REQ# разъема J1) |

| DEG# | Предупреждение о деградации питания |

| ENUM# | Все аппаратные модули установлены, можно производить нумерацию и конфигурирование устройств |

| FAL# | Отказ питания |

| GA0-GA4 | Географический адрес. Коммутацией на «землю» для каждого слота задается его двоичный географический адрес на шасси |

| SMB_SDA, SMB_SCL, | Сигналы шины SMBus (только на системном слоте) |

| SMB_ALERT# | Сигнал прерывания по шине SMBus |

| HEALTHY# | Сигнал от модуля, что он получает нормальное питание (PwrGood) и сигнал его сброса снят |

| INTP, INTS | Прерывания от первичного и вторичного контроллеров IDE |

| IPMB_PWR, | Батарейное питание шины IPMB (Independent Platform Management Bus, независимая последовательная шина управления платформой) |

| IPMB_SCL, IPMB_SDA | Синхронизация и данные шины IPMB |

| PRST# | Push Button Reset, сигнал от кнопки «Сброс» |

| RSV | Резерв на будущее |

| SYSEN# | Идентификация системного слота (на системном слоте контакт заземлен, что позволяет модулю опознать установку в это место) |

| UNC | Не подключен |

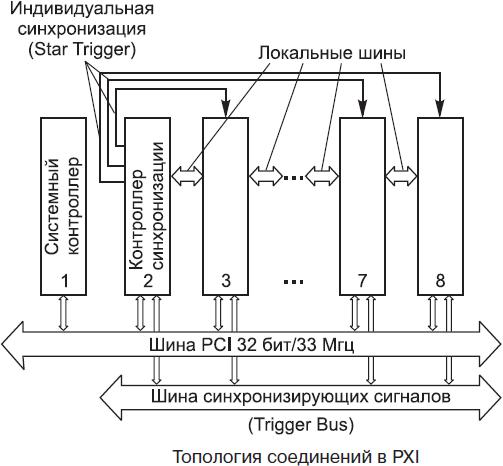

На базе шины Compact PCI фирмой National Instruments разработана спецификация PXI (PCI eXtensions for Instrumentation — расширение PCI для инструментальных систем) в тех же конструктивах. По сравнению с cPCI в PXI более жестко определяется местоположение модулей. На шасси левый слот отводится для контроллера шины, следующий за ним — для контроллера синхронизации (его номер пишут в ромбе), остальные — для периферийных модулей. При необходимости контроллер может расширяться влево, занимая дополнительные слоты, разъемы которых не связаны с общей шиной.

В шине PXI часть контактов J2/P2, определенных в Compact PCI как резервные, предназначаются для организации дополнительных локальных шин и синхронизации. Резервными остались только PXI_BRSVA15 и PXI_BRSVB4, разведенные по всем слотам шасси. Топологию соединений на шасси PXI иллюстрирует следующий рисунок.

В инструментальных системах зачастую требуется синхронизация разных модулей, для этого в PXI имеются специальные сигнальные линии. Шина синхронизирующих сигналов Trigger Bus (8 линий) PXI_TRIG[0:7] объединяет все слоты одного сегмента PXI, за исключением системного. Кроме того, имеются 13 линий индивидуальной синхронизации (Star Trigger), звездообразно соединяющих слот контроллера синхронизации с остальными периферийными слотами всего шасси (может распространяться и на два сегмента PXI). Каждая из линий PXI_STAR[0:12] слота контроллера синхронизации соединяется с линией PXI_STAR своего слота. Разводка линий обеспечивает идентичность задержек, вносимых ими в распространение сигнала между слотом контроллера синхронизации и периферийными слотами. Линии PXI_TRIG[0:7] и PXI_STAR[0:12] могут использоваться двояко: как для подачи команд запуска модулям от контроллера синхронизации, так и для сообщения модулями своего состояния (зависит от приложения шасси). Для прецизионной синхронизации имеется сигнал опорной частоты 10 МГц PXI_CLK10, который шасси синхронно (со сдвигом не более 1 нс) доставляет ко всем слотам. Для каждого слота предоставляется отдельный выход буфера; источником сигнала может быть как шасси, так и контроллер синхронизации (через сигнал PXI_CLK10_IN).

Локальные шины в PXI предназначены для связи соседних пар слотов. Локальные шины объединяют смежные слоты попарно (исключая слот системного контроллера), образуя цепочку устройств (daisy chain). Каждая локальная шина имеет 13 линий, соединяющих цепи PXI_LBR[0:12] левого слота с цепями PXI_LBL[0:12] правого слота пары. Линии могут использоваться как для цифровых, так и аналоговых (до 48 В, 200 мА) сигналов. Цепи PXI_LBR[0:12] последнего (самого правого) слота могут выводиться на внешний разъем шасси. Для слота контроллера синхронизации линии PXI_LBL[0:12] недоступны — их контакты заняты звездообразными сигналами синхронизации.

Кроме механических и электрических характеристик PXI определяет ПО модулей: основной ОС считается Windows NT/2000/9x, и модули должны поставляться с соответствующими драйверами. Это экономит время, необходимое для системной интеграции. В качестве средств разработки ПО предлагается использовать пакеты LabVIEW, LabWindows/CVI фирмы National Instruments; Visual Basic, Visual C/C++ от Microsoft и Turbo C/C++ от Borland. Модули PXI совместимы с шиной Compact PCI, а модули Compact PCI — с шиной PXI. Однако все преимущества спецификации реализуются только при установке модулей PXI в шину PXI.

Таблица. Разъем J2/P2 PXI для периферийного слота

| Контакт | a | b | c | d | e |

| 22 | GA4 | GA3 | GA2 | GA1 | GA0 |

| 21 | PXI_LBR0 | GND | PXI_LBR1 | PXI_LBR2 | PXI_LBR3 |

| 20 | PXI_LBR4 | PXI_LBR5 | PXI_LBL0 | GND | PXI_LBL1 |

| 19 | PXI_LBL2 | GND | PXI_LBL3 | PXI_LBL4 | PXI_LBL5 |

| 18 | PXI_TRIG3 | PXI_TRIG4 | PXI_TRIG5 | GND | PXI_TRIG6 |

| 17 | PXI_TRIG2 | GND | RSV | PXI_STAR | PXI_CLK10 |

| 16 | PXI_TRIG1 | PXI_TRIG0 | RSV | GND | PXI_TRIG7 |

| 15 | PXI_BRSVA15 | GND | RSV | PXI_LBL6 | PXI_LBR6 |

| Ряды 5–14 как у Compact PCI | |||||

| 4 | V(I/O) | PXI_BRSVB4 | C/BE7# | GND | C/BE6# |

| 3 | PXI_LBR7 | GND | PXI_LBR8 | PXI_LBR9 | PXI_LBR10 |

| 2 | PXI_LBR11 | PXI_LBR12 | UNC | PXI_LBL7 | PXI_LBL8 |

| 1 | PXI_LBL9 | GND | PXI_LBL10 | PXI_LBL11 | PXI_LBL12 |

Таблица. Разъем J2/P2 PXI для системного слота

| Контакт | a | b | c | d | e |

| 22 | GA4 | GA3 | GA2 | GA1 | GA0 |

| 21 | CLK6 | GND | RSV | RSV | RSV |

| 20 | CLK5 | GND | RSV | GND | RSV |

| 19 | GND | GND | SMB_SDA | SMB_SCL | SMB_ALERT# |

| 18 | PXI_TRIG4 | PXI_TRIG4 | PXI_TRIG5 | GND | PXI_TRIG6 |

| 17 | PXI_TRIG2 | GND | PRST# | REQ6# | GNT6# |

| 16 | PXI_TRIG1 | PXI_TRIG0 | DEG# | GND | PXI_TRIG7 |

| 15 | PXI_BRSVA15 | GND | FAL# | REQ5# | GNT5# |

| Ряды 5–14 как у Compact PCI | |||||

| 4 | V(I/O) | PXI_BRSVB4 | C/BE7# | GND | C/BE6# |

| 3 | CLK4 | GND | GNT3# | REQ4# | GNT4# |

| 2 | CLK2 | CLK3 | SYSEN# | GNT2# | REQ3# |

| 1 | CLK1 | GND | REQ1# | GNT1# | REQ2# |

Таблица. Разъем J2/P2 PXI для слота контроллера синхронизации

| Контакт | a | b | c | d | e |

| 22 | GA4 | GA3 | GA2 | GA1 | GA0 |

| 21 | PXI_LBR0 | GND | PXI_LBR1 | PXI_LBR2 | PXI_LBR3 |

| 20 | PXI_LBR4 | PXI_LBR5 | PXI_STAR0 | GND | PXI_STAR1 |

| 19 | PXI_STAR2 | GND | PXI_STAR3 | PXI_STAR4 | PXI_STAR5 |

| 18 | PXI_TRIG3 | PXI_TRIG4 | PXI_TRIG5 | GND | PXI_TRIG6 |

| 17 | PXI_TRIG2 | GND | RSV | PXI_CLK10_IN | PXI_CLK10 |

| 16 | PXI_TRIG1 | PXI_TRIG0 | RSV | GND | PXI_TRIG7 |

| 15 | PXI_BRSVA15 | GND | RSV | PXI_STAR6 | PXI_LBR6 |

| Ряды 5–14 как у Compact PCI | |||||

| 4 | V(I/O) | PXI_BRSVB4 | C/BE7# | GND | C/BE6# |

| 3 | GND | PXI_LBR8 | PXI_LBR9 | PXI_LBR10 | - |

| 2 | PXI_LBR12 | UNC | PXI_STAR7 | PXI_STAR8 | - |

| 1 | GND | PXI_STAR10 | PXI_STAR11 | PXI_STAR12 | - |

Организация шин PCI и PCI-X

Шина PCI позволяет объединять равноранговые устройства. Любое устройство шины может выступать как в роли инициатора транзакций (задатчика), так и в роли целевого устройства. Целевое устройство отвечает на транзакции, адресованные к его ресурсам (областям памяти и портам ввода/вывода). Ядро компьютера (центральный процессор и память) для шины PCI также представляется устройством — главным мостом (host bridge). В транзакциях, обращенных к устройствам PCI, инициированных центральным процессором, главный мост является задатчиком. В транзакциях от устройств PCI, обращающихся к ядру (к системной памяти), главный мост является целевым устройством. Право на управление шиной в любой момент времени дается лишь одному устройству данной шины; арбитраж запросов на управление шиной осуществляется централизованным способом. Арбитр, как правило, является частью моста.

Наличие активных устройств (помимо ЦП) позволяет выполнять в компьютере параллельно несколько операций обмена: одновременно с обращениями процессора могут выполняться транзакции от мастеров шины PCI. Эта параллельность — PCI Concurrency — возможна лишь для обменов по непересекающимся путям. Одновременный доступ нескольких инициаторов к одному ресурсу (как правило, к системной памяти) требует довольно сложной организации контроллера этого ресурса, но ради повышения суммарной эффективности системы на эти усложнения приходится идти. В системе с несколькими шинами PCI возможна параллельная работа устройств-мастеров на разных шинах — PCI Peer Concurrency. Однако если они обращаются к одному ресурсу (системной памяти), то какие-то фазы этих обменов все-таки должны будут выполняться последовательно.

Каждая физическая шина PCI позволяет объединять лишь небольшое число устройств: типовое ограничение по электрическим спецификациям — не более шести устройств на шине. Для увеличения числа подключаемых устройств применяют мосты PCI (PCI-to-PCI Bridge) — устройства PCI с парой интерфейсов, которыми шины объединяются в древовидную структуру. В корне этой структуры находится хост — «хозяин шины», в обязанности которого входит конфигурирование всех устройств, включая и мосты. В роли хоста, как правило, выступает центральный процессор с главным мостом. Мосты позволяют объединять шины PCI и PCI-X с разными характеристиками, а также подключать к PCI/PCI-X иные шины: (E)ISA, MCA, шины блокнотных ПК, PCI Express, Hyper Transport и другие.

Шина PCI/PCI-X имеет несколько вариантов конструктивного оформления, часть из которых при наличии специального контроллера допускают горячую замену устройств:

- шина объединения компонентов на печатной плате (системной плате или карте расширения);

- слотовые разъемы для установки карт расширения (в конструктивах PC и MCA);

- разъемы для малогабаритных карт расширения (Card Bus, Small PCI, Mini PCI);

- модульные конструктивы для промышленных и инструментальных компьютеров (CompactPCI, PXI).

Важной частью шины PCI является система автоматического конфигурирования; конфигурирование выполняется каждый раз при включении питания и инициализации системы. Специальное конфигурационное ПО позволяет обнаружить и идентифицировать все установленные устройства, а также выяснить их потребности в ресурсах (областях памяти, адресах ввода/вывода, прерываниях). Спецификация PCI требует от устройств способности перемещать все занимаемые ресурсы (области в пространстве памяти и ввода/вывода) в пределах доступного адресного пространства. Это позволяет обеспечить бесконфликтное распределение ресурсов для множества устройств. Одно и то же функциональное устройство может быть сконфигурировано по-разному, отображая свои операционные регистры либо на пространство памяти, либо на пространство адресов ввода/вывода. Драйвер может определить текущую настройку, прочитав содержимое регистра базового адреса устройства. Драйвер также может определить номер запроса на прерывание, который используется устройством. Для поддержки конфигурирования устройств существует специальный набор функций PCI BIOS.

Команды шины PCI

Команды PCI определяют направление и тип транзакций, а также адресное пространство, к которому они относятся. Набор команд шины PCI включает следующие:

- I/O Read, I/O Write — команды чтения и записи ввода/вывода, служат для обращения к пространству портов;

- Memory Read, Memory Write — команды чтения и записи памяти, служат для выполнения коротких (как правило, непакетных) транзакций. Их прямое назначение — обращение к отображенным на память устройствам ввода/вывода. Для «настоящей» памяти, допускающей предвыборки, предназначены команды чтения строк, множественного чтения и записи с инвалидацией;

- Memory-Read Line — чтение строки памяти, применяется, когда в транзакции планируется чтение до конца строки кэша. Выделение данного типа чтения позволяет повысить производительность обмена с памятью;

- Multiple Memory Read — множественное чтение памяти, используется для транзакций, затрагивающих более одной строки кэш-памяти. Использование данного типа транзакций позволяет контроллеру памяти выполнять упреждающую выборку строк, что дает дополнительный выигрыш производительности;

- Memory Write and Invalidate (MVI) — запись с инвалидацией, применяется к целым строкам кэша, причем все байты во всех фазах должны быть разрешены. Эта операция заставляет контроллер кэш-памяти очищать «грязные» строки кэша, соответствующие записываемой области, без их выгрузки в ОЗУ, что экономит время. Инициатор, вводящий эту команду, должен знать размер строки кэша в данной системе (для этого у него есть специальный регистр в конфигурационном пространстве);

- Dual Address Cycle (DAC) — двухадресный цикл, позволяет по 32-битной шине обращаться к устройствам с 64-битной адресацией. В этом случае младшие 32 бита адреса передаются одновременно с данной командой, а далее следует обычный цикл, определяющий команду обмена и несущий старшие 32 бита адреса. Шина PCI допускает 64-битную адресацию как памяти, так и портов ввода/вывода (последнее для систем на x86 бесполезно, но PCI существует и на других платформах);

- Configuration Read, Configuration Write — команды конфигурационного чтения и записи, адресуются к конфигурационному пространству устройств. Обращение производится только выровненными двойными словами, биты AD[1:0] используются для идентификации типа цикла (см. ниже). Для генерации данных команд требуется специальный аппаратно-программный механизм;

- Special Cycle — специальный цикл, отличается от всех других тем, что является широковещательным. Однако ни один агент на него не отвечает, а главный мост или иное устройство, вводящее этот цикл, всегда завершает его способом Master Abort (на него требуется 6 тактов шины). Специальный цикл предназначен для генерации широковещательных сообщений, которые могут читать любые «заинтересованные» агенты шины. Тип сообщения декодируется содержимым линий AD[15:0]; на линиях AD[31:16] могут помещаться данные, передаваемые в сообщении. Фаза адреса в этом цикле обычными устройствами игнорируется, но мосты используют ее информацию для управления распространением сообщения. Сообщения с кодами 0000h, 0001h и 0002h требуются для указания на отключение (сообщение Shutdown), остановку (сообщение Halt) процессора или специфические функции процессора x86, связанные с кэшем и трассировкой. Коды 0003h–FFFFh зарезервированы. Специальный цикл может генерироваться тем же аппаратно-программным механизмом, что и конфигурационные циклы, но со специфическим значением адреса;

- Interrupt Acknowledge (INTA) — команда подтверждения прерывания, предназначена для чтения вектора прерываний. По протоколу она выглядит как команда чтения, неявно адресованная к системному контроллеру прерываний. Здесь в фазе адреса по шине AD полезная информация не передается (BE[3:0]# задают размер вектора), но ее инициатор (главный мост) должен обеспечить стабильность сигналов и корректность бита четности. В x86-архитектуре 8-битный вектор передается в байте 0 по готовности контроллера прерываний (по сигналу TRDY#). Подтверждение прерываний выполняется за один цикл (первый холостой цикл, который процессоры x86 делают в дань совместимости со стариной, мостом подавляется).

Команды кодируются значениями бит C/BE# в фазе адреса (см. таблицу ниже), специфические команды PCI-X рассмотрены в последующих разделах.

| Код C/BE[3:0] | PCI команда | PCI-X команда | Длина | Возможность расщепления |

| 0000 | Interrupt Acknowledge | Interrupt Acknowledge, подтверждение прерывания | DWORD | + |

| 0001 | Special Cycle | Special Cycle, специальный широковещательный цикл | DWORD | - |

| 0010 | I/O Read | I/O Read, чтение ввода/вывода | DWORD | + |

| 0011 | I/O Write | I/O Read, запись ввода/вывода | DWORD | + |

| 0100 | Резерв | Резерв | - | - |

| 0101 | Резерв | Device ID Message (DIM), посылка собщения устройству (PCI-X 2.0) |

Пакет | - |

| 0110 | Memory Read | Memory Read DWORD, одиночное чтение памяти | DWORD | + |

| 0111 | Memory Write | Memory Write, запись памяти | Пакет | - |

| 1000 | Резерв | Alias to Memory Read Block псевдоним чтения блока памяти | Пакет | + |

| 1001 | Резерв | Alias to Memory Write Block, псевдоним записи блока памяти | Пакет | - |

| 1010 | Configuration Read | Configuration Read, конфигурационное чтение | DWORD | + |

| 1011 | Configuration Write | Configuration Write, конфигурационная запись | DWORD | + |

| 1100 | Memory Read Multiple | Split Completion, завершение расщепленной транзакции | Пакет | - |

| 1101 | Dual Address Cycle | Dual Address Cycle (DAC), цикл передачи расширенного адреса памяти | - | - |

| 1110 | Memory Read Line | Memory Read Block, чтение блока памяти | Пакет | + |

| 1111 | Memory Write and Invalidate | Memory Write Block, запись блока памяти | Пакет | - |

Таблица. Декодирование команд шин PCI и PCI-X

В каждой команде шины указывается адрес, относящийся к первой фазе данных пакета. Для каждой последующей фазы данных пакета адрес увеличивается на 4 (следующее двойное слово) или 8 (для 64-битных передач), но в командах обращения к памяти предусматривался и иной порядок.

В шине PCI байты шины AD, несущие реальную информацию, определяются сигналами C/BE[3:0]# в фазах данных. Разрешенные байты могут быть разрозненными; возможны фазы данных, в которых не разрешено ни одного байта. В PCI-X правила разрешения байтов изменились (см. ниже). Сигналами C/BE[3:0]# управляет инициатор, он указывает требуемые байты для каждой фазы данных и не меняет состояние этих сигналов в течение всей этой фазы. В транзакциях чтения байты «заказывает» опять же инициатор; если поведение целевого устройства (источника данных для чтения) зависит от того, какие байты заказаны, то целевое устройство вынуждено растягивать каждую фазу данных. При этом в первом такте каждой фазы данных целевое устройство принимает C/BE[3:0]# и только в последующем такте (а может, и с дополнительным ожиданием) выдает данные чтения.

В отличие от шины ISA на PCI нет динамического изменения разрядности — все устройства должны подключаться к шине 32- или 64-разрядным способом. Если в устройстве PCI применяются функциональные схемы иной разрядности (к примеру, нужно подключить микросхему 8255, имеющую 8-битную шину данных и четыре регистра), то приходится применять схемотехнические методы преобразования, отображающие все регистры на 32-разрядную шину AD. Возможность 16-битных подключений появилась только во второй версии PCI-X.

Для каждого из трех пространств — памяти, портов ввода/вывода и конфигурационных регистров — адресация различна; в специальных циклах адрес игнорируется.

Традиционный контроллер прерываний — PIC

Контроллер прерываний (PIC) 8259A является периферийным устройством, которое связано с процессором через системную шину. По этой шине процессор может обращаться к регистрам контроллера, программируя его режимы и управляя им, а также получать от контроллера 8-битный вектор прерывания, для чего в интерфейсе системной шины процессора имеется специальная команда подтверждения прерывания (INTA). Контроллер 8259A имеет 8 входов запросов от источников и один выход общего запроса. Каждому из входов соответствует свой вектор; программированием регистров контроллера задается номер вектора для входа 0, остальным входам соответствуют последующие номера векторов. Каждый вход может быть программно замаскирован — тогда он не будет вызывать сигнал общего запроса. Контроллер занимает два адреса в пространстве ввода/вывода, программное обращение по этим адресам обеспечивает выполнение следующих функций:

- управление режимами работы контроллера;

- управление приоритетами и масками запросов;

- идентификацию запросов прерывания без вырабатывания общего запроса — обслуживание прерываний по опросу (полинг).

В контроллере имеется три регистра: IRR, IMR и ISR. С каждым входом запроса в контроллере связано по одному биту каждого из этих регистров; бит 0 каждого из этих регистров относится к входу 0, бит 1 — к входу 1, бит 7 — ко входу 7. Регистры имеют следующие назначения:

- IRR (Interrupt Request Register) — регистр запросов прерываний, в котором бит устанавливается при обнаружении сигнала прерывания на соответствующем входе, независимо от маски;

- IMR (Interrupt Mask Register) — регистр масок прерываний. Единичное значение бита означает замаскированность данного входа — по запросу с замаскированного входа общий запрос прерывания не генерируется;

- ISR (Interrupt Service Register) — регистр обслуживаемого прерывания. Во время цикла подтверждения (INTA) в регистре устанавливается бит, соответствующий наиболее приоритетному запросу и, соответственно, формируемому вектору прерывания. В этот же момент обнуляется соответствующий бит запроса в регистре IRR. Бит в ISR обнуляется по получении контроллером команды EOI, а в режиме автоматического подтверждения (по команде AEOI) он обнуляется сразу после передачи вектора прерывания.

Контроллер прерываний позволяет программировать свои входы на чувствительность к уровню или перепаду сигнала:

- чувствительность к уровню (level sensitive) означает, что контроллер прерываний вырабатывает запрос прерывания процессора по факту обнаружения определенного уровня на входе IRQx. Если к моменту завершения обработки этого запроса (после записи команды EOI в регистр контроллера прерываний) контроллер снова обнаруживает активный уровень на том же входе DRQx, то он снова сформирует запрос на прерывание процессора;

- чувствительность к перепаду (edge sensitive) означает, что контроллер прерываний вырабатывает запрос прерывания процессора только по факту обнаружения перепада (на ISA — положительного) на входе IRQx. Повторно запрос по этому входу возможен только по следующему такому же перепаду, то есть сигнал предварительно должен вернуться в исходное состояние.

В любом случае сигнал запроса аппаратного прерывания IRQx должен удерживаться генерирующей его схемой, по крайней мере, до цикла подтверждения прерывания процессором — именно в этот момент PIC определяет самый приоритетный незамаскированный запрос и по нему формирует вектор. Если к этому моменту запрос будет снят, источник прерывания корректно идентифицирован не будет и контроллер сообщит ложный вектор прерывания (spurious interrupt), соответствующий его входу с максимальным номером (IRQ7 для первого контроллера и IRQ15 для второго). Обычно периферийные устройства строят так, что сигнал запроса сбрасывается при обращении программы обслуживания прерывания к соответствующим регистрам адаптера, так что ложных прерываний возникать не должно.

Стандартный PIC позволяет управлять чувствительностью только для всех входов одновременно. В шине ISA и системной периферии (таймеры, контроллер клавиатуры) прерывание сигнализируется положительным перепадом сигнала на линии запроса, так что традиционно контроллеры PIC программируют на чувствительность к перепаду. Более поздние модификации PIC, применяемые в системах с шиной EISA и ISA с поддержкой PnP, а также новые контроллеры APIC при работе в PIC-совместимом режиме позволяют управлять чувствительностью для каждого входа индивидуально.

Один PIC 8259A позволяет обслуживать 8 запросов прерываний; в PC/AT применяется каскадное соединение двух контроллеров, один из которых является ведущим, другой — ведомым. Ведущий контроллер 8259A#1 обслуживает запросы 0, 1, 3–7; его выход подключается к входу запроса прерываний процессора. К его входу 2 подключен ведомый контроллер 8259A#2, который обслуживает запросы 8–15. При этом поддерживается вложенность приоритетов — запросы 8–15 со своим рядом убывающих приоритетов вклиниваются между запросами 1 и 3 ведущего контроллера, приоритеты запросов которого также убывают с ростом номера. В XT каскадирование не применялось и один контроллер 8259A обслуживал все 8 линий запросов.

Контроллер 8259A позволяет работать с запросами в различных режимах:

- Fully Nested Mode — режим полной вложенности приоритетов; каждому входу (уровню) запросов назначается свой приоритет (самый приоритетный — вход 0). В момент подтверждения прерывания контроллер устанавливает в регистре ISR бит, соответствующий самому приоритетному запросу на данный момент (и переданному вектору прерывания), и до его сброса игнорирует последующие запросы с данного входа и менее приоритетные запросы;

- Special Fully Nested Mode — специальный режим полной вложенности, используемый в ведущем контроллере при каскадном соединении. В этом режиме ведущий контроллер не блокирует запрос от входа, к которому подключен ведомый контроллер. Это позволяет ведомому контроллеру сигнализировать о запросе, более приоритетном, чем предыдущий. В конце процедуры обработки ведомому контроллеру посылается неспецифический EOI, после чего считывается его ISR. Если в ISR ни один бит не установлен, то неспецифический EOI посылается и ведущему контроллеру, что позволит ему обслуживать и менее приоритетные входы. Если же в ISR ведомого контроллера есть ненулевые биты, то ведущий контроллер снова подаст общий запрос прерывания, и на его подтверждение ведомый пошлет соответствующий вектор. Упоминаний о проверке на 0 значения ISR вторичного контроллера до подачи EOI первичному применительно к PC автору не встречалось. Очевидно, что в ней нет необходимости, если не используется ротация приоритетов: если у вторичного контроллера есть еще не обслуженные запросы, то они будут обслужены в соответствии со своим приоритетом (до IRQ3…IRQ7);

- Automatic Rotation Mode — режим автоматической ротации приоритетов позволяет организовать равноприоритетное обслуживание всех запросов. В этом режиме уровень, запрос от которого пошел на обслуживание, получает низший приоритет. Ротация приоритетов организуется подачей команд OCW2 с кодом операции 101 или 100;

- Specific Rotation Mode — режим специфицированной ротации: командой OCW2 с кодом операции 111 или 110 указанному уровню устанавливается низший приоритет;

- Poll Mode — режим опроса, в котором общий запрос INTR не вырабатывается. По команде Poll, посылаемой через OCW3, контроллер фиксирует самый проритетный запрос. Последующее считывание из регистра контроллера даст байт, в котором бит 7 указывает на наличие запроса, а в битах [2:0] содержится номер самого приоритетного запроса;

- Normal EOI — нормальный режим завершения, в котором бит ISR сбрасывается явной командой EOI, посылаемой контроллеру в конце исполнения обработчика прерывания. Обычно используется команда неспецифического EOI (код 20h), по которой сбрасывается бит ISR, соответствующий самому приоритетному из обслуживаемых запросов. Возможна команда и специфического EOI, которая сбрасывает в ISR бит, указанный в данной команде. Бит для замаскированного запроса таким способом сброшен быть не может;

- Auto EOI — автоматическая генерация неспецифического EOI контроллером в конце цикла подтверждения прерывания. Этот режим применим лишь в случаях, когда не требуется поддержка вложенности прерываний, и только для ведущего контроллера.

Контроллер 8259A своими 8-битными регистрами приписывается к пространству ввода/вывода и занимает 2 смежных адреса. Обмен с регистрами контроллеров должен производиться только однобайтными операциями ввода/вывода. В современных PC-совместимых компьютерах контроллеры имеют и дополнительные регистры (ELCR). Положение регистров в пространстве ввода/вывода приведено в таблице ниже.

| Адрес 8259A#1 | Адрес 8259A#2 | Назначение | Тип |

| 020h | 0A0h |

Подача команд ICW1, OCW2, OCW3 | WO |

| Чтение регистров IRR, ISR или данных полинга (в зависимости от OCW3) | RO |

||

| 021h |

0A1h |

Подача команд ICW2, ICW3, ICW4, OCW1 |

WO |

| Обращение к регистру IMR |

RW |

||

| 4D0h | 4D1h | Обращение к регистру ELCR |

RW |

Контроллер имеет два режима работы: режим инициализации и операционный. После сброса контроллер инициализируется последовательностью команд ICW1– ICW4 (Initialization Command Words) длиной до 4 байт, после чего переходит в операционный режим. В операционном режиме (Operation Mode)контроллер воспринимает команды управления OCW1–OCW3 (Operation Control Words). В операционном режиме он может быть и реинициализирован, признаком начала инициализации является единичное значение бита 4 в байте, записываемом по адресу 020h (0A0h). Назначение команд и регистров контроллера прерываний приведено ниже

Команда инициализации ICW1 (запись по адресу 020h или 0A0h) служит для конфигурирования контроллера:

- биты [7:5]: 0 (в PC не используются);

- бит 4:1 — признак команды инициализации (в командах управления он нулевой);

- бит 3 — чувствительность линий запроса: 0 — прерывание по перепаду, 1 — прерывание по уровню. В современных контроллерах игнорируется, в них используется отдельный регистр ELCR, управляющий чувствительностью каждого из входов;

- бит 2 = 0 (в PC не используется);

- бит 1:0 — каскадное включение пары контроллеров, 1 — одиночный контроллер;

- бит 0:1 — признак использования ICW4.

Команда инициализации ICW2 (запись по адресу 021h или 0A1h) задает номер вектора, генерируемого данным контроллером для входа 0. Биты [2:0] должны иметь нулевые значения.

Команда инициализации ICW3 (запись по адресу 021h или 0A1h) используется только для каскадного включения:

- для ведущего контроллера (Master, 8259A#1) биты [0:7] указывают на наличие ведомых контроллеров на линиях IRQ0–IRQ7 соответственно. В AT ICW3 = 04h (ведомый на IRQ2);

- для ведомого контроллера (Slave, 8259A#2) биты [2:0] содержат номер входа ведущего контроллера, к которому он подключен, биты [7:3] сброшены. В AT ICW3 = 02h (подключен к IRQ2 ведущего).

Команда инициализации ICW4 (запись по адресу 021h или 0A1h) задает режим работы контроллера, его применение обязательно при начальной инициализации:

- биты [7:5]: 0 — не используются;

- бит 4 — SFNM (Special Fully Nested Mode): 1 — специальный режим полной вложенности разрешен, 0 — запрещен;

- бит 3 — BUF (Buffered): 1 — признак буферизованности шины;

- бит 2 — M/S (Master/Slave), положение в каскаде: 1 — ведущий, 0 — ведомый. В современных контроллерах не используется (сброшен);

- бит 1 — AEOI (Auto End Of Interrupt): 1 — разрешение автоматического завершения прерывания, 0 — нормальный режим (требует подачи EOI);

- бит 0 — тип используемого процессора: 1 — 8086/8088 и далее, 0 — 8080.

Команда управления OCW1 (запись по адресу 021h или 0A1h) задает маски запросов, единичное значение бита означает маскирование запроса. Биты [0:7]определяют маски запросов для IRQ0–IRQ7 (8259#1) или IRQ8–IRQ15 (8259#2).

Команда управления OCW2 (запись по адресу 020h или 0A0h) — завершение обслуживания прерывания (команда EOI), управление приоритетом:

- биты [7:5] задают код операции (в операциях, помеченных звездочкой, используется поле LLL в битах 2–0):

- -001 — неспецифический EOI;

- -011* — специфический EOI для запроса LLL;

- -101 — неспецифический EOI с ротацией приоритета;

- -100 — установка ротации приоритета в режиме AEOI;

- -000 — сброс ротации приоритета в режиме AEOI;

- -111* — специфический EOI с ротацией приоритета (установкой низшего приоритета для заданного уровня);

- -110* — установка низшего приоритета для заданного уровня;

- -010 — нет операции.

- биты [4:3]: 00 — признак OCW2;

- биты [2:0] — поле LLL — номер уровня, к которому относится команда (только для команд, помеченных звездочкой).

Команда управления OCW3 (запись по адресу 020h или 0A0h) — оперативное управление контроллером:

- бит 7:0 — не используется;

- биты [6:5] — режим специального маскирования (в PC не используется): 11 — установить, 10 — сбросить, 00, 01 — не изменять;

- биты [4:3]: 01 — признак OCW3;

- бит 2 — признак команды опроса (полинга). После команды полинга на последующую команду чтения порта 020h или 0A0h контроллер ответит байтом, кодирующим запрос прерывания с максимальным приоритетом. Для PC полинг обычно не используется (бит 2 — нулевой), а контроллер передает вектор прерывания по команде INTA;

- биты [1:0] — управление чтением регистров при операциях ввода по адресу 020h или 0A0h:

- -10 — чтение IRR — регистра запросов;

- -11 — чтение ISR — регистра обслуживаемого прерывания;

- -00, 01 — не изменять выбор регистра.

Регистры ELCR, имеющиеся в современных компьютерах, позволяют селективно управлять чувствительностью входов. В этих регистрах каждый бит отвечает за режим своего входа запроса: 0 — чувствительность к положительному перепаду, 1 — чувствительность к высокому уровню. Для входов IRQ0, 1, 2, 8 и 13 (таймер, клавиатура, вторичный контроллер прерываний, часы и исключение сопроцессора), допускается чувствительность только к перепаду (соответствующие биты должны быть нулевыми, но чипсет может их и игнорировать). Линии запросов прерывания от PCI по пути ко входам инвертируются, так как на них запрос сигнализируется низким уровнем.

В IBM PC/XT/AT используется специальный режим вложенных прерываний с фиксированным приоритетом и автоматическим неспецифическим завершением; типовые байты инициализации и управления приведены в следующей таблице. После инициализации (процедурой POST и при загрузке ОС) все неиспользуемые входы контроллеров замаскированы (на запросы прерываний реагировать не будут), а их векторы прерываний указывают на «заглушку» — процедуру с единственной инструкцией IRET. Для подключения обработчика прерывания от устройства первым делом следует загрузить обработчик в память и установить указатель на него в таблице прерываний. Далее следует размаскировать соответствующий ему вход в контроллере прерываний, для чего выполняется чтение регистра маски (адрес 21h для 8259A#1, A1h для 8259A#2), обнуление соответствующего бита и запись в регистр нового значения маски. Если обработчик прерывания удаляется из памяти, предварительно должен быть замаскирован соответствующий ему вход контроллера. Все изменения в таблице прерываний должны выполняться при замаскированных прерываниях, чтобы избежать попытки использования вектора в процессе его модификации (это приведет к «вылету» программы — вызову по некорректному адресу).

Каждая процедура обработки аппаратного прерывания должна завершаться командой неспецифического EOI — посылкой OCW2 = 20h контроллеру:

| Байт | 8259A#1 | 8259A#2 |

| ICW1 | 10h | 10h |

| ICW2 | 08h | 70h |

| ICW3 | 04h | 02h |

| ICW4 | 1Fh | 1Bh |

| OCW3 | 0Ah | 0Ah |

На современных системных платах функции контроллеров прерываний возлагаются на чипсет, который может иметь и более гибкие возможности управления, чем пара контроллеров 8259A. Процедура инициализации контроллеров может и отличаться от традиционной, но ею занимается тест POST, который «знает» особенности системной платы. Однако в операционном режиме всегда сохраняется программная совместимость с 8259A.

Маршрутизация по иерархическому адресу

Задача маршрутизации — определение, где по отношению к мосту находится ресурс, адресованный каждой транзакции, — является первоочередной при обработке каждой транзакции, «увиденной» мостом на любом из своих интерфейсов. Эта задача решается двояко, поскольку в фазе адреса может передаваться как иерархический адрес PCI (шина -> устройство -> функция), так и «плоский» адрес памяти или порта ввода-вывода.

Маршрутизация по иерархическому адресу

Через номера шины и устройства адресуются транзакции конфигурационной записи и чтения, генерации специального цикла, а в PCI-X еще и завершение расщепленной транзакции, а также сообщения DIM. Для этих транзакций маршрутизация основана на системе нумерации шин. Номера назначаются шинам PCI при конфигурировании системы строго последовательно, номера мостов соответствуют номерам их вторичных шин. Так, главный мост имеет номер 0. Номера подчиненных шин моста начинаются с номера, следующего за номером его вторичной шины. Таким образом, для каждого моста необходимые ему знания топологии шин системы описываются списком номеров шин — тремя числовыми параметрами в его конфигурационном пространстве:

- Primary Bus Number — номер первичной шины;

- Secondary Bus Number — номер вторичной шины (это и номер моста);

- Subordinate Bus Number — максимальный номер подчиненной шины.

Все шины с номерами в диапазоне от Secondary Bus Number до Subordinate Bus Number включительно будут лежать со стороны вторичного интерфейса, все остальные — на стороне первичного.

Знание номеров шины позволяет мостам распространять обращения к конфигурационным регистрам устройств в сторону от хоста к подчиненным шинам и распространять специальные циклы во всех направлениях. Ответы на расщепленные транзакции (Split Complete) мост транслирует с одного интерфейса на другой, если они адресованы к шине противоположного интерфейса.

Конфигурационные циклы типа 0 и специальные циклы мостами не транслируются. Конфигурационные транзакции типа 1, обнаруженные на первичном интерфейсе, мост обрабатывает следующим образом:

- Преобразует их в конфигурационные циклы типа 0 или специальные циклы, если номер шины (на линиях AD[23:16]) соответствует номеру вторичной шины. При преобразовании в цикл типа 0 номер устройства с первичной шины, полученный в фазе адреса, декодируется в позиционный код на вторичной шине (см. главу 2), номер функции и регистра передается без изменений, биты AD[1:0] на вторичной шине обнуляются. В PCI-X кроме позиционного кода на вторичную шину передается и номер устройства. Преобразование в специальный цикл (изменение кода команды) производится, если в полях номера устройства и функции все биты единичные, а в поле номера регистра — нулевые.

- Пропускает их с первичного интерфейса на вторичный без изменения, если номер шины соответствует диапазону номеров подчиненных шин.

- Игнорирует, если номер шины лежит вне диапазона номеров шин стороны вторичного интерфейса.

Со стороны вторичного интерфейса мост передает на первичный только конфигурационные циклы типа 1, относящиеся к специальным циклам (в полях номера устройства и функции все биты единичные, а в поле номера регистра — нулевые). Если номер шины соответствует номеру первичной шины, мост преобразует эту транзакцию в специальный цикл.

Если конфигурационный цикл не воспринимается ни одним из устройств, мосты могут эту ситуацию отрабатывать двояко: фиксировать отсутствие устройства (сработает Master Abort) или же выполнять операции вхолостую. Однако в любом случае чтение конфигурационного регистра несуществующего устройства (функции) должно возвращать значение FFFFFFFFh (это будет безопасной информацией, поскольку даст недопустимое значение идентификатора устройства).

Еще статьи...

Подкатегории

-

Протокол, команды и транзакции шин PCI и PCI-X

- Кол-во материалов:

- 12

-

Общая информация

- Кол-во материалов:

- 4

-

Электрический интерфейс и конструктивы для шин PCI

- Кол-во материалов:

- 8

-

Конфигурирование и BIOS устройств PCI и PCI-X

- Кол-во материалов:

- 10

-

Мосты PCI и PCI-X

- Кол-во материалов:

- 10

-

Прерывания PCI: INTx#, PME#, MSI и SERR#

- Кол-во материалов:

- 7