Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

PCI и PCI-X

Обмен сообщениями между устройствами (команда DIM)

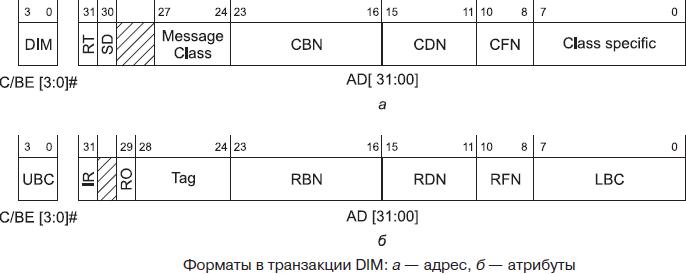

В PCI-X 2.0 введена возможность передачи информации (сообщений) устройству, адресуясь с помощью идентификатора (номера шины, устройства и функции). Для адресации и маршрутизации этих сообщений, которыми могут обмениваться любые устройства шины (включая и главный мост), не используется адресное пространство памяти или ввода/вывода. Сообщения передаются последовательностями, в которых используются команды DIM (Device ID Message), отличающиеся специфичностью адреса и атрибутов. В фазе адреса (рисунок ниже, а) передается идентификатор получателя сообщений (Completer ID) — номер его шины (CBN), устройства (CDN) и функции (CFN). Бит RT (Route Type) указывает тип маршрутизации сообщения: 0 — явная адресация с использованием вышеуказанного идентификатора, 1 — неявная адресация к главному мосту (при этом идентификатор не используется). Бит SD (Silent Drop) задает способ отработки ошибок при выполнении данной транзакции: 0 — обычный (как для записи в память), 1 — игнорирование некоторых типов ошибок (но не контроля четности или ECC). Поле Message Class задает класс сообщения, в соответствии с которым трактуется младший байт адреса. Транзакция может использовать и двухадресный цикл, при этом в первой фазе адреса по линиям C/BE[3:0]# передается код команды DAC, содержимое бит AD[31:00] соответствует рисунку, а. Во второй фазе адреса по линиям C/BE[3:0]# передается код команды DIM, а все биты AD[31:00] трактуются в зависимости от класса сообщения. Устройство, поддерживающее обмен сообщениями, декодировав команду DIM, проверяет поля идентификаторов получателя на соответствие своему собственному.

В фазе атрибутов (рисунок, б) передается идентификатор источника сообщения (RBN, RDN и RFN), тег сообщения (Tag), 12-битный счетчик байтов (UBC и LBC) идополнительные биты-признаки. Бит IR (Initial Request) является признаком начала сообщения, которое может быть разорвано на несколько частей инициатором, получателем или промежуточными мостами (во всех последующих частях бит обнулен). Бит RO (Relaxed Ordering) указывает на возможность неупорядоченной доставки данного сообщения по отношению к другим сообщениям и записям в память, распространяемым в том же направлении (порядок доставки фрагментов данного сообщения сохраняется всегда).

Тело сообщения, передаваемое в фазах данных, может иметь длину до 4096 байт (предел обусловлен 12-битным счетчиком длины). Содержимое тела определяется классом сообщения; класс 0 отдается на использование по воле производителя.

Сообщения с явной маршрутизацией маршрутизируются мостами на основе номера шины получателя. Проблемы передачи могут возникать только на главных мостах: если в системе имеется несколько главных мостов, то архитектурная связь между ними может быть очень сложной (например, через магистрали контроллера памяти). Передача сообщений с шины на шину через главные мосты желательна (это проще, чем передача транзакций всех типов), но не строго обязательна. Поддержка этой передачи дает больше свободы пользователю (не приходится при расстановке устройств принимать во внимание всю топологию шин). Сообщения с неявной маршрутизацией передаются только по направлению к хосту.

Поддержка DIM для устройств PCI-X необязательна; мосты PCI-X Mode 2 обязаны поддерживать DIM. Если сообщение DIM адресуется к устройству, находящемуся на шине, работающей в стандартном режиме PCI (или путь к нему ведет через PCI), мост либо просто аннулирует это сообщение (если SD = 1), либо отвергает транзакцию (Target Abort, если SD = 0).