Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

http://govoritel.ru/gromkogovoriteli пожарный 2 режима сирена громкоговоритель. Купить подарочный сертификат Летуаль по доступным ценам на сайте Кинг Гифтс.

PCI Express

PCI Express

Общая информация

- Подробности

- Родительская категория: PCI Express

- Категория: PCI Express

PCI Express — новая архитектура соединения компонентов, введенная под эгидой PCI SIG, известная и под названием 3GIO (3-Generation Input-Output, ввод/вывод 3-го поколения). Здесь шинное соединение устройств с параллельным интерфейсом заменено на двухточечные последовательные соединения с использованием коммутаторов. В этой архитектуре сохраняются многие программные черты шины PCI, что обеспечивает плавность миграции от PCI к PCI Express. В архитектуре появились новые возможности: управление качеством обслуживания (QoS), потреблением и бюджетом связей. Протокол PCI Express отличается малыми накладными расходами и малыми задержками выполнения транзакций.

PCI Express позиционируется как универсальная архитектура ввода/вывода для компьютеров разных классов, телекоммуникационных устройств и встроенных систем. Высокая пропускная способность достигается при цене, соизмеримой с PCI и ниже. Сфера применения — от соединений между микросхемами на плате до межплатных разъемных и кабельных соединений. Высокая пропускная способность на контакт соединения позволяет минимизировать число соединительных контактов. Малое число сигнальных линий позволяет применять малогабаритные конструктивы. Универсальность дает возможность использования единой программной модели для всех форм-факторов. Спецификация PCI Express Base specification Revision 1.0a опубликована в апреле 2003 года.

Элементы и топология соединений PCI Express

- Подробности

- Родительская категория: PCI Express

- Категория: PCI Express

Соединение PCI Express (PCI Express Link) — это пара встречных симплексных каналов, соединяющих два компонента. По этим каналам передаются пакеты, несущие команды и данные транзакций, сообщения и управляющие посылки. Канал может быть образован одной или несколькими линиями передачи сигналов (Lane); применение нескольких линий позволяет масштабировать пропускную способность канала. В PCI Express с помощью пакетного протокола реализуются все транзакции чтения и записи, используемые в PCI, причем в расщепленном варианте. Таким образом, здесь фигурируют запросчик транзакции (Requester) и исполнитель транзакции (Completer). В PCI Express рассматриваются четыре пространства: памяти, ввода/вывода, конфигурационное и сообщений. Новое (по сравнению с PCI) пространство сообщений (Message Space) используется для передачи в виде пакетов «внеполосных» сигналов PCI: прерываний по линиям INTx, управления потреблением и т. п. Таким образом реализуются «виртуальные провода». Порт PCI Express содержит передатчик, приемник и узлы, необходимые для сборки-разборки пакетов.

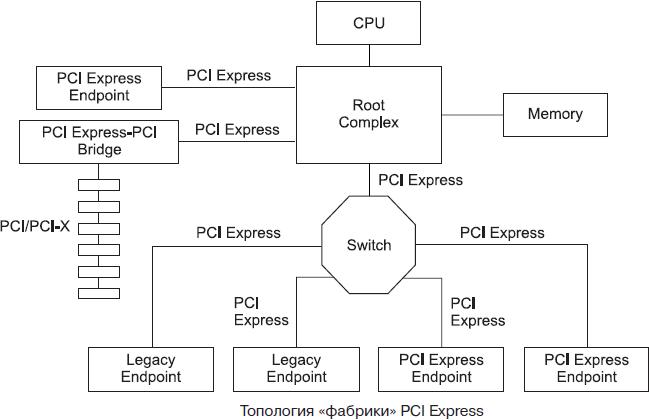

Пример топологии средств ввода/вывода, иллюстрирующий архитектуру PCI Express, приведен на рисунке ниже. Центральным элементом архитектуры является корневой комплекс (Root Comlex), соединяющий иерархию ввода/вывода с центром — процессором (одним или несколькими) и памятью. Корневой комплекс может иметь один и более портов PCI Express, каждый из них определяет свой домен иерархии (hierarchy domain). Каждый домен состоит из одной конечной точки (Endpoint) или субиерархии — нескольких конечных точек, связанных коммутаторами. Возможность непосредственных равноранговых коммуникаций между элементами разных доменов обязательной не является, но может присутствовать в конкретных реализациях. Для обеспечения прозрачных равноранговых коммуникаций в корневом комплексе должны присутствовать коммутаторы. Возможность взаимодействия центрального процессора с любым устройством любого домена безусловна, как и возможность обращения любого устройства к памяти. Корневой комплекс должен генерировать запросы к конфигурационному пространству — его роль аналогична главному мосту PCI. Корневой комплекс может генерировать запросы ввода/вывода как запросчик; он может генерировать и блокированные (Locked) запросы, требующие непрерываемого исполнения. Корневой комплекс не должен поддерживать блокированные запросы как исполнитель (Completer) — это предотвращает «заклинивание» ввода/вывода.

Конечная точка (Endpoint) — это устройство, способное инициировать и/или исполнять транзакции PCI Express от своего имени или от имени устройства не-PCI Express (например, хост контролера USB). Конечная точка должна быть видима в одном из доменов иерархии. Конечная точка должна иметь заголовок конфигурационного пространства типа 0 и отвечать как исполнитель на конфигурационные запросы. В качестве механизма сигнализации прерываний все конечные точки используют MSI. В PCI Express рассматриваются два типа конечных точек: «наследники» (Legacy) и новые точки, построенные по идеологии PCI Express. К «наследным» точкам имеется ряд послаблений:

- в плане адресации памяти они могут и не поддерживать более 4 Гбайт;

- ввод/вывод может не быть абсолютно перемещаемым (из пространства ввода/

вывода в пространство памяти) с помощью регистров базового адреса (BAR), так что могут потребоваться транзакции обращения к пространству ввода/вывода (транзакции к памяти предпочтительнее); - диапазон занимаемых адресов может быть менее 128 байт (требования к границам были жестко сформированы в PCI-X);

- конфигурационное пространство может не быть расширенным (оставаться в пределах 256 байт);

- программная модель может требовать использования блокированных запросов к устройству (но не от него).

Коммутатор (Switch) имеет несколько портов PCI Express. Логически он представляет собой несколько виртуальных мостов PCI-PCI, соединяющих порты коммутатора со своей внутренней локальной шиной. Виртуальный мост PCI описывается конфигурационными регистрами с заголовком типа 1. Порт, ведущий к вершине иерархии, называется восходящим (upstream port) — через него коммутатор конфигурируется как набор мостов PCI. Коммутатор транслирует между портами пакеты всех типов, основываясь на адресной информации, актуальной для пакета данного типа. Коммутатор не распространяет блокированные запросы со своих нисходящих портов. Арбитраж между портами коммутатора может учитывать виртуальные каналы и, соответственно, взвешенно распределять пропускную способность. Коммутатор не имеет права разбивать пакеты на более мелкие (аналог этого права имеется в мостах PCI).

Мост PCI Express–PCI соединяет иерархию шин PCI/PCI-X с «фабрикой» ввода/вывода — корневым комплексом или коммутаторами PCI Express.

Конфигурирование «фабрики» осуществляется либо со 100% совместимостью с конфигурационным механизмом PCI 2.3, либо с использованием расширенного конфигурационного пространства PCI-X. Каждое соединение PCI Express с помощью виртуальных мостов отображается в виде логической шины PCI со своим номером. Логические устройства отображаются в конфигурационном пространстве как устройства PCI, каждое из которых может иметь 1–8 функций со своим набором конфигурационных регистров.

Программная совместимость с PCI/PCI-X

- Подробности

- Родительская категория: PCI Express

- Категория: PCI Express

Программная модель PCI Express совместима с PCI в следующих аспектах:

- обнаружение, нумерация и конфигурирование устройств PCI Express выполняются тем же конфигурационным ПО, что используется в PCI (PCI-X 2.0);

- существующие ОС загружаются без каких-либо модификаций;

- драйверы существующих устройств поддерживаются без каких-либо модификаций;

- конфигурирование и разрешение новых функциональных возможностей PCI Express выполняется по общей идее конфигурирования устройств PCI.

Качество обслуживания и виртуальные каналы

В PCI Express имеется поддержка дифференцированных классов по качеству обслуживания (QoS), обеспечивающая следующие возможности:

- выделять ресурсы соединения для потока каждого класса (виртуальные каналы);

- конфигурировать политику по QoS для каждого компонента;

- указывать QoS для каждого пакета;

- создавать изохронные соединения.

Для поддержки QoS применяется маркировка трафика: каждый пакет TLP имеет трехбитное поле метки класса трафика TC (Traffic Class). Это позволяет различать передаваемые данные по типам, создавать дифференцированные условия передачи трафика для разных классов. Порядок исполнения транзакций соблюдается в пределах одного класса, но не между разными классами. Для дифференцирования условий передачи трафика разных классов в коммутирующих элементах PCI Express могут создаваться виртуальные каналы. Виртуальный канал VC (Virtual Channel) представляет собой физически обособленные наборы буферов и средств маршрутизации пакетов, которые загружаются только обработкой трафика своего виртуального канала. На основе номеров виртуальных каналов и их приоритетов производится арбитраж при маршрутизации входящих пакетов. Каждый порт, поддерживающий виртуальные каналы, выполняет отображение пакетов определенных классов на соответствующие виртуальные каналы. При этом на один канал может отображаться произвольное число классов. По умолчанию весь трафик маркируется нулевым классом (TC0) и передается дежурным каналом (VC0). Виртуальные каналы вводятся по мере необходимости.

Архитектурная модель PCI Express

- Подробности

- Родительская категория: PCI Express

- Категория: PCI Express

Архитектура PCI Express разделена на три уровня:

- уровень транзакций (Transaction Layer) — верний уровень архитектуры, отвечающий за сборку и разборку транзакционных пакетов TLP (Transaction Layer Packets). Эти пакеты используются для транзакций чтения и записи, а также сообщения о событиях некоторых типов. Каждый пакет TLP имеет уникальный идентификатор, который позволяет направить ответный пакет его отправителю. В TLP используются различные форматы адресации, зависящие от типов транзакций. Пакет может иметь атрибуты отмены слежения за когерентностью NS (No Snoop) и «расслабленной» упорядоченности RO (Relaxed Ordering). Каждая транзакция, требующая ответа, выполняется в виде расщепленной. Уровень транзакций отвечает и за управление потоком, реализованное на основе механизма кредитов;

- канальный уровень (Data Link Layer), промежуточный в стеке, первым делом отвечает за управление связью, обнаружение ошибок и организации повторных передач, до успеха или признания отказа соединения. К пакетам, полученным от уровня транзакций, канальный уровень добавляет номера пакетов и контрольные коды. Канальный уровень и сам является генератором и получателем пакетов DLLP (Data Link Layer Packet), используемых для управления соединением;

- физический уровень изолирует канальный от всех подробностей передачи сигналов. Он состоит из двух субблоков. Логический субблок при передаче выполняет распределение данных по линиям, скремблирование, кодирование по схеме 8B/10B, кадрирование и преобразование в последовательный код. При приеме выполняются обратные действия. Дополнительные символы, обеспечиваемые кодированием 8B/10B, используются для служебной сигнализации. Логический субблок отвечает и за согласование соединения, инициализацию и т. п. Электрический субблок отвечает за электрическое согласование, синхронизацию, обнаружение приемника. Уровневая модель, принятая в PCI Express, позволяет, не затрагивая остальных уровней, заменить физический уровень или его субблоки, когда появятся более эффективные схемы кодирования и сигнализации. Интерфейс между физическим и канальным уровнем зависит от реализации этих компонентов и выбирается их разработчиком. Интерфейс физического уровня четко специфицирован, что обеспечивает возможность соединения устройств разного происхождения. Для тестирования на соответствие электрическим параметрам достаточно подключить устройство PCI Express к специальному тестеру.

Сигнализация прерываний и управление энергопотреблением

- Подробности

- Родительская категория: PCI Express

- Категория: PCI Express

Основной метод сигнализации прерываний в PCI Express — с помощью передачи сообщений (MSI), причем с 64-битной адресацией (32-битная разрешена только для «наследных» устройств). Однако ради обеспечения программной совместимости устройство может использовать и эмуляцию прерываний через INTx#, передавая эти запросы с помощью специальных пакетов. Получателем пакетов сигнализации прерываний, как MSI, так и эмуляции INTx#, как правило, является контроллер прерываний, расположенный в корневом комплексе. Сигнализация INTx# производится пакетами класса TC0. Прерывания MSI при использовании виртуальных каналов должны использовать класс трафика, соответствующий классу трафика данных, к которым относятся данные прерывания. Иначе возможно нарушение синхронизации из-за относительной неупорядоченности трафика разных классов. Синхронизации можно добиваться и теми же средствами, что и в PCI/PCI-X — чтением (пусть даже нулевой длины) через коммутатор (мост). Такой прием неизбежен, если прерывания относятся к данным нескольких разных классов (виртуальных каналов).

Сигнализация событий управления энергопотреблением возможна в двух вариантах: пакетная эмуляция сигнала PME# (аналогично эмуляции INTx#) и естественная сигнализация PCI Express с помощью соответствующих сообщений. При эмуляции PME# идентификация источника сигнала выполняется последовательным чтением конфигурационных регистров устройств, способных генерировать этот сигнал. Естественная сигнализация гораздо удобнее: идентификатор устройства-источника присутствует в сообщении.

Расширенное управление потреблением и бюджетом мощности (PM — power management) означает:

- возможность идентификации способностей к PM каждой функции;

- возможность перевода функции в указанное состояние потребления;

- возможность получения информации о текущем состоянии потребления функции;

- возможность генерации запроса пробуждения при выключенном основном питании;

- возможность последовательного включения устройств.

Еще статьи...

Подкатегории

-

PCI Express

- Кол-во материалов:

- 10