Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

Базовая организация ЭВМ

Архитектура ЭВМ

В данном разделе мы ознакомимся с основными принципами работы ЭВМ. Узнаем о особенностях построения и взаимодействия всех компонентах.... А так же многое многое друге. Этот раздел будет познавательным как для начинающих так и для "прошаренных" пользователей.....

Эволюция развития ЭВМ

- Подробности

- Родительская категория: Архитектура ЭВМ

- Категория: Базовая организация ЭВМ

Стоит сразу сказать, что разные авторы, и вообще, различные источники по своему разделяют этапы эволюции ВТ (вычислительной техники). Я же постараюсь выделить самые основные пути развития:

0) Нулевое поколение — так называемая "механическая эра". Вообще, это поколение не принято считать официально, но я всё таки решился привести пару примеров, дабы было понятно с чего всё начиналось. В эту группу можно отнести:

Первые счёты — абак в древнем Вавилоне 3000 лет до н.э.

1492 г. Всем известный Леонардо да Винчи приводит рисунок тринадцатиразрядного десятичного сумматора на основе зубчатых колёс.

Счёты с косточками на проволоке — 500 лет до н.э., Китай

1885 г. Дорр Фельт, с этим именем связано появление первого калькулятора, в котором числа вводятся нажатием клавиш.

1938 г. Конрад Цузе изобретает программируемый вычислитель Z1 с памятью на 1000 бит. Позже Z3 с программой на перфоленте. Такая операция как умножение одного числа на другое занимает около 5 секунд. Можно сказать, что это и было толчком для продвижения вперёд в области вычислительной техники.

1) Первое поколение — электронные лампы (1945-1955). Типичный представитель — ЭВМ ЭНИАК. Это поколение аккумуляторных ЭВМ с небольшой памятью (4 Кбайт).

2) Второе поколение — в основе работы лежали транзисторы (1955-1965). Изобретение транзистора произошло в лаборатории Bell Laboratories, за что была получена Нобелевская премия в 1956 г. Ну так вот, появились новые архитектурные элементы: блок обработки чисел с плавающей запятой, память на магнитных сердечниках, общая шина, Широко распространился отечественный компьютер Минск-32.

3) Третье поколение — интегральные схемы (1965-1980). Была изобретена кремниевая интегральная схема в 1958 году Робертом Нойсом. Среди архитектурных новшеств: конвейерная и параллельная обработка, кэш-память, микропрограммирование, ну и конечно же первые операционные системы. Во всём мире известность получил компьютер IBM-360, который обладал следующими характеристиками (речь идёт о модели 50): время цикла 500 нс (наносекунд), объём памяти 256 Кбайт, за одно обращение к ОЗУ выбирал 4 байта.

4) Четвёртое поколение - времена сверхбольших интегральных схем (1980-....). Large-scale integration LSI — до 1000 транзисторов на кристалле. Very Large-scale integration VLSI — до 100 000 транзисторов на кристалле. Появился первый микропроцессор — ЭВМ на кристалле, а затем и персональные ЭВМ Intel и Apple. В 1981 году появился первый персональный компьютер IBM PC. Оснавная память стала полупроводниковой. Идея ЭВМ с сокращённым набором команд — RISC идеология(об этом будем ещё говорить). Язык программирования C.

5) Пятое поколение — мультипроцессорные системы (1990-....)

6) Шестое поколение — в разработке. Шестое поколение связывают с искусственным интеллектом.

Ну вот и всё. Мы разобрали основные поколения развития ЭВМ.....

Процессор — аппаратный уровень. Операционные устройства

- Подробности

- Родительская категория: Процессор

- Категория: Процессор — аппаратный уровень.

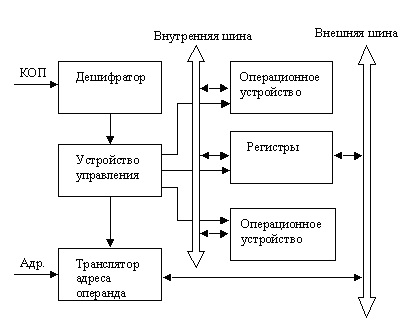

Процессор — это ядро и мотор компьютера, обеспечивает как выполнение операций, так и функционирование всех узлов. Обычно простой процессор включает в себя декодер команд, арифметико-логическое устройство (АЛУ), регистры, транслятор адресов операндов и устройство управления. Отдельные элементы связаны внутренней шиной. Связь с внешними устройствами осуществляется через внешнюю шину.

Структура процессора

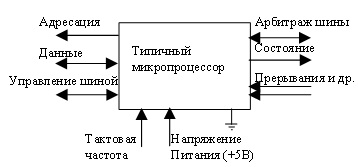

Все перечисленные элементы могут помещаться в одной микросхеме — микропроцессоре. Они доступны через выводы микросхемы при выполнении команд, загружаемых из ОЗУ. На следующем рисунке показаны выводы типичного микропроцессора. Рассмотрим как работает процессор изнутри, на аппаратном и микропрограммном уровне. Далее будет представлено рассмотрение конкретного процессора i8086.

Типичный процессор

Аппаратный уровень процессора в настоящее время не является ни программно доступным, ни даже наблюдаемым, однако представление о нем помогает пониманию таких вопросов, как скорость выполнения команд, возможность конвейеризации и т.д.

Для того чтобы понять как выполняются команды в процессоре рассмотрим работу операционных устройств. В машине фон Неймана в качестве операционного устройства применяется АЛУ. Учитывая разнообразие выполняемых операций и обрабатываемых данных, можно говорить не об одном устройстве, а о целом комплексе специализированных операционных устройств, каждое из которых выполняет свое подмножество операций (команд). Следует выделить операционные устройства:

- целочисленной арифметики;

- логических операций;

- десятичной арифметики;

- чисел с плавающей запятой.

Кроме указанных устройств процессоры в зависимости от их назначения могут иметь и другие операционные устройства: управления потреблением, графических операций, упаковки/распаковки изображений и др. В минимальном варианте операционное устройство целочисленной арифметики (АЛУ) должно содержать аппаратуру для реализации лишь основных логических операций, сдвигов, инвертирования, а также сложения чисел в формате с фиксированной запятой. Опираясь на этот набор, можно программным способом обеспечить выполнение остальных арифметических и логических операций как для чисел с фиксированной запятой, так и для других форм представления информации. Следует отметить, что подобный вариант не позволяет добиться высокой скорости вычислений, поэтому по мере расширения технологических возможностей доля аппаратных средств в составе АЛУ постоянно возрастает. Набор элементов, на основе которых строятся структуры различных операционных устройств, называется структурным базисом. Структурный базис операционных устройств включает в себя:

- регистры, обеспечивающие хранение слов данных;

- шины, связывающие регистры и предназначенные для передачи слов данных;

- комбинационные схемы, реализующие вычисления по управляющим сигналам от устройства управления.

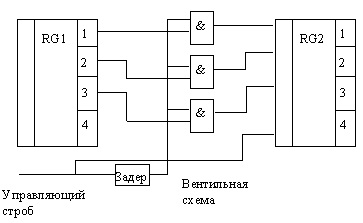

Выполнение команды может быть сведено к нескольким (одновременно или последовательно во времени) операциям пересылки из регистра в регистр(на рисунке). Возможно с промежуточным преобразованием пересылаемых двоичных слов на комбинационных логических схемах. В следующей теме подробно рассмотрим регистры.

Регистры операционного устройства

Конвейер команд. Конвейеризация — способ обеспечения параллельности выполнения команд

- Подробности

- Родительская категория: Процессор

- Категория: Конвейер команд

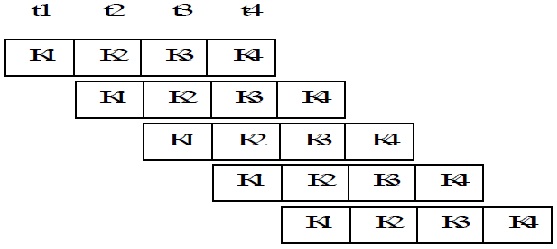

Первым шагом на пути обеспечения параллельности уровня команд явилось создание конвейера команд. Идея конвейера команд была предложена в 1956 году С.А. Лебедевым. Команда подразделяется на несколько этапов, каждый из которых выполняется своей частью аппаратуры, причем, эти части могут работать параллельно. Если на выполнение каждого этапа расходуется одинаковое время (один такт), то на выходе процессора в каждый такт появляется результат очередной команды. Производительность при этом возрастает благодаря тому, что одновременно на различных ступенях конвейера выполняется несколько команд. Конвейерная обработка такого рода широко применяется во всех современных быстродействующих процессорах. Количество этапов, на которые конструкторы разбивают выполнение процессорной команды, может быть различным (в разных моделях процессоров х86 колеблется от 2 i8088 до 20 Pentium IV).

Конвейеризация — способ обеспечения параллельности выполнения команд

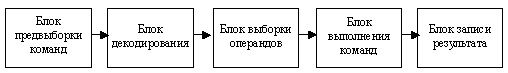

Выполнение типичной команды можно разделить на следующие этапы:

- выборка команды — IF (по адресу, заданному счетчиком команд, из памяти извлекается команда);

- декодирование команды / выборка операндов из регистров — ID;

- выполнение операции / вычисление эффективного адреса памяти — EX;

- обращение к памяти — MEM;

- запоминание результата — WB.

В зависимости от типа команды и способа адресации, время выполнения команды сильно варьируется. Дольше всего выполняются этапы, связанные с обращением к памяти. На рисунках показаны блоки и конвейер команд гипотетического процессора, имеющего пять блоков исполнения команд и соответственно пять этапов (ступеней). Изображены выполняемые команды, номера тактов и этапы выполнения команд. На первом такте считывается первая команда. На втором, пока декодируется первая команда, считывается вторая. На пятом такте в процессоре одновременно находятся пять команд, каждая в своем узле.

Блоки прохождения команды в процессоре

Пятиступенчатая схема конвейера

Конвейеризация увеличивает пропускную способность процессора (количество команд, завершающихся в единицу времени), но она не сокращает время выполнения отдельной команды. Имеются некоторые накладные расходы на конвейеризацию, возникающие в результате несбалансированности задержки на каждой его ступени. Частота синхронизации (такт синхронизации) не может быть выше, чем время, необходимое для работы наиболее медленной ступени конвейера. Конвейер не всегда представляет собой линейную цепочку этапов. В ряде ситуаций оказывается выгодным, когда функциональные блоки соединены между собой не последовательно, а в соответствии с логикой обработки. Отдельные блоки в цепочке могут пропускаться, а другие — образовывать циклические процедуры. Это позволяет с помощью одного конвейера вычислять более одной функции.

Поток команд — естественная последовательность команд, проходящая по конвейеру процессора. Процессор может поддерживать несколько потоков команд (суперпроцессоры 5 и 6 поколения), если для каждого потока и каждого этапа есть исполнительные элементы.

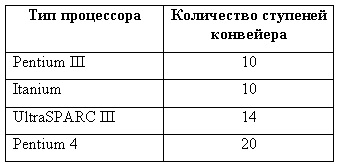

Суперконвейер команд — разбиение каждой ступени на подступени при одновременном увеличении тактовой частоты внутри конвейера; включение в состав процессора многих конвейеров, работающих с перекрытием. Дробление ступеней позволяет поднять тактовые частоты процессора. К суперконвейерным относятся процессоры, в которых число ступеней больше шести (см. таблицу).

Суперконвейер

Cуперконвейер ведет не только к увеличению скорости вычислений, но и к возникновению дополнительных сложностей. Возрастает вероятность конфликтов. Дороже встает ошибка предсказания перехода — приходится сбрасывать весь длинный конвейер, на что требуется дополнительное время. Усложняется логика взаимодействия ступеней. Однако за счет использования новых архитектур удается справиться с большинством проблем. При рассмотрении современных процессоров будут описаны новые идеи: исполнения команд с изменением последовательности, переименования регистров, спекулятивного исполнения и другие.

Устройство управления. Микропрограммный автомат

- Подробности

- Родительская категория: Процессор

- Категория: Устройство управления. Микропрограммный автомат

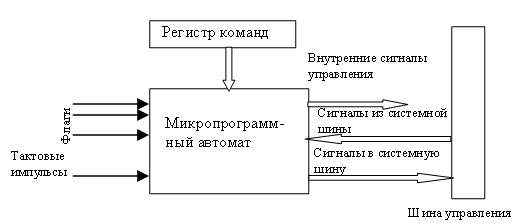

Устройство управления (УУ) ЭВМ реализует функции управления ходом вычислительного процесса, обеспечивая автоматическое выполнение команд программы (см. рисунок). Входной информацией для УУ служат:

- тактовые импульсы — с каждым импульсом УУ выполняет одну или несколько микроопераций;

- код операции — поступает из регистра команды и используется, чтобы определить, какие микроопераций должны выполняться;

- флаги — требуются для оценки состояния процессора, что необходимо для выполнения команд условного перехода;

- сигналы из системной шины — обслуживание прерывания, прямого доступа в память. В свою очередь УУ, а точнее микропрограммный автомат, формирует следующую выходную информацию:

- внутренние сигналы управления — перемещают операнды из регистра в регистр и инициируют работу операционных устройств;

- сигналы в системную шину — управляющие сигналы в память или в устройства ввода-вывода.

Модель устройства управления

Как отмечалось, процесс функционирования ЭВМ состоит из последовательности элементарных действий в ее узлах. Такие элементарные действия, выполняемые в течение одного такта сигналовсинхронизации, называются микрооперациями. Совокупность одновременно выполняемых микроопераций образует микрокоманду.

Последовательность микрокоманд, определяющая порядок реализации машинного цикла, составляет микропрограмму. Микропрограммный автомат определяет микропрограмму как последовательность выполнения микроопераций. В общей структуре УУ можно выделить две части: управляющую и адресную. Управляющая часть предназначена для координирования работы операционного блока, адресной части, основной памяти и др. Адресная часть обеспечивает формирование адресов команд и адресов операндов в основной памяти. Состав управляющей части: регистр команды, микропрограммный автомат, узел прерываний и приоритетов. Микропрограммный автомат на основе декодирования команды вырабатывает определенную последовательность микрокоманд. В зависимости от способа формирования микрокоманд различают микропрограммные автоматы с жесткой и программируемой логикой. Адресная часть УУ включает в себя: операционный узел устройства управления (ОПУУ), регистр адреса, счетчик команд. Регистр адреса используется для хранения исполнительных адресов операндов, а счетчик команд — для выработки и хранения адресов команд. Их содержимое посылаются в регистр адреса основной памяти. ОПУУ обрабатывает адресные части команд, формируя исполнительные адреса операндов, а также подготавливает адрес следующей команды при выполнении команд перехода. Иногда ОПУУ совмещают с основным операционным устройством. Ниже будет рассмотрена схема ОПУУ процессора i8086.

Способы адресации. Функции способов адресации (и механизма трансляции адреса)

- Подробности

- Родительская категория: Процессор

- Категория: Способы адресации

Способы адресации

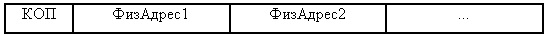

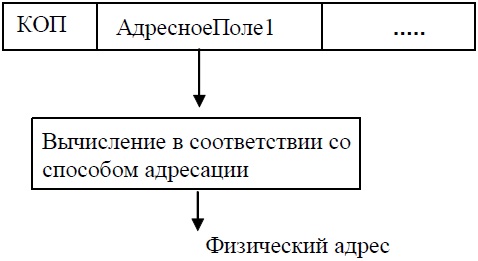

Простейшая структура адресной части команды:

Адресные поля содержат физические адреса.

1) Для ЭВМ 1 — .2 поколений были характерны небольшой обьем ОЗУ (4...32 Кслов) и значительная длина машинного слова (40...64 и более бит). Длина слова выбиралась обычно достаточной для представления числа с инженерной точностью в плавающем формате. При этом в поле адреса мог поместиться полный физический адрес (для маленького объема ОЗУ он был коротким).

2) В ходе развития ЭВМ

•увеличивался обьем ОЗУ, а, следовательно, и длина требуемого физического адреса;

•желательно было вычислять / модифицировать адреса. Это давало возможность одному участку программы обрабатывать данные, расположенные в разных адресах.

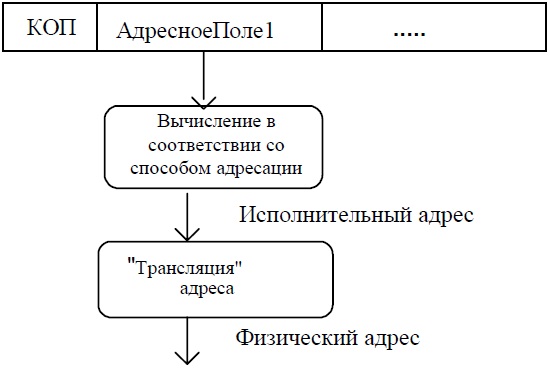

Перешли к следующей структуре (см. рисунок ниже):

Двухуровневая схема трансляции адреса

Простейший вариант: физический адрес содержится в адресном регистре, а адресное поле содержит имя (код, номер) адресного регистра плюс код, обозначающий способ адресации (в данном случае косвенно-регистровую адресацию — см. далее). Длина такого поля адреса, могла быть гораздо меньше длины адреса. Например, если процессор содержит восемь регистров общего назначения и использует не более 8 разных способов адресации, длина номера регистра = 3 бита, длина кода способа адресации — также 3 бита. Адресное поле в команде будет содержать всего 6 бит.

3) При дальнейшем развитии ЭВМ — увеличивается размер адресного пространства.

При 32-разрядном адресе размер адресного пространства = 4 ГБайт. В то же время реальный обьем ОЗУ составляет 16...128 МБайт (длина физического адреса: 24...27 разрядов). Таким образом, имеет место несовпадение диапазона логических адресов (в частности, тех чисел, которые могут храниться в адресных регистрах процессора) и диапазона физических адресов, нумерующих реально существующие ячейки ОЗУ. Поэтому все более широко используется следующая схема преобразования адресов (см. следующий рисунок):

Трехуровневая схема трансляции адреса

В результате вычисления в соответствии со способом адресации формируется объект, называемый исполнительным (executive) или эффективным (так переводят английский термин effective, хотя более правильным является перевод “исполнительный” или “действующий” адрес). Это понятие уровня языка ассемблера почти эквивалентно используемому в языках высокого уровня понятию указатель(pointer). Все перечисленные в данном абзаце понятия — прежде всего суть понятия логические (логические адреса).

Логические адреса требуется отображать на физические адреса фактически имеющейся памяти. В простейшем случае можно это делать "один в один", начиная (размещая, загружая) всю программу целиком в определенное место памяти. В то же время, как увидим далее, такое взаимно-однозначное отображение адресов не всегда удобно, а иногда даже и невозможно.

Понятие "Способ адресации" включает:

•1)Способ кодирования адреса в адресном поле команды;

•2)Условное обозначение (синтаксис) способа адресации при записи команды на языке ассемблера;

•3)Алгоритм вычисления исполнительного адреса по информации, содержащейся в адресном поле, а также в других элементах процессора, имеющих отношение к вычислению адреса (хранящих адресную информацию, компоненты адреса).

Функции способов адресации (и механизма трансляции адреса)

1. Обеспечить удобство вычисления логических адресов при отображении на память компонентов сложных структур данных (массив, структура и поля ее записей, список и т.п.) Это одно из свойств, которые обычно имеют в виду, когда говорят, что "микропроцессор оснащен средствами для программирования на языках высокого уровня".

2. Обеспечить переход от содержимого адресного поля команды к логическому адресу и отображение пространства логических адресов на пространство физических адресов.

3. Обеспечить перемещаемость программных модулей (для легкости компоновки из этих модулей большой программы) или обеспечения позиционной независимости программы.

Под термином "перемещаемость" могут иметь в виду одно из двух различных свойств программы. Статическая перемещаемостьсостоит в том, что оттранслированную программу можно, без модификации адресных частей команд, загружать, начиная с различных адресов, при этом программа сохраняет работоспособность. Динамическая перемещаемость — более сильное свойство, состоящее в том, что загруженную и выполняющуюся программу можно в любой точке остановить, переместить, как единое целое, в другое место памяти и затем успешно продолжить выполнение с точки останова.

4. Для настройки на реально существующую в системе физическую память.

5. Обеспечить возможность многозадачного режима работы, когда в памяти одновременно находятся и выполняются несколько программ: надо разрешить этим программам обмениваться информацией, но защитить их друг от друга (чтобы одна программа не имела возможности испортить другую).

Что такое "многозадачность"?

В простейшем случае есть две задачи: программа пользователя ПрП и операционная система ОС. ПрП не должна иметь возможности испортить ОС.

Другой пример: кроме ОС, две ПрП, из которых одна работает в фоновом режиме. Например, основная задача — текстовый процессор, с которым работает человек, редактируя текст. В паузах, когда человек думает, какую клавишу нажать, работает фоновая задача, например, распечатывается на принтере другой текст. Еще более сложный случай — многопользовательская система, когда на одном процессоре работает несколько пользователей одновременно, они разделяют процессорное время, пространства памяти и другие ресурсы. Механизм трансляции адреса позволяет отображать логические адреса программ, выполняемых на вычислительной системе именно в тот диапазон физических адресов, который соответствует реально установленной памяти.

Еще статьи...

Подкатегории

-

Базовая организация ЭВМ

.

- Кол-во материалов:

- 11

-

Процессор

•Процессор — аппаратный уровень. Операционные устройства.

•Устройство управления. Микропрограммный автомат.

•Конвейер команд.

•Архитектуры системы команд.

•Система команд процессора.

•Способы адресации.

•Управление вычислительным процессом.

•Кодирование команд в процессоре х86.- Кол-во материалов:

- 30

-

Кодирование команд в процессоре х86

- Кол-во материалов:

- 2

-

Управление вычислительным процессом

- Кол-во материалов:

- 8

-

Способы адресации

- Кол-во материалов:

- 2

-

Система команд процессора

- Кол-во материалов:

- 6

-

Архитектуры системы команд

- Кол-во материалов:

- 5

-

Конвейер команд

- Кол-во материалов:

- 1

-

Устройство управления. Микропрограммный автомат

- Кол-во материалов:

- 2

-

Процессор — аппаратный уровень.

- Кол-во материалов:

- 4