Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

Память. Нижний уровень

Микросхемы памяти

Микросхемы памяти

- Подробности

- Родительская категория: Память. Нижний уровень

- Категория: Микросхемы памяти

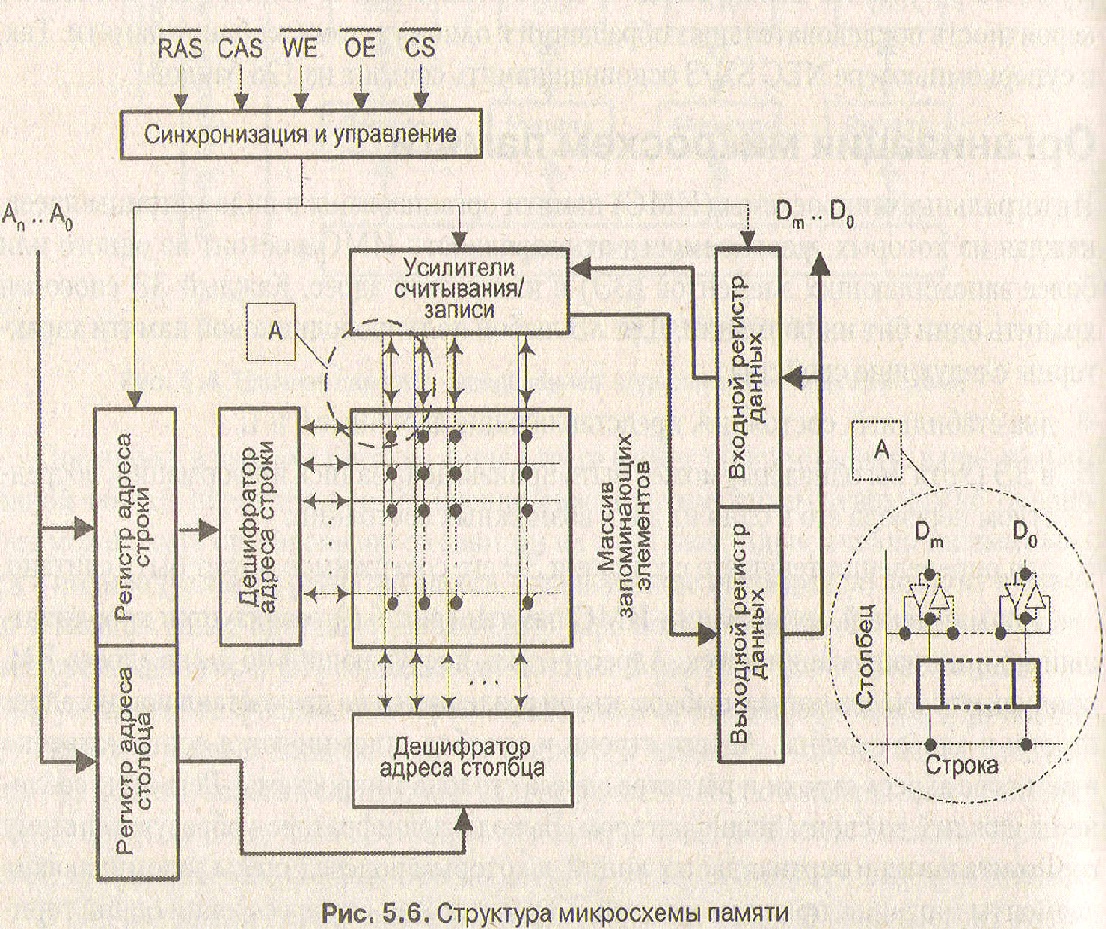

Интегральные микросхемы памяти организованы в виде матрицы ячеек, каждая из которых, в зависимости от разрядности, состоит из одного или более запоминающих элементов (ЗЭ) и имеет свой адрес. Каждый ЗЭ способен хранить один бит информации. При матричной организации ИМС памяти (см. рисунок ниже) реализуется координатный принцип адресации ячеек.

Структурная схема микросхемы памяти

Адрес ячейки, поступающий по шине адреса ЭВМ, пропускается через логику выбора, где он разделяется на две составляющие: адрес строки и адрес столбца. Адреса строки и столбца запоминаются соответственно в регистре адреса строки и регистре адреса столбца микросхемы. Регистры соединяются каждый со своим дешифратором. Выходы дешифраторов образуют систему горизонтальных и вертикальных линий, к которым подсоединены запоминающие элементы матрицы, при этом каждый ЗЭ расположен на пересечении одной горизонтальной и одной вертикальной линии. ЗЭ, объединенные общим горизонтальным проводом, принято называть строкой (row). Запоминающие элементы, подключенные к общему вертикальному проводу, называют столбцом (column). Фактически вертикальных проводов в микросхеме должно быть, по крайней мере, вдвое больше, чем это требуется для адресации, поскольку к каждому ЗЭ необходимо подключить линию, по которой будет передаваться считываемая и записываемая информация. Совокупность запоминающих элементов и логических схем, связанных с выбором строк и столбцов, называют ядром микросхемы памяти. Помимо ядра, в микросхеме имеется еще интерфейсная логика, обеспечивающая взаимодействие ядра с внешним миром. В ее задачи, в частности, входит коммутация нужного столбца на выход при считывании и на вход — при записи. На физическую организацию ядра, как матрицы однобитовых ЗЭ, накладывается логическая организация памяти, под которой понимается разрядность микросхемы, то есть количество линий ввода/вывода. Разрядность микросхемы определяет количество ЗЭ, имеющих один и тот же адрес (такая совокупность запоминающих элементов называется ячейкой), то есть каждый столбец содержит столько разрядов, сколько есть линий ввода/вывода данных. Для уменьшения числа контактов микросхемы адреса строки и столбца в большинстве микросхем подаются через одни и те же контакты последовательно во времени (мультиплексируются) и запоминаются, соответственно, в регистре адреса строки и регистре адреса столбца микросхемы.

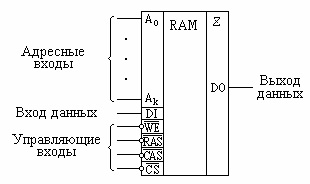

Мультиплексирование обычно реализуется внешней логикой. Для синхронизации процессов фиксации и обработки адресной информации адрес строки (RA) сопровождается сигналом RAS (Row Address Strobe — строб строки), а адрес столбца (СА) — сигналом CAS (Column Address Strobe — строб столбца). Чтобы стробирование было надежным, эти сигналы подаются с задержкой, достаточной для завершения переходных процессов на шине адресаj/I в адресных цепях микросхемы. Сигнал выбора микросхемы CS (Crystal Select) разрешает работу схемы и используется для выбора определенной микросхемы в системах, состоящих из нескольких микросхем. Вход WE (Write Enable — разрешение записи) определяет вид выыполняемой операции (считывание или запись). На все время, пока микросхемы памяти не использует шину данных, информационные выходы микросхемы переводятся в третье (высокоимпедансное) состояние. Управление переключением в третье состояние о6еспечивается сигналом ОЕ (Output Enable — разрешение выдачи выходных сигналов). Этот сигнал активизируется при выполнении операции чтения. На рисунке (см. рисунок ниже) представлено изображение ОЗУ на принципиальных схемах.

Условное изображение ОЗУ

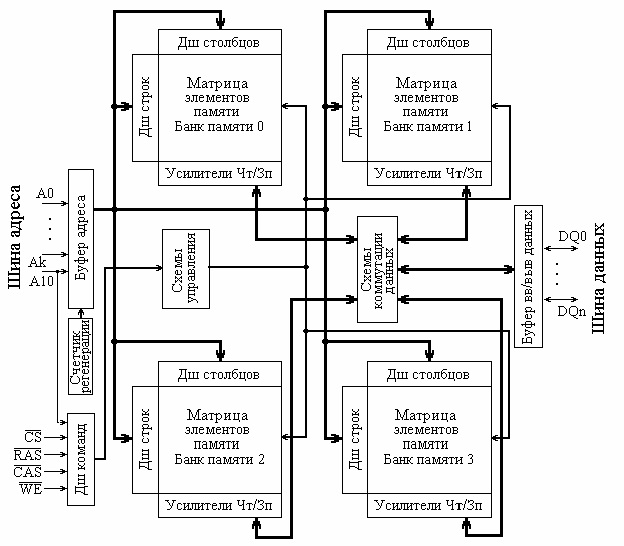

Структурная схема БИС динамического ОЗУ с четырьмя банками памяти показана на рисунке (см. рисунок ниже). Основными ее компонентами являются четыре банка памяти, представляющих собой матрицы элементов памяти с дешифраторами строк и столбцов и усилителями чтения-записи. Кроме собственно банков памяти, в состав ОЗУ входят:

- буфер адреса, фиксирующий адреса строки и столбца;

- счетчик регенерации, формирующий адрес строки, в которой должна выполняться очередная регенерация;

- дешифратор команд, определяющий, какое действие (команду) должна выполнить микросхема в соответствии с поданными управляющими сигналами (и сигналомA10);

- схемы управления, формирующие управляющие сигналы для остальных узлов микросхемы;

- схемы коммутации данных, передающие читаемые или записываемые данные из/в банки памяти;

- буфер ввода/вывода данных, обеспечивающий связь микросхемы памяти с шиной данных.

Управление операциями с основной памятью осуществляется контроллером памяти. Обычно этот контроллер входит в состав центрального процессора или реализуется в виде внешнего по отношению к памяти устройства. В последних микросхемах памяти часть функций контроллера возлагается на микросхему.

Структурная схема БИС динамического ОЗУ

В общем случае на каждую операцию (считывание или запись) требуется как минимум пять тактов, которые используются следующим образом:

1. Указание типа операции (чтение или запись) и установка адреса строки.

2. Формирование сигнала RAS.

3. Установка адреса столбца.

4. Формирование сигнала CAS.

5. Возврат сигналов RAS и CAS в неактивное состояние. Обратная запись.

Типовую процедуру доступа к памяти рассмотрим на примере чтения с мультиплексированием адресов строки столбцов. Сначала на входе WE

устанавливается уровень, соответствующий операции чтения, а на адресные контакты микросхемы подается адрес строки, сопровождаемый сигналом RAS. По заднему фронту этого сигнала адрес запоминается в регистре адреса строки, после чего дешифрируется. После стабилизации процессов, вызванных сигналом RAS, выбранная строка подключается к усилителям считывания/записи (УСЗ). Далее на вход подается адрес столбца, который по заднему фронту сигнала CAS заносится в регистр адреса столбца. Одновременно подготавливается выходной регистр данных, куда после стабилизации сигнала CAS загружается информация с выбранных УСЗ. Разработчики микросхем памяти тратят значительные усилия на повышение быстродействия микросхем. Возможности "ускорения" ядра микросхемы ЗУ весьма ограничены и связаны, в основном, с миниатюризацией запоминающих элементов. Наибольшие успехи достигнуты в интерфейсной части. Касаются они, главным образом, операций чтения, то есть способов доставки содержимого ячейки на шину данных. Наибольшее распространение получили следующие шесть фундаментальных подходов: последовательный, конвейерный, регистровый, страничный, пакетный, удвоенной скорости. Они будут рассмотрены при обсуждении типов микросхем.

Типы микросхем динамических ОЗУ

- Подробности

- Родительская категория: Память. Нижний уровень

- Категория: Микросхемы памяти

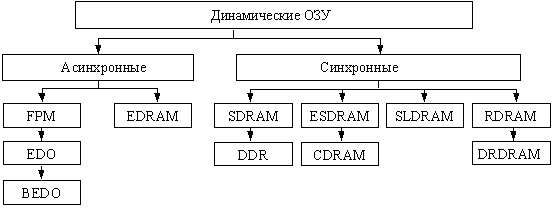

Динамическая память состоит из ядра (массива ЗЭ) и интерфейсной логики (буферных регистров, усилителей чтения данных, схемы регенерации и др.), Хотя количество видов DRAM уже превысило два десятка, ядро у них организовано практически одинаково. Главные различия связаны с интерфейсной логикой, причем различия эти обусловлены также и областью применения микросхем — помимо основной памяти ЭВМ, микросхемы памяти входят, например, в состав видеоадаптеров. Классификация микросхем динамической памяти показана ниже (см. рисунок ниже).

Типы микросхем динамического ОЗУ

Теперь рассмотрим различные типы микросхем динамической памяти DRAM. На начальном этапе это были микросхемы асинхронной памяти, работа которых не привязана жестко к тактовым импульсам системной шины. Асинхронной памяти свойственны дополнительные затраты времени на взаимодействие микросхем памяти и контроллера. Так, в асинхронной схеме сигнал RAS будет сформирован только после поступления в контроллер тактирующего импульса и будет воспринят микросхемой памяти через некоторое время.

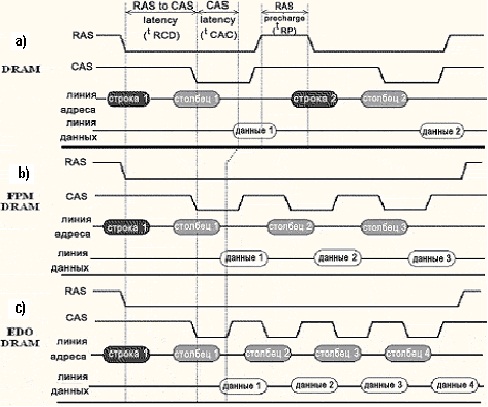

Микросхемы DRAM. В первых микросхемах динамической памяти применялся наиболее простой способ обмена данными. Он позволял считывать и записывать строку памяти только на каждый пятый такт (см. рисунок ниже "a"). Этапы такой процедуры были описаны ранее. Традиционной DRAM соответствует формула 5-5-5-5. Микросхемы данного типа могли работать на частотах до 40 МГц и из-за своей медлительности (время доступа составляло около 120 нс) просуществовали недолго.

Микросхемы FРМ DRAM. Микросхемы динамического ОЗУ, реализующие режим FPM (Fast Page Mode), также относятся к ранним типам DRAM. В основе лежит следующая идея. Доступ к ячейкам, лежащим в одной строке матрицы, можно проводить быстрее. Для доступа к очередной ячейке достаточно подавать на микросхему лишь адрес нового столбца, сопровождая его сигналом CAS. Полный же адрес (строки и столбца) передается только при первом обращении к строке. Сигнал RAS остается активным на протяжении всего страничного цикла и позволяет заносить в регистр адреса столбца новую информацию не по спадающему фронту CAS, а как только адрес на входе стабилизируется, то есть практически по переднему фронту сигнала CAS. Схема чтения для FPM DRAM (см. рисунок ниже "b") описывается формулой 5-3-3-3 (всего 14 тактов). Применение схемы быстрого страничного доступа позволило сократить время доступа до 60 нс.

Микросхемы EDO DRAM. Следующим этапом в развитии динамических ОЗУ стали микросхемы с гuперстраничным режимом доступа (НРМ, Нурег Page Mode), более известные как EDO (Extended Data Output — расширенное время удержания данных на выходе). Главная особенность технологии — увеличенное по cpaвнению с FPM DRAM время доступности данных на выходе микросхемы. В микросхемах FPM DRAM выходные данные остаются действительными только при активном сигнале CAS, за счет чего во втором и последующих доступах к строке нужно три такта: такт переключения CAS в активное состояние, такт считывания данных и такт переключения CAS в неактивное состояние. В EDO DRAM по активному (спадающему) фронту сигнала CAS данные запоминаются во внутреннем регистре, где хранятся еще некоторое время после того, как поступит следующий активный фронт сигнала. Это позволяет использовать хранимые данные, когда CAS уже переведен в неактивное состояние. Схема чтения у EDO DRAM уже 5-2- 2-2 (см. рисунок ниже "c"), что на 20% быстрее, чем у FPM. Время доступа составляет порядка 30-40 нс.

Временные диаграммы DRAM, FPM DRAM, EDO DRAM

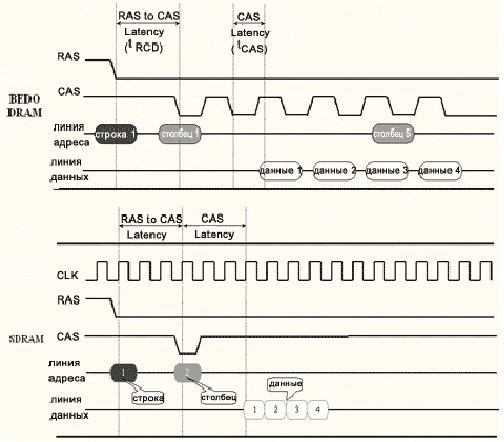

Микросхемы BEDO DRAM. Технология EDO была усовершенствована компанией VIА Technologies. Новая модификация EDO известна как BEDO (Burst EDO — пакетная EDO). Новизна метода в том, что при первом обращении считывается вся строка микросхемы, в которую входят последовательные слова пакета. За последовательной пересылкой слов (переключением столбцов) автоматически следит внутренний счетчик микросхемы. Это исключает необходимость выдавать адреса для всех ячеек пакета, но требует поддержки со стороны внешней логики. Способ позволяет сократить время считывания второго и последующих слов еще на один такт (см. рисунок ниже), благодаря чему формула приобретает вид 5-1-1-1.

Микросхемы SDRAM. Аббревиатура SDRAM (Sуnchrоnous DRAM — Синхронная DRAM) используется для обозначения микросхем "обычных" синхронных динамических ОЗУ. Кардинальные отличия SDRAM от рассмотренных выше асинхронных динамических ОЗУ можно свести к четырем положениям:

•синхронный метод передачи данных на шину;

•применение нескольких (двух или четырех) внутренних банков памяти;

•конвейерный механизм пересылки пакета;

•передача части функций контроллера памяти логике самой микросхемы.

Синхронность памяти позволяет контроллеру памяти "знать" моменты готовности данных, за счет чего снижаются издержки циклов ожидания и поиска данных. Так как данные появляются на выходе микросхемы одновременно с тактовыми импульсами, упрощается взаимодействие памяти с другими устройствами ЭВМ.В отличие от ВЕDО конвейер позволяет передавать данные пакета по тактам, благодаря чему ОЗУ может работать бесперебойно на более высоких частотах, чем асинхронные ОЗУ.

Временные диаграммы BEDO DRAM, SDRAM

Микросхемы DDR SDRAM. Важным этапом в дальнейшем развитии технологии SDRAM стала DDR SDRAM (Double Data Rate SDRAM — SDRAM с удвоенной скоростью передачи данных). В отличие от SDRAM, новая модификация выдает данные в пакетном режиме по обоим фронтам импульса синхронизации, из-за чего пропускная способность возрастает вдвое.

Микросхемы RDRAM, DRDRAM. Принципиально отличный подход к построению DRAM был предложен компанией Rambus в 1997 году. В нем используется оригинальная система обмена данными между ядром и контроллером памяти. В таблице (см. таблица ниже) приведены сравнительные характеристики перечисленных выше микросхем памяти. Ведутся работы по повышению быстродействия, в частности, связанные с применением КЭШ в микросхемах (CDRAM).

Сравнительные характеристики микросхем памяти

Модули динамической памяти

- Подробности

- Родительская категория: Память. Нижний уровень

- Категория: Микросхемы памяти

Модули динамической полупроводниковой памяти прошли эволюцию от набора микросхем, устанавливаемых на системной плате и заметных по своему регулярному расположению (несколько смежных рядов одинаковых микросхем), до отдельных небольших плат, вставляемых в стандартный разъем (слот) системной платы. Первенство в создании таких модулей памяти обычно относят к фирме IBM. Основными разновидностями модулей динамических оперативных ЗУ с момента их оформления в виде самостоятельных единиц были:

•30-контактные однобайтные модули SIMM (DRAM);

•72-контактные четырехбайтные модули SIMM (DRAM);

•168-контактные восьмибайтные модули DIMM (SDRAM);

•184-контактные восьмибайтные модули DIMM (DDR SDRAM);

•184-контактные (20 из них не заняты) двухбайтные модули RIMM RDDRAM).

Сокращение SIMM означает Single In-Line Memory Module — модуль памяти с одним рядом контактов, так как контакты краевого разъема модуля, расположенные в одинаковых позициях с двух сторон платы, электрически соединены. Соответственно, DIMM значит Dual In-Line Memory Module — модуль памяти с двумя рядами контактов. А вот RIMM означает Rambus Memory Module — модуль памяти типа Rambus. Кроме этих модулей, имеются также варианты для малогабаритных компьютеров, для графических карт и некоторые другие.

Если микросхемы памяти физически располагаются только с одной стороны платы, то такой модуль называют односторонним, а если с двух сторон — то двухсторонним. При равной емкости модулей у двухстороннего модуля количество микросхем больше, поэтому на каждую линию шины данных приходится большая нагрузка, чем при использовании одностороннего. С этой точки зрения односторонние модули предпочтительней двусторонних. Однако количество банков в двусторонних модулях вдвое больше, чем в односторонних, поэтому при определенных условиях и хорошем контроллере памяти двусторонний модуль может обеспечить несколько большую производительность.

Помимо собственно конструктивной организации и типа памяти, модули имеют также и некоторые другие различия. Одним из таких различий является возможность (или ее отсутствие) контроля хранимых данных.

Контроль может основываться на использовании дополнительных (по одному на каждый хранимый байт) битов четности (Parity bits), т.е. в этом случае каждый байт занимает в памяти по 9 бит. Такой контроль позволяет выявить ошибки при считывании хранимой информации из памяти, но не исправить их. Более сложный контроль предполагает использование кодов, корректирующих ошибки, — ECC (Error Correcting Codes). Эти коды позволяют обнаруживать ошибки большей кратности, чем одиночные, а одиночные ошибки могут быть исправлены. Подобные схемы используются в серверных конфигурациях, когда требуется повышенная надежность. Память, устанавливаемая в настольные ПЭВМ, обычно не имеет никакого контроля.

Кроме того, известны также различные модификации схем контроля, вплоть до просто имитирующих контрольные функции, но не осуществляющие их, например, с генерацией всегда верного бита четности.

Модули DIMM также различаются по наличию или отсутствию в них буферных схем на шинах адреса и управляющих сигналов. Небуферизованные (unbuffered) модули больше нагружают эти шины, но более быстродействующие и дешевые. Их обычно применяют в настольных ЭВМ. Буферизованные (registered) имеют буферные регистры и, обеспечивая меньшую нагрузку на шины, позволяют подключить к ней большее количество модулей. Однако эти регистры несколько снижают быстродействие памяти, требуя лишнего такта задержки. Применяют буферизованные модули обычно в серверных системах.

Еще одной особенностью, различающей модули динамической памяти, является способ, посредством которого после включения компьютера определяется объем и тип установленной в нем памяти.

В первых персональных ЭВМ объем и быстродействие установленной памяти задавались переключателями (джамперами — jumpers), расположенными на системной плате. С появлением модулей SIMM (существовали также похожие на них модули SIPP) стал использоваться так называемый параллельный метод идентификации (parallel presence detect), при котором краевой разъем модуля имел дополнительные контакты, используемые только для целей указания присутствия модуля в том слоте, где он установлен, его объема и времени обращения. В самых первых (30-контактных) модулях таких дополнительных контактов было только два, в 72-контактных модулях их стало четыре: два указывали на объем модуля и два — на время обращения. Эти контакты могли заземляться непосредственно на модуле, что позволяло различить четыре вида модулей по объему и четыре по времени доступа.

Попытки использовать этот же прием в последующих модулях потребовали увеличения количества таких контактов, но решить все проблемы идентификации не смогли. Поэтому, начиная c модулей DIMM, используют так называемый последовательный способ идентификации (Serial Presence Detect — SPD), при котором на плату модуля устанавливается специальная дополнительная микросхема, так называемый SPD-чип, представляющая собой небольшую постоянную память на 128 или 256 байт с последовательным (I2C) интерфейсом доступа. В этой микросхеме записана основная информация об изготовителе микросхемы и ее параметрах. Формат этих данных стандартный, определенный советом JEDEC (Joint Electron Devices Engineering Council), стандартов которого придерживаются все изготовители полупроводниковой памяти.

Регенерация памяти

- Подробности

- Родительская категория: Память. Нижний уровень

- Категория: Микросхемы памяти

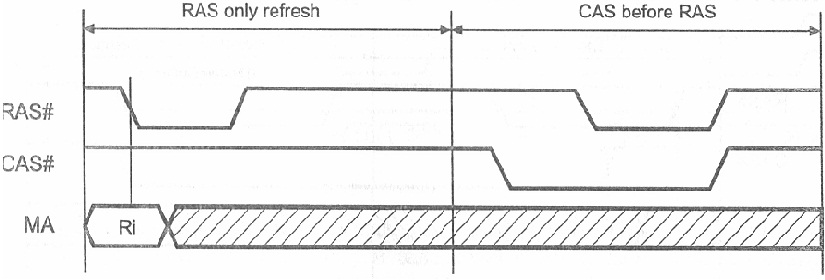

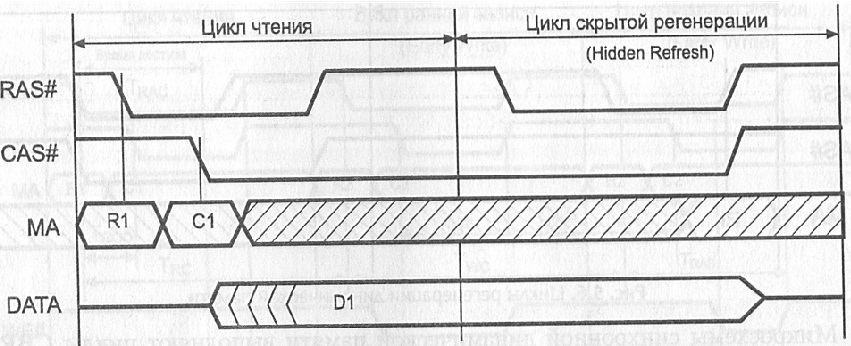

В различных типах микросхем динамической памяти нашли применение три основные метода регенерации (см. рисунок ниже):

1. одним сигналом RAS (ROR — RAS Only Refresh);

2. сигналом CAS, предваряющим, сигнал RAS (CBR — CAS Before RAS);

3. скрытая и автоматическая регенерация (SR — Self Refresh).

Временные диаграммы регенерации памяти в режимах ROR, CBR

Регенерация одним RAS использовалась еще в первых микросхемах DRAM. На шину адреса выдается адрес регенерируемой строки, сопровождаемый сигналом RAS. При этом выбирается строка ячеек и хранящиеся там данные поступают во внутренние цепи микросхемы, после чего записываются обратно. Так как сигнал CAS не появляется, цикл чтения/записи не начинается. В следующий раз на шину адреса подается адрес следующей строки и т. д., пока не восстановятся все строки, после чего цикл повторяется. К недостаткам метода можно отнести занятость шины адреса в момент регенерации, когда доступ к другим устройствам блокирован. Особенность метода CBR в том, что если в обычном цикле чтения/ записи сигнал RAS всегда предшествует сигналу CAS, то при появлении сигнала CAS первым начинается специальный цикл регенерации. В этом случае адрес строки не передается, а микросхема использует свой внутренний счетчик, содержимое которого увеличивается на единицу при каждом очередном СВR-цикле. Режим позволяет регенерировать память, не занимая шину адреса, то есть более эффективен (см. рисунок ниже).

Временные диаграммы регенерации памяти в режиме CBR — скрытой регенерации

Обнаружение и исправление ошибок

- Подробности

- Родительская категория: Память. Нижний уровень

- Категория: Микросхемы памяти

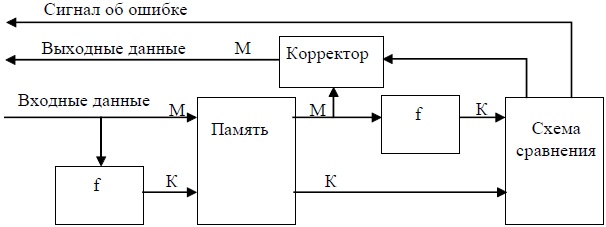

При работе с полупроводниковой памятью не исключено возникновение различного рода отказов и сбоев. Причиной отказов могут быть производственные дефекты, повреждение микросхем или их физический износ. Проявляются отказы в том, что в отдельных разрядах одной или нескольких ячеек постоянно считывается 0 или 1, вне зависимости от реально записанной туда информации. Сбой — это случайное событие, выражающееся в неверном считывании или записи информации в отдельных разрядах одной или нескольких ячеек, не связанное с дефектами микросхемы. Сбои обычно обусловлены проблемами с источником питания или с воздействием альфа-частиц, возникающих в результате распада радиоактивных элементов, которые в небольших количествах присутствуют практически в любых материалах. Как отказы, так и сбои крайне нежелательны, поэтому в большинстве систем основной памяти содержатся схемы, служащие для обнаружения и исправления ошибок. Вне зависимости от того, как именно реализуется контроль и исправление ошибок, в основе их всегда лежит введение избыточности. Это означает, что контролируемые разряды дополняются контрольными разрядами, благодаря которым и возможно детектирование ошибок, а в ряде методов — их коррекция. Общую схему обнаружения и исправления ошибок иллюстрирует рисунок ниже.

Схема памяти с обнаружением и исправлением ошибок

На рисунке показано, каким образом осуществляются обнаружение и исправление ошибок. Перед записью М-разрядных данных в память производится их обработка, обозначенная на схеме функцией f, в результате которой формируется добавочный К-разрядный код. В память заносятся как данные, так и этот вычисленный код, то есть (М + К)-разрядная информация. При чтении информации повторно формируется К-разрядный код, который сравнивается с аналогичным кодом, считанным из ячейки. Сравнение приводит к одному из трех результатов:

•Не обнаружено ни одной ошибки. Извлеченные из ячейки данные подаются на выход памяти.

•Обнаружена ошибка, и она может быть исправлена. Биты данных и добавочного кода подаются на схему коррекции. После исправления ошибки данные поступают на выход памяти.

•Обнаружена ошибка, и она не может быть исправлена. Выдается сообщение о неисправимой ошибке.

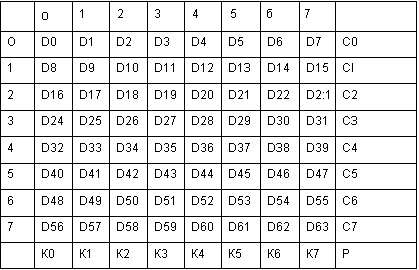

Коды, используемые для подобных операций, называют корректирующими кодами или кодами с исправлением ошибок Простейший вид такого кода основан на добавлении к каждому байту информации одного бита паритета. Бит паритета — это дополнительный бит, значение которого устанавливается таким, чтобы суммарное число единиц в данных, с учетом этого дополнительного разряда, было четным (или нечетным). В ряде систем за основу берется четность, в иных — нечетность. Простейший вариант корректирующего кода также может быть построен на базе битов паритета. Для этого биты данных представляются в виде матрицы, к каждой строке и столбцу которой добавляется бит паритета. Для 64-разрядных данных этот подход иллюстрирует таблица ниже.

Пример корректирующего кода

Здесь D — биты данных, С — столбец битов паритета строк, К — строка битов паритета столбцов, Р — бит паритета, контролирующий столбец С и строку К. Таким образом, к 64 битам данных нужно добавить 17 бит паритета: по 8 бит на строки и столбцы и один дополнительный бит для контроля строки и столбца битов паритета. Если в одной строке и одном столбце обнаружено нарушение паритета, для исправления ошибки достаточно просто инвертировать бит на пересечении этих строки и столбца. Если ошибка паритета выявлена только в одной строке или только одном столбце либо одновременно в нескольких строках и столбцах, фиксируется многобитовая ошибка и формируется признак невозможности коррекции.

Недостаток рассмотренного приема в том, что он требует большого числа дополнительных разрядов. Более эффективным представляется код, предложенный Ричардом Хэммингом и носящий его имя (код Хэмминга).

Еще статьи...

Не жаждете тратить огромные суммы за интимнейший отдых. Веб сайт https://prostitutkicheboksaryxx.com предлагает снять обаятельных проституток, не в урон наполнению портмоне и суперкачеству их секс услуг.