Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

Отдохните в санатории "Красная Пахра" на программе лечения пневмонии. Для классического стиля на vegas-glass.ru представлены шторки на ванну с профилем белого цвета.

Память. Нижний уровень

Типы микросхем динамических ОЗУ

- Подробности

- Родительская категория: Память. Нижний уровень

- Категория: Микросхемы памяти

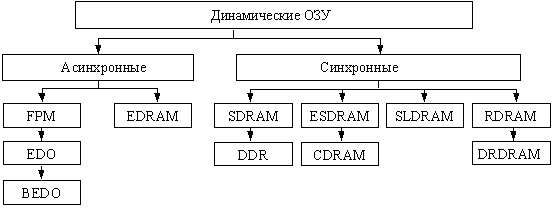

Динамическая память состоит из ядра (массива ЗЭ) и интерфейсной логики (буферных регистров, усилителей чтения данных, схемы регенерации и др.), Хотя количество видов DRAM уже превысило два десятка, ядро у них организовано практически одинаково. Главные различия связаны с интерфейсной логикой, причем различия эти обусловлены также и областью применения микросхем — помимо основной памяти ЭВМ, микросхемы памяти входят, например, в состав видеоадаптеров. Классификация микросхем динамической памяти показана ниже (см. рисунок ниже).

Типы микросхем динамического ОЗУ

Теперь рассмотрим различные типы микросхем динамической памяти DRAM. На начальном этапе это были микросхемы асинхронной памяти, работа которых не привязана жестко к тактовым импульсам системной шины. Асинхронной памяти свойственны дополнительные затраты времени на взаимодействие микросхем памяти и контроллера. Так, в асинхронной схеме сигнал RAS будет сформирован только после поступления в контроллер тактирующего импульса и будет воспринят микросхемой памяти через некоторое время.

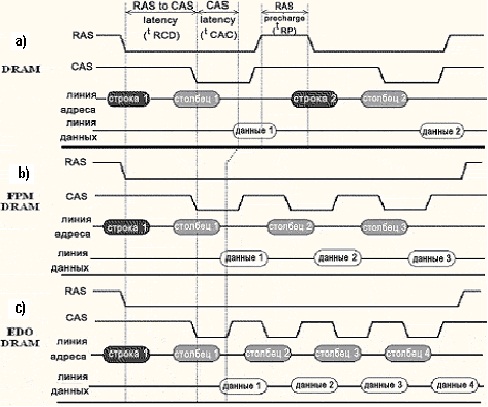

Микросхемы DRAM. В первых микросхемах динамической памяти применялся наиболее простой способ обмена данными. Он позволял считывать и записывать строку памяти только на каждый пятый такт (см. рисунок ниже "a"). Этапы такой процедуры были описаны ранее. Традиционной DRAM соответствует формула 5-5-5-5. Микросхемы данного типа могли работать на частотах до 40 МГц и из-за своей медлительности (время доступа составляло около 120 нс) просуществовали недолго.

Микросхемы FРМ DRAM. Микросхемы динамического ОЗУ, реализующие режим FPM (Fast Page Mode), также относятся к ранним типам DRAM. В основе лежит следующая идея. Доступ к ячейкам, лежащим в одной строке матрицы, можно проводить быстрее. Для доступа к очередной ячейке достаточно подавать на микросхему лишь адрес нового столбца, сопровождая его сигналом CAS. Полный же адрес (строки и столбца) передается только при первом обращении к строке. Сигнал RAS остается активным на протяжении всего страничного цикла и позволяет заносить в регистр адреса столбца новую информацию не по спадающему фронту CAS, а как только адрес на входе стабилизируется, то есть практически по переднему фронту сигнала CAS. Схема чтения для FPM DRAM (см. рисунок ниже "b") описывается формулой 5-3-3-3 (всего 14 тактов). Применение схемы быстрого страничного доступа позволило сократить время доступа до 60 нс.

Микросхемы EDO DRAM. Следующим этапом в развитии динамических ОЗУ стали микросхемы с гuперстраничным режимом доступа (НРМ, Нурег Page Mode), более известные как EDO (Extended Data Output — расширенное время удержания данных на выходе). Главная особенность технологии — увеличенное по cpaвнению с FPM DRAM время доступности данных на выходе микросхемы. В микросхемах FPM DRAM выходные данные остаются действительными только при активном сигнале CAS, за счет чего во втором и последующих доступах к строке нужно три такта: такт переключения CAS в активное состояние, такт считывания данных и такт переключения CAS в неактивное состояние. В EDO DRAM по активному (спадающему) фронту сигнала CAS данные запоминаются во внутреннем регистре, где хранятся еще некоторое время после того, как поступит следующий активный фронт сигнала. Это позволяет использовать хранимые данные, когда CAS уже переведен в неактивное состояние. Схема чтения у EDO DRAM уже 5-2- 2-2 (см. рисунок ниже "c"), что на 20% быстрее, чем у FPM. Время доступа составляет порядка 30-40 нс.

Временные диаграммы DRAM, FPM DRAM, EDO DRAM

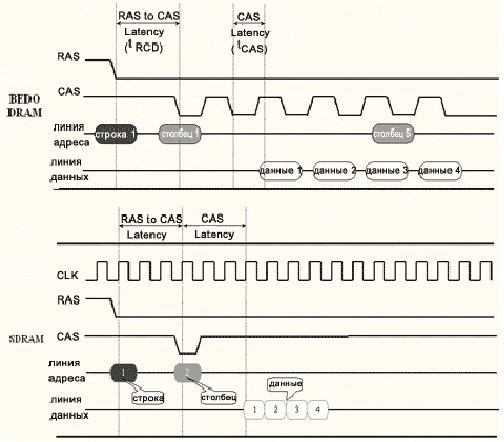

Микросхемы BEDO DRAM. Технология EDO была усовершенствована компанией VIА Technologies. Новая модификация EDO известна как BEDO (Burst EDO — пакетная EDO). Новизна метода в том, что при первом обращении считывается вся строка микросхемы, в которую входят последовательные слова пакета. За последовательной пересылкой слов (переключением столбцов) автоматически следит внутренний счетчик микросхемы. Это исключает необходимость выдавать адреса для всех ячеек пакета, но требует поддержки со стороны внешней логики. Способ позволяет сократить время считывания второго и последующих слов еще на один такт (см. рисунок ниже), благодаря чему формула приобретает вид 5-1-1-1.

Микросхемы SDRAM. Аббревиатура SDRAM (Sуnchrоnous DRAM — Синхронная DRAM) используется для обозначения микросхем "обычных" синхронных динамических ОЗУ. Кардинальные отличия SDRAM от рассмотренных выше асинхронных динамических ОЗУ можно свести к четырем положениям:

•синхронный метод передачи данных на шину;

•применение нескольких (двух или четырех) внутренних банков памяти;

•конвейерный механизм пересылки пакета;

•передача части функций контроллера памяти логике самой микросхемы.

Синхронность памяти позволяет контроллеру памяти "знать" моменты готовности данных, за счет чего снижаются издержки циклов ожидания и поиска данных. Так как данные появляются на выходе микросхемы одновременно с тактовыми импульсами, упрощается взаимодействие памяти с другими устройствами ЭВМ.В отличие от ВЕDО конвейер позволяет передавать данные пакета по тактам, благодаря чему ОЗУ может работать бесперебойно на более высоких частотах, чем асинхронные ОЗУ.

Временные диаграммы BEDO DRAM, SDRAM

Микросхемы DDR SDRAM. Важным этапом в дальнейшем развитии технологии SDRAM стала DDR SDRAM (Double Data Rate SDRAM — SDRAM с удвоенной скоростью передачи данных). В отличие от SDRAM, новая модификация выдает данные в пакетном режиме по обоим фронтам импульса синхронизации, из-за чего пропускная способность возрастает вдвое.

Микросхемы RDRAM, DRDRAM. Принципиально отличный подход к построению DRAM был предложен компанией Rambus в 1997 году. В нем используется оригинальная система обмена данными между ядром и контроллером памяти. В таблице (см. таблица ниже) приведены сравнительные характеристики перечисленных выше микросхем памяти. Ведутся работы по повышению быстродействия, в частности, связанные с применением КЭШ в микросхемах (CDRAM).