Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

PCI и PCI-X

Протокол, команды и транзакции шин PCI и PCI-X

Контроль достоверности передачи и обработка ошибок

Для контроля достоверности передачи информации на шине PCI применяется проверка четности адреса и данных; в PCI-X используется и ECC-контроль с исправлением однобитных ошибок. ECC-контроль обязателен при работе в Mode 2, он может использоваться и при работе в Mode 1. Метод контроля достоверности сообщается мостом в шаблоне инициализации по окончании аппаратного сброса шины. Мост выбирает тот метод контроля, который поддерживают все абоненты его вторичной шины (и он сам). Для сообщения об ошибках служат сигналы PERR# (протокольная сигнализация между устройствами) и SERR# (сигнал фатальной ошибки, вызывающий, как правило, немаскируемое прерывание системы).

При контроле четности используются сигналы PAR и PAR64, обеспечивающие четность числа «единиц» на наборах линий AD[31:0], C/BE[3:0]#, PAR и AD[63:32], C/BE[7:4]#, PAR64. Сигналы четности PAR и PAR64 вырабатываются тем устройством, которое в данный момент управляет шиной AD (выводит команду и адрес, атрибуты или данные). Сигналы четности в режиме PCI вырабатываются с задержкой на один такт относительно контролируемых ими линий AD и C/BE#. В PCI-X при операциях чтения правила немного иные: биты четности в такте N относятся к битам данных такта N — 1 и сигналам C/BE# такта N — 2. Сигналы PERR# и SERR# вырабатываются приемником информации в такте, следующем за тактом, в котором нарушено условие четности.

При ECC-контроле в 32-разрядном режиме для контроля линий AD[31:0] и C/BE[3:0]# применяется 7-битный код ECC с сигналами ECC[6:0]; в 64-разрядном режиме применяется 8-битный код с сигналами ECC[7:0]; в 16-разрядном режиме применяется несколько измененная схема ECC7 + 1. В любом из режимов ECC-контроль позволяет исправлять только одиночные ошибки и обнаруживать большинство ошибок с большей кратностью. Исправление ошибок может быть запрещено программно (через регистр управления ECC-контролем), при этом обнаруживаются все ошибки кратности 1, 2 и 3. В любом случае в регистрах ECCконтроля сохраняется диагностическая информация. Биты ECC выводятся на шину по тем же правилам и с теми же задержками, как и биты четности. Однако сигналы PERR# и SERR# вырабатываются приемником информации через такт после действительных бит ECC — «лишний» такт отдается на анализ синдрома ECC и попытку исправления ошибки.

Обнаруженная ошибка четности, как и ошибка более чем в одном бите, обнаруженная при ECC-контроле, считается неисправимой (unrecoverable). Достоверность информации в фазе адреса, а в PCI-X и в фазе атрибутов, проверяется целевым устройством. В случае обнаружения неисправимой ошибки в этих фазах целевое устройство подает сигнал SERR# (в течение одного такта) и устанавливает в своем регистре состояния бит 14 — Signaled System Error. В фазе данных достоверность проверяет устройство-приемник данных; в случае обнаружения неисправимой ошибки оно подает сигнал PERR# и устанавливает в своем регистре состояния бит 15 — Detected Parity Error.

В регистре состояния устройства имеется бит 8 (Master Data Parity Error), который отражает неудачу выполнения транзакции (последовательности) из-за обнаруженной ошибки данных. В PCI и PCI-X его правила установки формально различны:

- в PCI этот бит устанавливается только инициатором транзакции, когда он сам ввел (при чтении) или обнаружил (при записи) сигнал PERR#;

- в PCI-X этот бит устанавливается запросчиком транзакции или мостом: будучи инициатором команд чтения, мост обнаруживает ошибку в данных; будучи инициатором команд записи, мост обнаруживает сигнал PERR#; будучи целевым устройством, мост получает данные завершения с ошибкой или сообщение завершения с ошибкой транзакции записи от одного из устройств.

В случае обнаружения ошибки данных у устройства PCI-X и его драйвера есть два варианта поведения:

- не пытаясь выполнить какие-то действия по восстановлению и продолжению работы, подать сигнал SERR# — это сигнал катастрофической ошибки, который может трактоваться ОС как повод к перезагрузке. Для устройств PCI это единственно возможный вариант поведения;

- не подавать сигнал SERR#, а пытаться обработать ошибку самостоятельно. Это можно делать только программно с учетом всех возможных побочных эффектов от лишних операций (простой повтор чтения может, например, привести к потере данных).

Выбор варианта поведения обеспечивается установкой бита 0 (Uncorrectable Data Error Recovery Enable) в регистре PCI-X Command. По умолчанию (после сброса) он обнулен — по ошибке данных устанавливается сигнал SERR#; иной вариант должен выбирать драйвер, «умеющий» самостоятельно обрабатывать ошибки. Обнаружение ошибки в фазе адреса или атрибутов всегда является фатальной ошибкой.

Инициатор (запросчик) транзакции должен иметь возможность уведомить драйвер об отвержении транзакции по условию Master Abort (нет ответа от целевого устройства) или Target Abort (отказ целевого устройства), используя прерывания или другие подходящие средства. Если такое уведомление невозможно, устройство должно подавать сигнал SERR#.

Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

Как было сказано выше, шина PCI не предоставляет возможности прямого доступа к памяти с использованием централизованного контроллера в стиле 8237A (как для шины ISA). Для разгрузки центрального процессора от рутинных перекачек данных предлагается прямое управление шиной со стороны устройств, называемых ведущими устройствами шины (PCI Bus Master). Степень интеллектуальности ведущего устройства может быть различной. В простейшем варианте ведущее устройство обеспечивает пересылку блоков данных между устройством и системной памятью (или памятью других устройств) по указанию от CPU. Здесь CPU командами обращения к определенным регистрам ведущего устройства задает начальный адрес, длину блока, направление пересылки и разрешает запуск передачи. После этого пересылка выполняется по готовности (или инициативе) устройства, без отвлечения CPU. Таким образом выполняется прямой доступ к памяти (DMA). Более сложный контроллер DMA может организовывать сцепку буферов при чтении, разбросанную запись и т. п. — возможности, знакомые еще по «продвинутым» контроллерам DMA для ISA/EISA. Более интеллектуальное ведущее устройство, как правило, обладающее собственным микроконтроллером, не ограничивается такой простой работой по указке CPU — оно выполняет обмены уже по программе своего контроллера. Таким интеллектом обладают, например, хост-контроллеры последовательных шин USB и IEEE 1394, рассмотренные в данной книге.

Для совместимости устройств PCI со старым PC-ориентированным ПО и упрощения устройств PCI фирма Intel разработала специальный протокол PC/PCI DMA, позволяющий централизованно эмулировать стандартную (для PC) связку контроллеров DMA 8237. Альтернативное решение — механизм DDMA (Distributed DMA — распределенный DMA) позволяет «расчленить» стандартный контроллер и отдельные его каналы эмулировать средствами карт PCI. Оба этих механизма реализуемы только как часть моста между первичной шиной PCI и шиной ISA, поэтому их поддержка может обеспечиваться (или не обеспечиваться) только на системной плате и разрешаться в CMOS Setup.

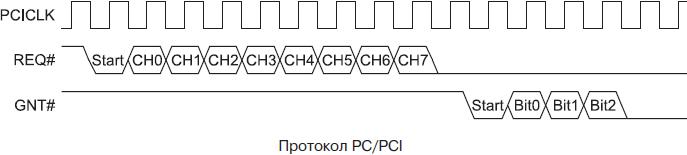

Для поддержки протокола PC/PCI главный мост PCI комбинируется с контроллером DMA, программно-совместимым с парой 8237. Так, например, в хабе-контроллере ввода/вывода ICH3 (микросхема 82801CA фирмы Intel) имеется 7-канальный контроллер DMA, у которого любой из каналов может быть подключен к протоколу PC/PCI или шине LPC. Подключением каналов к тому или иному протоколу управляет специальный 16-битный регистр (смещение 90h в конфигурационном пространстве нулевой функции устройства ICH), в котором каждому каналу отводится пара бит. Хаб ICH является и главным мостом PCI, обеспечивая, естественно, и функции арбитража для абонентов шины, включая и свои интегрированные устройства. В протоколе PC/PCI меняется назначение пары сигналов REQi# и GNTi# для заранее выбранного агента шины PCI, являющегося «проводником» DMA. Этот агент имеет внешние (по отношению к шине PCI) пары сигналов DRQx# и DACKx# с логикой, аналогичной одноименным сигналам ISA DMA, а линии REQi# и GNTi# в процессе запроса управления шиной использует особым образом (см. рисунок ниже). Когда агент получает запрос DRQx (один или несколько), он по линии REQi# передает в последовательном коде состояние активности линий запросов DRQx. В первом такте CLK передается старт-бит — низкий уровень REQi#, во втором — активность запроса DRQ0, затем DRQ1 и так далее до DRQ7, после чего сохраняется низкий уровень REQ#. На это сообщение хаб1 ответит по линии GNTi# посылкой с указанием номера канала, которому дается подтверждение DACKx# для передачи данных в последующих транзакциях.

Далее хаб (как инициатор на PCI) организует передачу данных между агентом PCI DMA и памятью, при этом направлением передачи и текущим адресом в памяти управляет контроллер 8237, находящийся в том же хабе. Во время этой передачи сигнал GNTi# остается активным. Передача каждого байта или слова данных ведется не за один шинный цикл, как в ISA DMA, а за пару шинных циклов PCI: в одном цикле происходит обращение к памяти, в другом — к агенту PCI DMA. Порядок циклов определяется направлением передачи (понятно, что в первом цикле данные должны быть считаны, а во втором — записаны). В этих циклах данные передаются только по линиям AD[7:0] при работе с 8-битными каналами и по AD[15:0] при работе с 16-битными с соответствующими сигналами BE[3:0]#. В цикле обращения к памяти (команда Memory Read или Memory Write) фигурирует адрес памяти, сформированный соответствующим каналом 8237. В цикле ввода/вывода (обращения к агенту) команды IO Read или IO Write адресуются к специальным адресам:

- 00h — передача данных;

- 04h — передача данных с признаком конца цикла (сигнал TC контроллера 8237).

Кроме передачи данных протокол PC/PCI позволяет эмулировать и режим верификации DMA (без передачи данных), здесь используется команда IO Read с другими адресами:

- C0h — верификация данных;

- C4h — верификация данных с признаком конца цикла.

Агент должен сообщать хабу обо всех изменениях состояний линий запросов DRQx, в том числе и о снятии сигналов запроса. Если агент сигнализирует об установке более одной линии запроса, то после того, как какой-то из них будет обслужен, агент должен повторить посылку запроса для необслуженного канала. Для посылки новой информации о запросах агент на один такт снимает сигнал REQi# и снова вводит посылку запроса, начинающуюся со старт-бита. О снятии DRQx, соответствующего обслуживаемому в данный момент каналу, агент сигнализирует снятием сигнала REQi# на два такта PCI; это он должен сделать за 7 тактов до подачи им сигнала TRDY# в цикле ввода/вывода, иначе хаб начнет следующий цикл передачи.

Механизм PC/PCI DMA реализуют только в чипсете системной платы. В частности, вышеупомянутый хаб ICH3 позволяет запрограммировать на поддержку PC/PCI не более двух пар сигнальных линий REQi# и GNTi#. При этом данные линии не смогут использоваться для обычного арбитража устройств PCI. Сам агент PCI DMA тоже должен находиться на системной плате, он обеспечивает каналами DMA устройства шины ISA. Поддержку PC/PCI можно разрешать и запрещать через CMOS Setup. Через слоты PCI протокол PC/PCI, очевидно, не используется: упоминаний о механизме «объяснения» устройствам PCI, как должны использоваться их линии GNT#/REQ# (штатно или по протоколу PC/PCI), автору найти не удалось.