Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

Фольма ткань 160 20 купить фольма ткань Судизол.

Процессоры

Технология Trace Cache

- Подробности

- Родительская категория: Процессоры

- Категория: Архитектура процессоров Pentium 4

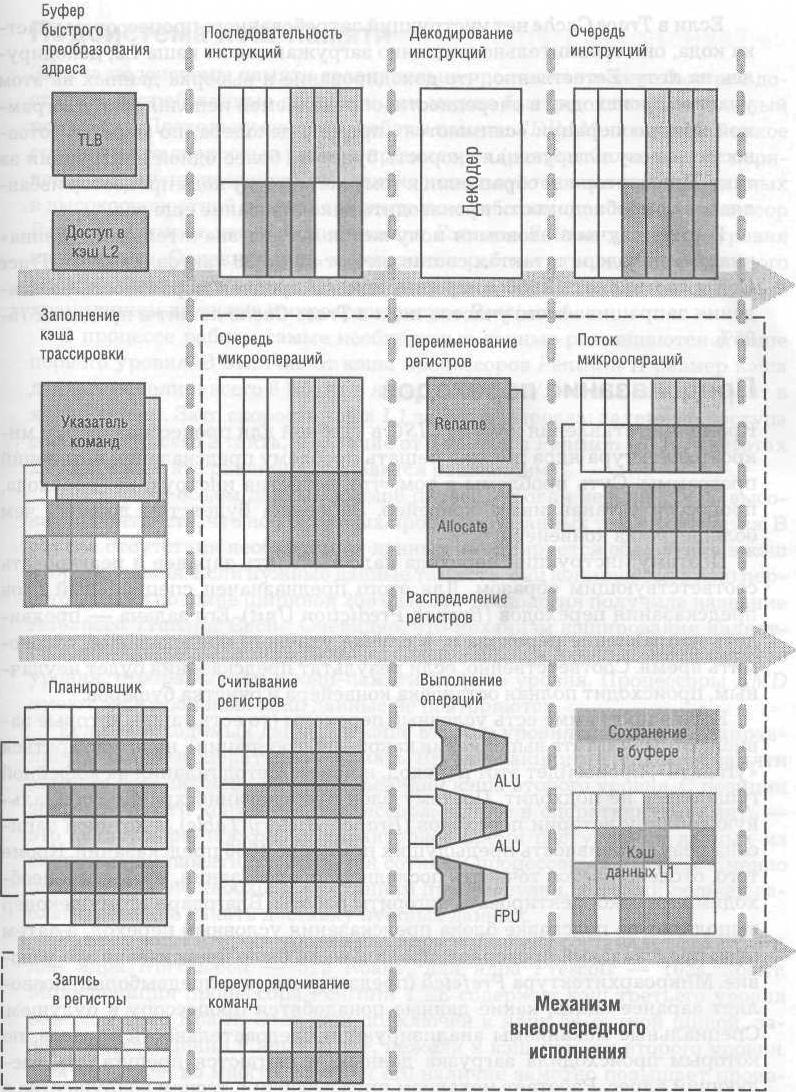

Если команду х86 нельзя представить в виде одной простой инструкции, декодер создает некую последовательность простых инструкций (микроопераций) RISC. В процессоре Pentium 4 вместо традиционного кэша команд, в котором хранится код х86, имеется кэш трассировки (Trace Cache). Он расположен после декодера, но перед остальными блоками процессора. В нем хранятся не инструкции CISC, а результаты их декодирования — микрооперации. При такой архитектуре декодер работает независимо от остальных блоков, наполняя Trace Cache микрооперациями.

Конвейер операций процессора Pentium 4

Если в Trace Cache нет инструкций затребованного процессором участка кода, они сравнительно медленно загружаются из кэша L2, декодируясь на лету. Естественно, что декодирование и выборка данных на этом участке происходят в очередности, определяемой исполняемой программой. Микрооперации «снимаются» прямо с декодера, по мере их готовности, и результирующая скорость будет не более одной инструкции за такт. При повторном обращении к тому же участку кода процессор избавляется от необходимости производить декодирование еще раз.

В ряде случаев экономия получается весьма значительной: «длина» участка декодера в тактах составляет от 10 до 30 тактов. Емкость Trace Cache составляет 12 000 микроопераций. В среднем вероятность нахождения запрашиваемого участка кода в Trace Cache лежит в пределах 75-95%.