Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

Ввод-вывод

Ввод-вывод

Второе. ICW2 — определение базового адреса

- Подробности

- Родительская категория: Ввод-вывод

- Категория: Программирование контроллера прерываний i8259А

Настало время прояснить еще один принципиальный момент, до этого времени сознательно замалчиваемый. Он связан с принципом определения числового диапазона адресов векторов прерываний для аппаратных прерываний, замкнутых на контроллер прерываний. В реальном режиме работы микропроцессора для хранения указателей (векторов) на процедуры-обработчики прерываний используется специальная область памяти — таблица векторов прерываний. Эта таблица начинается с нулевого адреса оперативной памяти и занимает 1 Кбайт. Среди векторов есть, конечно, и вектора, указывающие на процедуры-обработчики тех прерываний, которые замкнуты на контроллер. Эти вектора располагаются в таблице последовательно, одной группой, и их нумерация начинается с некоторого номера вектора, называемого базовым. Приказ ICW2 (табл. 15.2) позволяет задать номер этого базового вектора для контроллера прерываний в соответствии с тем номером, который назначен соответствующему вектору в таблице векторов прерываний. В реальном режиме работы микропроцессора BIOS в процессе начальной загрузки системы инициализируется ведущий контроллер значением 08h, а ведомый — значением 70h. Теперь понятно, почему обработчику прерываний от таймера соответствует номер вектора 08h в таблице векторов прерываний, хотя физически он замкнут на уровень 0 контроллера i8259A. При желании мы вполне можем изменить значение базового номера на любой не используемый в системе номер, к примеру — 90h. Также следует учитывать, что некорректная установка нового номера этим приказом может полностью нарушить работу всей системы.

Данный приказ посылается в порт 21h.

Как видно, для задания номера базового вектора используются биты с 3 по 7 приказа ICW2. Объяснить это можно тем, что на контроллер замыкаются 8 источников прерываний. Выше мы отметили, что номера векторов, соответствующих прерываниям, замкнутых на контроллер, имеют последовательные номера, начиная с базового. Так, для контроллера, инициализированного значением базового номера 08h, номера векторов в таблице векторов прерываний будут 08h, 09h, 0ah, 0bh и т. д. Отсюда и получается, что для задания базового номера биты 0...2 использовать нельзя, так как они применяются для формирования адресов векторов прерываний следующих после базового уровней.

Буферизация содержимого системной шины. Схема декодирования адреса порта

- Подробности

- Родительская категория: Ввод-вывод

- Категория: Шина ISA

Буферизация содержимого системной шины

Необходимость буферизации определяется следующими причинами:

•Защита канала от больших напряжений, замыканий на землю;

•Защита от большой нагрузки при подключении к каналу большого числа потребителей (более 5), которые увеличивают емкостную нагрузку, вследствие чего изменяют временные параметры.

В качестве буфера можно использовать шинные приемо-передатчики, подключенные к соответствующим линиям канала.

В модуле используются следующие микросхемы:

•однонаправленные приемо-передатчики — 74LS245 (КР580 ВА 86),

•двунаправленные приемо-передатчики — 74LS244 (КР580 ИР 82). Последние применены для буферизации шины данных и включаются по сигналу AEN, а направление передачи определяет сигнал IOW.

Схема декодирования адреса порта

Элемент декодирования адреса порта предназначен для определения порта модулем. Номер порта в модуле задан аппаратно, и при совпадении в процессе декодирования этого номера с пришедшим (по шине адреса) модуль откликается на команду ввода-вывода (происходят те или иные действия).

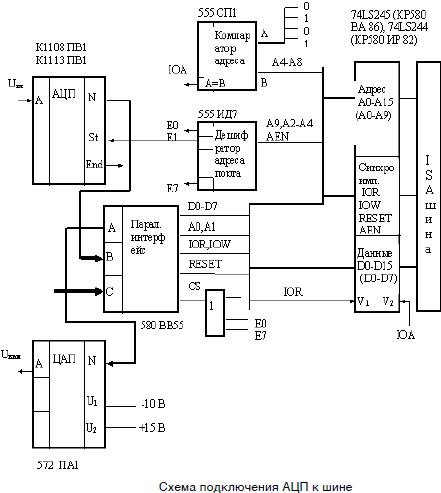

На рисунке ниже (схема подключения АЦП к шине) представлена двухкаскадная схема декодирования адреса. Она включает цифровой компаратор (555 СП1) и дешифратор (555 ИД7). На входе А компаратора жестко задан код 0101, а код адреса дешифратора определяется номером используемого выхода. Разряд А9 включает дешифратор. Младшие разряды А0, А1 задают номер канала параллельного интерфейса.

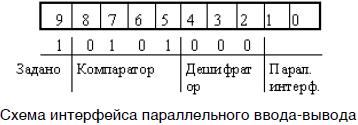

Адрес порта можно определить в соответствии с приведенной ниже схемой (схема интерфейса параллельного ввода-вывода).

Схема предназначена для подключения нескольких источников (приемников) данных к шине, а также для организации двунаправленного и стробируемого ввода-вывода (см. таблица ниже).

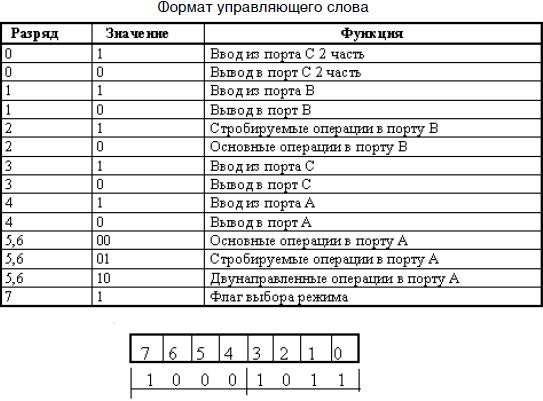

Микросхема параллельного интерфейса поддерживает несколько режимов работы по каждому выходу (А, В, С), выбор режима проводится подачей управляющего слова. Ниже приведен формат управляющего слова ().

Последняя картинка для того, чтобы порт А работал на вывод, а порты В,С — на ввод, необходимо записать управляющее слово.

В результате при работе со схемой (Схема подключения АЦП к шине) необходимо первоначально запрограммировать конфигурацию внутренних портов, а лишь затем считывать из АЦП или выводить в ЦАП информацию. Команды чтения и вывода аналогового сигнала будут иметь вид:

Port [$2A3]:=$8B;

A:=Port[$2A1];

Port [$2A0]:=A;

Время реакции на запрос. Способы задания точек входа

- Подробности

- Родительская категория: Ввод-вывод

- Категория: Прерывания

Время реакции на запрос прерывания

Это время определяется двумя независимыми факторами:

1) Время входа в прерывание для одиночного запроса.

2) Интенсивность потока запросов — при значительном количестве источников и при интенсивном потоке запросов часто оказывается, что очередной запрос приходит еще до того, как обслужен предыдущий. В этом случае среднее время реакции на запрос (время от момента возникновения запроса до начала выполнения первой команды обработчика) может оказаться значительным

Способы задания точек входа в обработчик прерывания

•Короткое прерывание — по прерыванию происходит выход на первую исполняемую команду. Адрес команды может быть фиксирован (TMS 320C10) или задаваться номером прерывания (ADSP 2181).

•Длинное прерывание — выход в обработчик через команду JMP или через вектор прерывания:

•Фиксированное расположение векторов в памяти (каждый вектор определяет адрес обработчика прерываний) (Intel 80x86);

•Программно задаваемое / перемещаемое расположение векторов (MC 68060).

Третье. ICW3 — связь контроллеров

- Подробности

- Родительская категория: Ввод-вывод

- Категория: Программирование контроллера прерываний i8259А

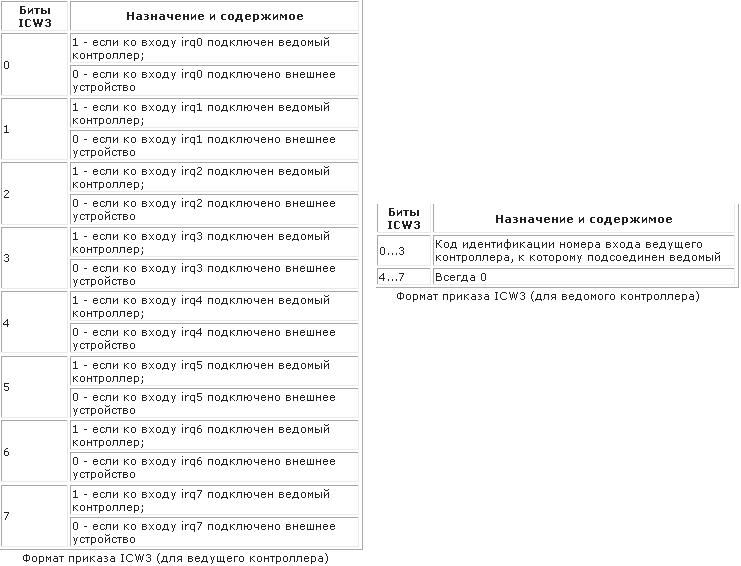

Этот приказ предназначен для связи контроллеров в системе с несколькими контроллерами прерываний.

Вариант работы с одной микросхемой i8259А, позволяющий обрабатывать запросы от 8 источников, использовался в ранних системах на базе микропроцессоров i8088/86 (в архитектуре XT). Но i8259А позволяет организовать так называемое каскадное соединение этих микросхем, при котором выход INT одной микросхемы подается на вход одного из уровней irq другой микросхемы (см. рис. 15.1). Это позволяет организовать обработку запросов от большего числа источников. При этом один контроллер является ведущим, а другой — ведомым (тот, который подключен ко входу irq ведущего). Ниже мы разберемся с каскадированием более подробно. Сейчас отметим, что формат приказа ICW3 зависит от того, какой контроллер инициализируется — ведущий (табл. 15.3) или ведомый (табл. 15.4). При инициализации ведущего контроллера ICW3M сообщает, к каким его входам irq подсоединены ведомые контроллеры. Соответственно, при инициализации ведомого контроллера нужна другая форма этого приказа, которая несет информацию о том, к какому входу ведущего подключен данный ведомый контроллер.

Приказ ICW3 посылается в порт 21h.

Источники прерываний: внешние и внутренние события. Радиальная схема прерывания

- Подробности

- Родительская категория: Ввод-вывод

- Категория: Прерывания

Источники прерываний: внешние и внутренние события

До сих пор речь шла о событиях, внешних по отношению к

вычислительному ядру (процессор + память).

В ходе выполнения программы могут произойти внутренние события, которые заранее трудно предсказуемы, например:

•арифметическое переполнение;

•деление на нуль;

•появление в программе недопустимой команды (из-за ошибки программиста, из-за сбоя, из-за того, что программа разрабатывалась для "старших" моделей семействапроцессоров и использует команды, отсутствующие в младшей модели);

•обращение к несуществующему адресу памяти;

• и многие другие подобные.

Такие внутренние события, делающие нормальное продолжение основного алгоритма невозможным, принято называть прерываниями по внутренним причинам, исключительными ситуациями или исключениями (exceptions).

Почти все их можно выявить, вставляя в программу в подходящих местах соответствующие анализирующие фрагменты, Например, после выполнения действий по модификации адресов проверять результат на нахождение в заданных границах, но это требует затрат дополнительного процессорного времени, иногда весьма значительных, а также дополнительных усилий программиста. Поэтому разработчики процессора могут предусматривать автоматическое выявление подобных ситуаций и генерацию запроса прерывания.

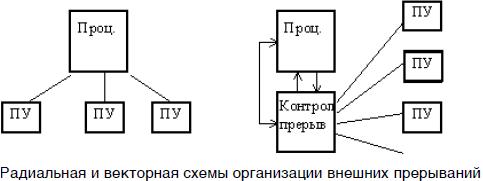

Радиальная схема и управление прерываниями. Контроллер прерываний

Схемы организации прерываний представлены на рисунке (см. рисунок ниже). Для реализации радиальной схемы подключения источников аппаратных запросов надо иметь отдельный вход запроса для каждого источника запроса. Большинство процессоров имеет малое количество входов запроса (1...3). Этого может быть достаточно в очень маленьких системах, однако весьма часто в системе требуется иметь больше входов запроса прерывания, чем имеет процессор. Это позволяет сделать дополнительный узел, называемый программируемым контроллером прерываний (ПКП). Обычно ПКП имеет несколько входов для подключения источников запросов и один выход, подключаемый ко входу запроса прерывания процессора.

ПКП выполняет несколько функций:

1) преобразовывает радиальную схему подключения периферийных устрой в векторную;

2) обеспечивает обмен сигналами с процессором для идентификации источника прерываний;

3) позволяет управлять приоритетами отдельных запросов;

4) дает возможность программно разрешать/запрещать прерывания отдельно для каждого источника, а также выбирать фрагмент входного сигнала, инициирующий запрос (уровень или фронт, активная полярность).

В любой реальной вычислительной системе далеко не все векторы прерываний и даже не все входы запросов аппаратных прерываний бывают использованы. Разработчик программы или программно- аппаратного комплекса может использовать свободные ресурсы системы прерываний ля собственных нужд, например, для обеспечения реакции на события в "своем" (может быть, нестандартном) периферийном устройстве.

Еще статьи...

Подкатегории

-

Прямой доступ к памяти (ПДП)

- Кол-во материалов:

- 2

-

Программирование контроллера прерываний i8259А

- Кол-во материалов:

- 11

-

Прерывания

- Кол-во материалов:

- 9

-

Синхронизация программ с внешними процессами

- Кол-во материалов:

- 2

-

Шина ISA

- Кол-во материалов:

- 4

-

Подключение периферийных устройств к ЭВМ

- Кол-во материалов:

- 3