Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

https://rbzaym.ru где срочно взять деньги.

Память. Нижний уровень

Пакетная передача данных

- Подробности

- Родительская категория: Память. Нижний уровень

- Категория: КЭШ-память

Пакетная передача данных(Burst Mode) предназначена для быстрых операций со строками КЭШа. Строка КЭШа процессора, например, имеет длину 16 байт, следовательно, для ее пересылки требуется четыре 32-разрядных шинных цикла. В этом режиме адрес и сигналы идентификации типа шинного цикла выдаются только в первом такте пакета. В каждом из последующих тактов могут передаваться данные, адрес для которых уже не передается по шине, а вычисляется из первого такта, по правилам, известным и процессору, и внешнему устройству. В пакетный цикл процессор может преобразовать любой внутренний запрос на множественную передачу.

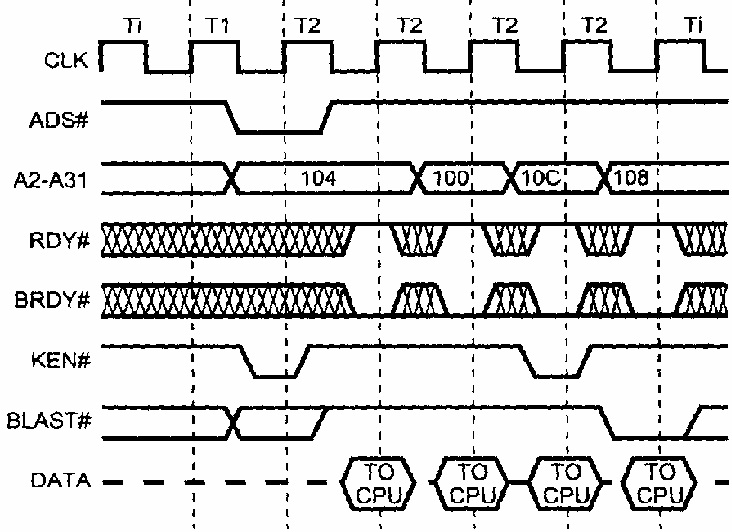

Пакетный цикл (см. рисунок ниже) начинается процессором так же, как и обычный: на внешней шине устанавливается адрес, сигналы идентификации типа цикла и формируется строб ADS#. В следующем такте передается первая порция данных, и, если она не единственная, сигнал BLAST# имеет пассивное значение. Если адресованное устройство поддерживает пакетный режим, оно должно ответить сигналом BRDY# вместо сигнала RDY# по готовности данных в первой же передаче данных цикла. В этом случае процессор продолжит цикл как пакетный, не вводя такта адресации-идентификации (с сигналом ADS#), а сразу перейдет к передаче следующей порции данных.

Нормально о завершении пакетного цикла процессор сообщает устройству сигналом BLAST#, который выдается в такте последней передачи пакета. Если у процессора есть намерения собрать пакет, а устройство отвечает сигналом RDY#, данные будут передаваться обычными циклами. Введением сигнала RDY# вместо BRDY# внешнее устройство может в любой момент прервать пакетную передачу, и процессор ее продолжит обычными циклами. В идеальном варианте (без тактов ожидания) для передачи 16 байт в пакетном режиме требуется всего 5 тактов шины вместо восьми, которые потребовались бы при обычном режиме обмена

Временная диаграмма пакетного режима загрузки КЭШ- памяти

Пакетная передача данных предполагает соблюдение одних и тех же правил формирования последующих адресов как процессором, так и внешним устройством (памятью). Во время пакетного цикла процессора старшие биты адреса А[Зl:4] остаются неизменными (как и сигналы идентификации M/IO#, D/C#, W/R#. Изменяться могут только биты А[З:2] и сигналы ВЕ[З:О] (у процессоров с 64-битной шиной данных неизменны А[Зl:5], меняются только А[4:З] и ВЕ[7:0]). Таким образом, один пакетный цикл не может пересекать границу строки КЭШа. Кроме того, имеется специфический порядок следования адресов в пакетном цикле, который определяется начальным адресом пакета (задается процессором) и разрядностью передачи (задается устройством сигналами ВS1б# и ВS8#).