Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

USB

Структуры данных и регистры EHC

Контроллер EHC имеет несколько наборов регистров:

- конфигурационные регистры PCI — стандартный заголовок и специфические регистры. В заголовке для EHC указывается код класса 0Ch, подкласс 03h, интерфейс 20h;

- регистры описания структуры контроллера, отображенные на память; на их положение указывает BAR в заголовке конфигурационного пространства;

- операционные регистры EHC (32-битные), отображенные на память; они расположены вслед за предыдущим набором.

Таблица. Специфические регистры конфигурационного пространства EHC

| Смещение (длина) | Назначение |

| 60h (8 бит) | SBRN (Serial Bus Release Number) — версия шины USB (20h) |

| 61h (8 бит) | FLADJ (Frame Length Adjustment Register) — регистр подстройки длительности кадра, используются биты [5:0]. Длительность кадра в битовых интервалах HS определяется по формуле 59488+16× FLADJ, по умолчанию FLADJ=20h (60 000 bt) |

| 62-63h (16 бит) | PORTWAKECAP, регистр возможности генерации событий пробуждения для портов корневого хаба. Бит 0 — признак наличия данного регистра (0 — нет регистра), биты [15:1] — маски для портов с теми же номерами. На работу EHC регистр не влияет (это только информация для драйвера) |

| EECP+0h (32 бита) | USBLEGSUP (USB Legacy Support), регистр возможностей поддержки эмуляции старых устройств, адрес определяется в поле EECP регистра HCCPARAMS, отображенного на память. Назначение бит: Биты 31:25 — резерв Бит 24 — HC OS Owned Semaphore, семафор запроса управления контроллером. ОС устанавливает в «1» как запрос, право считается предоставленным, когда BIOS установит в «0» бит 16; Биты [23:17] — резерв; Бит 16 — HC BIOS Owned Semaphore, семафор права управления контроллером. BIOS устанавливает в «1» как признак владения контроллером; Бит [15:8] — Next EHCI Extended Capability Pointer, указатель на следующий идентификатор расширенных возможностей; [7:0] Capability ID, идентификатор поддержки старых устройств (01h) |

| EECP+4h (32 бита) |

USBLEGCTLSTS (USB Legacy Support Control and Status), регистр управления и состояния эмуляции. BIOS использует этот регистр для разрешения SMI по различным событиям и идентификации событий. Назначение бит: Бит 31 — SMI on BAR, прерывание SMI по смене базового адреса регистров EHC Бит 30 — SMI on PCI Command, прерывание SMI по записи в регистр команд конфигурационного пространства устройства PCI |

Таблица. Регистры описания структуры контроллера EHC

| Смещение (длина) | Назначение |

| 00h (8 бит) | CAPLENGTH, длина набора регистров описания (определяет положение операционных регистров) |

| 01h (8 бит) | Резерв |

| 02h (16 бит) | HCIVERSION, номер версии интерфейса хост-контроллера (0100h) |

| 04h (32 бита) |

HCSPARAMS, параметры структуры: Бит 16 — P_INDICATOR, признак поддержки управления индикаторами портов |

| 08h (32 бита) | HCCPARAMS, параметры свойств: Биты [31:16] — резерв. Биты [15:8] — EECP (EHCI Extended Capabilities Pointer), указатель на положение регистра USBLEGSUP в конфигурационном пространстве Биты [7:4] — Isochronous Scheduling Threshold, порог планирования изохронных передач. Если бит 7=0, то биты [6:4] определяют минимальную дистанцию (число микрокадров) от текущей позиции, на которой драйвер может менять дескрипторы изохронных передач. Единичное значение бита 7 означает, что контроллер способен удержать в своем кэше дескрипторы для целого кадра Бит 3 — резерв Бит 2 — Asynchronous Schedule Park Capability, поддержка режима парковки для заголовков HS-очередей асинхронного плана Бит 1 — Programmable Frame List Flag, признак поддержки программируемого размера списка кадров (0 — размер только 1024 элемента) Бит 0 — 64-bit Addressing Capability, способность использования 64-битной адресации памяти |

| 0Ch (64 бита) | HCSP-PORTROUTE, описание распределения портов по контроллерам-компаньонам, массив 4-байтных номеров контроллера-компаньона для каждого нисходящего порта корневого хаба. Вмещает описания для 15 портов (биты [3:0], формально относящиеся к нулевому порту, не используются) |

Таблица. Операционные регистры контроллера EHC

| Смещение (длина) | Назначение |

| 00h |

USBCMD, регистр команд USB Биты 9:8 — Asynchronous Schedule Park Mode Count, число успешных транзакций из HS-очереди, которые контроллер может выполнять до продолжения прохода по асинхронному плану |

| 04h | USBSTS, регистр состояния USB Биты [31:16] — резерв Бит 15 — Asynchronous Schedule Status, реальное текущее состояние разрешения асинхронного плана (может отставать от команды смены) Бит 14 — Periodic Schedule Status, реальное текущее состояние разрешения периодического плана (может отставать от команды смены) Бит 13 — Reclamation, признак не пустого асинхронного плана. Обнуляется, когда контроллер встречает заголовок очереди с установленным флагом H, устанавливается в «1» при исполнении любой транзакции асинхронного плана. Если при обнуленном бите Reclamation контроллер встречает заголовок очереди с флагом H, он останавливает обход асинхронного плана Бит 12 — HCHalted, состояния останова контроллера Биты [11:6] — резерв Бит 5 — Interrupt on Async Advance, признак прерывания по продвижению асинхронного плана Бит 4 — Host System Error, признак системной ошибки контроллера (как устройства PCI) Бит 3 — Frame List Rollover, признак оборота по списку кадров Бит 2 — Port Change Detect, обнаружена смена состояния порта Бит 1 — USBERRINT (USB Error Interrupt), признак завершения транзакции по ошибке USB Бит 0 —USBINT (USB Interrupt), признак завершения транзакции, для которой предписана генерация прерывания |

| 08h |

USBINTR, регистр разрешения прерываний USB: Бит 2 — Port Change Interrupt Enable, разрешение прерывания по смене состояния порта |

| 0Ch | FRINDEX, индекс кадра. Инкрементируется с каждым микрокадром, биты [N:3] используются как текущий индекс в списке кадров |

| 10h | CTRLDSSEGMENT, старшие биты 64-битного адреса (адрес 4G-сегмента, содержащего все структуры данных и регистры EHC) |

| 14h | PERIODICLISTBASE, базовый адрес списка кадров (биты [11:0] нулевые — список должен быть выровнен по границе станицы 4 Кб) |

| 18h | ASYNCLISTADDR, очередной адрес асинхронного списка, указывает на следующий заголовок очереди в асинхронном плане (биты [4:0] — резерв) |

| 1C-3Fh | Резерв |

| 40h | CONFIGFLAG, флаг конфигурирования: бит 0 устанавливается в 1, когда ПО завершает конфигурирование EHC (по этому флагу включается управление маршрутизацией портов от EHC, при нулевом значении порты безусловно подключены к своим контроллерам-компаньонам). Биты [31:1] не используются |

| 44h… …40h+4×n |

PORTSC(n), управление и состояние n-го порта корневого хаба: Биты [31:23] — резерв |

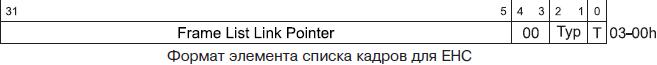

Формат элемента списка кадров (Frame List Element Pointer) приведен на рисунке ниже.Здесь Frame List Link Pointer — указатель на дескриптор изохронной передачи или заголовок очереди (для прерываний); если бит T = 1 (Terminate), то указатель не используется. Поле Typ описывает тип структуры, на которую ссылается указатель: 00 — iTD, 01 — QH, 10 — siTD, 11 — FSTN.

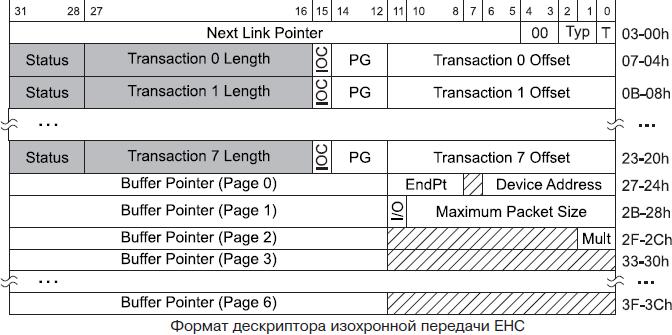

Дескриптор изохронной передачи iTD (Isochronous Transfer Descriptor) относится к точкам HS-устройств, его формат приведен на рисунке ниже. Первое двойное слово по формату совпадает с элементом списка кадров. Далее следует 8-элементный список дескрипторов транзакций, выполняемых в каждом из восьми микрокадров (серым цветом выделены поля, модифицируемые хост-контроллером). В следующих семи двойных словах содержатся адреса физических страниц, в которых может располагаться буфер для транзакций, и описание конечной точки. В этом описании:

- поле Status отражает состояние выполнения транзакции:

- бит 31 — Active, активность, устанавливается драйвером как признак необходимости исполнения, сбрасывается контроллером по исполнении транзакции;

- бит 30 — Data Buffer Error, ошибка буфера данных (несвоевременность доставки данных в/из памяти);

- бит 29 — Babble Detected, «болтливость», обнаруженная при исполнении транзакции;

- бит 28 — Transaction Error (XactErr), ошибка USB при выполнении транзакции (только для транзакций IN).

- поле Transaction X Length задает число переданных байтов (0–3072). Для транзакций IN драйвер устанавливает ожидаемое число, контроллер его меняет на реальное число принятых байтов;

- бит IOC (Interrupt On Complete) заказывает прерывание по исполнению;

- поле PG (Page Select) задает номер страницы буфера (0–6), из которого берутся старшие (31:12) биты адреса для формирования стартового адреса буфера данной транзакции;

- поле Transaction X Offset задает смещение начала буфера X-транзакции относительно выбранной страницы;

- поля Buffer Pointer (Page n) задают физические адреса страниц 0–7;

- поле EndPt задает номер конечной точки;

- поле I/O задает направление: 0 — OUT, 1 — IN;

- поле Device Address задает адрес устройства;

- поле Maximum Packet Size — максимальный размер пакета для точки (1–1024), в транзакции IN используется как порог для определения «болтливости» устройства;

- поле Mult задает число транзакций за один микрокадр (00 — резерв).

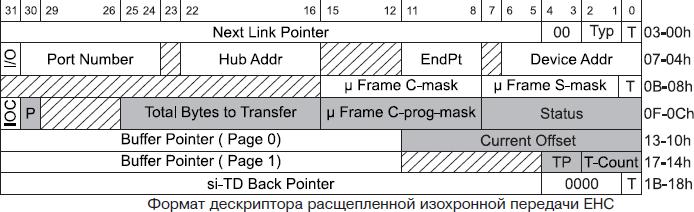

Дескриптор расщепленной изохронной транзакции siTD (Split-transaction Isochronous Transfer Descriptor) относится к точкам FS-устройств, его формат приведен на следующем рисунке. Первое двойное слово по формату совпадает с элементом списка кадров. Поля I/O, EndPt, Device Address описывают координаты и направление конечной точки.

Поля Hub Addr и Port Number задают адрес расщепляющего транзакцию хаба и номер порта.

Битовые поля μFrame S-mask и μFrame C-mask задают маски для микрокадров, в которых планируются транзакции SS и CS (транзакция в микрокадре выполняется при единичном значении маски). В поле μFrame C-prog-mask контроллер отмечает кадры, в которых произошли транзакции завершения.

Адрес буфера для начала транзакции задается полями Buffer Pointer (Page 0) и Current offset, при переходе на другую физическую станицу в качестве ее адреса используется поле Buffer Pointer (Page 1). Бит P определяет номер используемой страницы. Ожидаемый размер пакета задается в поле Total Bytes to Transfer, контроллер этот размер заменит реальным. Бит IOC (Interrupt On Complete) заказывает прерывание по исполнении.

Поле TP (Transaction Position) — позиция текущей HS-транзакции: 00 — All, HSтранзакция содержит все данные FS-транзакции (не более 188 байт), 01 — Begin, первый пакет для FS-транзакции, 10 —Mid, промежуточный, 11 — End, последний HS-пакет для FS-транзакции.

Поле T-Count (Transaction Count), число HS-транзакций, необходимых для выполнения FS-транзакции (1–6).

Состояние выполнения транзакции определяется полем Status:

- бит 7 — Active, активность, устанавливается драйвером как признак необходимости исполнения, сбрасывается контроллером по исполнении или по ошибке;

- бит 6 — ERR, признак получения одноименного ответа от транслятора транзакций;

- бит 5 — Data Buffer Error, ошибка буфера данных (несвоевременность доставки данных в/из памяти);

- бит 4 — Babble Detected, «болтливость», обнаруженная при исполнении транзакции;

- бит 3 — Transaction Error (XactErr), ошибка USB при выполнении транзакции (только для транзакций IN);

- бит 2 — Missed Micro-Frame, пропуск микрокадра (по вине контроллера), в котором должно было быть завершение;

- бит 1 — SplitXstate (Split Transaction State), состояние (фаза) расщепленной транзакции: 0 — SS, 1 — CS;

- бит 0 — резерв.

Поле si-TD Back Pointer является обратным указателем на декриптор si-TD (если в том же двойном слове бит T = 1, указатель не используется).

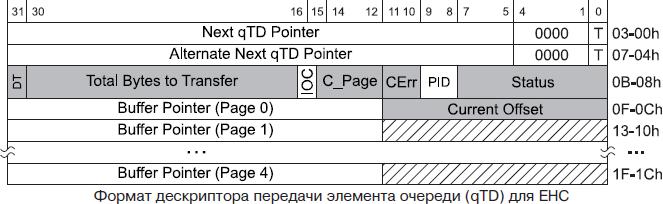

Дескриптор передачи — элемент очереди qTD (Queue Element Transfer Descriptor) имеет формат, приведенный на следующем рисунке. Поле Next qTD Pointer указывает на следующий qTD (если T = 0), к которому следует перейти после нормальной отработки передачи. Поле Alternate Next qTD Pointer позволяет указать на qTD, к которому следует перейти в случае приема короткого пакета. Ожидаемая длина передачи задается полем Total Bytes to Transfer, по окончании в этом поле окажется реальная длина. Адрес буфера для начала транзакции задается полями Buffer Pointer (Page 0) и Current offset, по мере продвижения контроллер меняет значение поля C_Page, определяющего номер физической страницы. Бит IOC задает прерывание по выполнению. Поле PID задает тип маркера в транзакциях: 00 — OUT, 01 — IN, 10 — SETUP, 11 — резерв. Бит DT — текущее значение Data Toggle для данной передачи, В поле CErr драйвер заносит допустимое число повторов (из-за ошибок) в каждой транзакции данной передачи (0 — число повторов неограниченно). Поле Status отражает состояние текущей транзакции передачи:

- бит 7 — Active, активность, устанавливается драйвером как признак необходимости исполнения, сбрасывается контроллером по исполнении или по достижении лимита повторов;

- бит 6 — Halted — признак получения ответа STALLl;

- бит 5 — Data Buffer Error, ошибка буфера данных (несвоевременность доставки данных в/из памяти);

- бит 4 — Babble Detected, «болтливость», обнаруженная при исполнении транзакции;

- бит 3 — Transaction Error (XactErr), ошибка USB при выполнении транзакции (только для транзакций IN);

- бит 2 — Missed Micro-Frame, пропуск микрокадра (по вине контроллера), в котором должно было быть завершение (только для FS- и LS-точек);

- бит 1 — SplitXstate (Split Transaction State), состояние (фаза) расщепленной транзакции (только для FS- и LS-точек): 0 — SS, 1 — CS;

- бит 0 — P/ERR, для HS-точек при PID Code = 00 (OUT) — состояние протокола Ping (Ping State): 0 — выполнять транзакцию OUT, 1 — PING. Для не-HS точек — ERR, признак получения подтверждения ERR на расщепленную периодическую транзакцию.

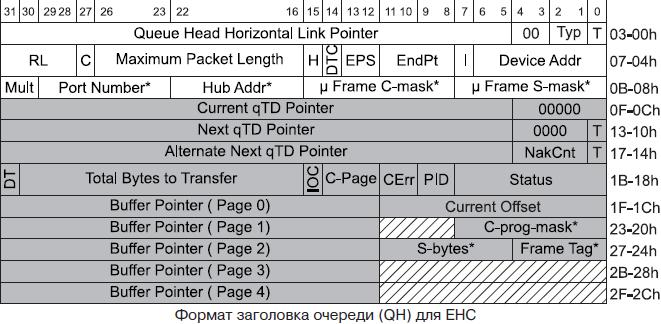

Заголовок очереди QH имеет формат, приведенный на рисунке ниже. Здесь Queue Head Horizontal Link Pointer указывает на следующую структуру по горизонтали, которая может быть заголовком очереди или любым дескриптором изохронной передачи. В последующих двух двойных словах описывается конечная точка, а для точек LS/FS еще и дополнительные параметры, требуемые для расщепления транзакций. Поля Device Address, EndPt и Maximum Packet Length задают адрес устройства, номер точки и максимальный размер пакета. Поле EPS задает скорость: 00 — LS, 01 — FS, 10 — HS, 11 — резерв. Бит H (Head of Reclamation List Flag) — флаг, которым драйвер помечает один из заголовков очередей из асинхронного плана для определения опустошения всех очередей этого плана (этот флаг вызывает обнуление бита Reclamation в регистре состояния контроллера). Бит DTC управляет переключателем Toggle Bit: 0 — использовать бит DT из данного заголовка очереди QH, 1 — из qTD. Флаг C — признак управляющей точки HS-устройства. Флаг I (Inactivate on Next Transaction) — программный запрос контроллеру обнулить бит активности при следующей транзакции. Используется только в заголовке очереди периодических транзакций FS/LS-устройств для обеспечения возможности программной коррекции значений полей S-mask и C-mask в данном заголовке. Поле RL (Nak Count Reload) задает значение счетчика ответов NAK, загружаемое в поле Nak Cnt. Поле Mult задает число транзакций в микрокадре для широкополосных точек (0 — резерв). Поля Port Number, Hub Addr, μFrame S-mask и μFrame C-mask требуются для точек FS/LS-устройств, по назначению они совпадает с одноименными полями siTD.

Поле Current qTD Pointer содержит адрес текущего обрабатываемого qTD, последующие 8 двойных слов являются оверлейной областью передачи (Transfer Overlay), в которую контроллер загружает требуемые параметры для обрабатываемого элемента. Большинство полей по назначению (и положению) совпадает с одноименными полями qTD, здесь перечислим только особые. Поле NakCnt (Nak Counter) — счетчик ответов NAK или NYET. В поле C-prog-mask контроллер отмечает микрокадры, в которых происходили транзакции завершения расщепленных транзакций. В поле FrameTag контроллер записывает тег кадра, в котором производится расщепленная транзакция прерывания. В поле S-bytes контроллер указывает число байтов, переданных в расщепленных транзакциях IN и OUT.

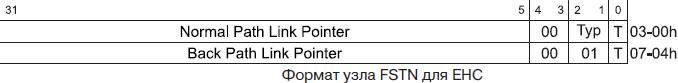

Формат узла FSTN (Periodic Frame Span Traversal Node) приведен на последнем рисунке. Здесь Normal Path Link Pointer может указывать на любую структуру данных, а обратный указатель Back Path Link Pointer может указывать только на заголовок очереди.