Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

Вакуумная формовочная машина korst58.ru.

USB

Структуры данных и регистры контроллера UHC

Драйвер в системной памяти создает список кадров Frame List, состоящий из 1024 элементов. Каждый элемент этого списка содержит 32-битный указатель на связанный список структур данных, по которым контроллер выполняет транзакции в данном кадре. Хост-контроллер имеет регистр базового адреса списка кадров, указывающий на начало списка. Текущий номер отрабатываемого элемента определяется десятью младшими битами счетчика кадров, находящегося в контроллере и инкрементируемого каждую миллисекунду. Период счета кадров можно немного варьировать, изменяя константу, занесенную в регистр модификации длительности кадра (SOF Modify Register), что обеспечивает возможность подстройки частоты кадров для синхронизации изохронных обменов.

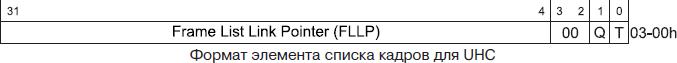

Элемент списка кадров может указывать либо на дескриптор изохронной передачи TD (Transfer Descriptor), либо (если в данном кадре изохронный обмен не планируется) на заголовок очереди QH (Queue Head). Если в данном кадре вообще не планируются передачи, то в элементе устанавливается признак-«заглушка» T (Terminate, конец связанного списка, в данном случае — пустого). Еще раз напомним, что здесь слово «передача» (Transfer, согласно спецификации UHCI) употребляется в узком смысле — она соответствует одной транзакции (передаче не более одного пакета данных). Элемент (32-битное слово) имеет формат, приведенный на рисунке ниже. Поле FLLP (Frame List Link Pointer) — указатель на элемент; бит T — признак последнего элемента (при T = 1 указатель FLLP недействителен). Бит Q задает класс связанного элемента, на который указывает FLLP (0 — TD, 1 — QH).

Для каждого кадра из списка устанавливается своя цепочка дескрипторов изохронных передач (возможно и пустая), последний из этой цепочки должен ссылаться на цепочку заголовков очередей. Цепочки заголовков QH могут быть общими для группы кадров или даже для всех кадров списка. Общая идея построения очередей состоит в том, чтобы создавать свою очередь для каждого установленного канала (для всех сконфигурированных точек, кроме изохронных). «Дежурный» метод обслуживания — по горизонтали, тогда после выполнения транзакции с одной точкой контроллер перейдет к другой точке (другой очереди). Связывание TD и QH через указатели позволяет формировать произвольные конфигурации переходов от одной очереди к другой и даже делать петли — в последнем случае возможно, что с одной точкой в кадре успеют пройти несколько транзакций. Однако это нетипичный способ планирования. Если очередей много (установлено много каналов), то они распределяются по кадрам (из 1024-элементного списка) так, чтобы цепочка каждого кадра обязательно прошла по горизонтали до конца. Это можно спланировать, поскольку максимальное время для отработки одного элемента каждой очереди (как и изохронных транзакций) заранее известно (оно определяется типом передачи, максимальным размером пакета и скоростью устройства, что известно системе USB). При необходимости «горизонтальную справедливость» можно нарушить, задав вертикальный порядок обслуживания, — контроллер, успешно обработав из очереди передачу с признаком V = 1, перейдет к следующему дескриптору из этой же очереди, а не к следующей очереди.

Дескрипторы передач и заголовки очередей размещаются драйвером в ОЗУ по адресам, выровненным по границе параграфа, поскольку в качестве указателей используются лишь старшие 28 бит (биты [3:0] используются для служебных признаков).

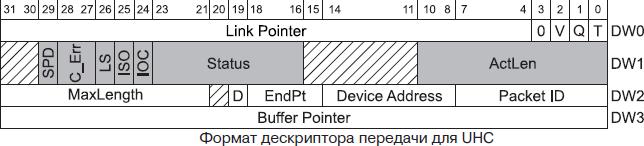

Дескриптор передачи (TD) состоит из 32 байтов, из которых хост-контроллер использует только первые четыре 32-битных слова DW0–DW3. Слова DW4–DW7 зарезервированы для использования драйвером UHC (для организации «сборки мусора» — повторного использования отработанных областей). Формат дескриптора передачи приведен на рисунке ниже. Серым цветом выделены поля, модифицируемые хост-контроллером.

В слове DW0 поле Link Pointer аналогично полю FLLP, а биты T и Q аналогичны одноименным битам элемента списка кадров. Бит V — метод обслуживания TD (1 — в глубину, 0 — в ширину).

Слово DW1 используется для управления и определения состояния выполнения передачи, модифицируется хост-контроллером. Поле ActLen — действительная длина переданных данных; поле Status — состояние выполнения передачи:

длина переданных данных; поле Status — состояние выполнения передачи:

- бит 23: Active — «надо исполнять», устанавливается драйвером, сбрасывается контроллером по успешному исполнению или исчерпанию лимита повторов;

- бит 22: Stalled — точка ответила пакетом STALL;

- бит 21: Data Buffer Error — ошибка буфера данных (переполнение или переопустошение FIFO при выполнении транзакции), транзакция остается активной (при переопустрошении контроллер генерирует пакет с ошибочным CRC, при переполнении не отвечает подтверждением);

- бит 20: Babble — при выполнении данной транзакции обнаружена «болтливость» устройства (оно отключается и устанавливается бит Stalled);

- бит 19: NAK — получение соответствующего ответа (в транзакции SETUP получение NAK устанавливает и признак ошибки тайм-аута);

- бит 18: CRC/Time Out Error — обнаружена ошибка передачи (CRC или таймаут);

- бит 17: Bitstuff Error — обнаружена ошибка вставки бит.

Биты [24:31] используются для управления передачей. Бит IOC заказывает прерывание по исполнению (прерывание генерируется в конце кадра, даже если транзакция уже неактивна, выборка ее дескриптора вызовет прерывание). Бит ISO — признак изохронной передачи (указание не делать повторных попыток). Бит LS — признак LS-устройства, использовать преамбулу перед передачей. Поле C_ERR — счетчик повторных попыток, декрементируемый по каждой ошибке. Переход в 1 или 0 вызывает перевод дескриптора в неактивное состояние. Если драйвер устанавливает нулевое значение, то число повторов неограниченно. Бит SPD — детектор короткого пакета: если в транзакции IN, стоящей в очереди, успешно принято меньше данных, чем ожидалось, то в конце кадра вырабатывается условие прерывания.

В слове DW2 содержится информация для выполнения транзакции: Packet ID — тип используемого маркера IN (69h), OUT (E1h) или SETUP (2Dh); Device Address— адрес устройства USB; EndPt — номер и направление конечной точки. Бит D (Data Toggle) — состояние переключателя для передаваемого или посылаемого пакета. Поле MaxLength — длина передаваемых данных (максимальная длина принимаемых), 000 — 1 байт, 001 — 2, 3FF — 1024; 7FFh — 0 (пустой пакет). Допустимые значения до 4FFh — 1280 байт, теоретический предел емкости кадра. Значения 500–7FEh недопустимы, вызывают фатальную ошибку контроллера.

В слове DW3 содержится Buffer Pointer — указатель на буфер в ОЗУ, используемый для данных этой передачи.

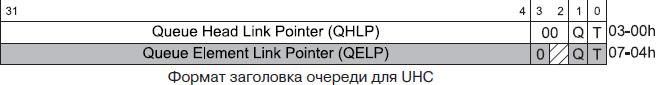

Заголовок очереди (QH) связывает очереди друг с другом (по горизонтали) и ссылается на первый элемент (TD) данной очереди. Хост-контроллер использует два 32-битных слова (см. следующий рисунок). В поле QHLP (Queue Head Link Pointer) содержится указатель на следующий заголовок очереди (горизонтальная связка). В поле QELP (Queue Element Link Pointer) содержится указатель на элемент очереди (вертикальная связка). Признаки последнего элемента (T) и класс связанного элемента (Q) аналогичны одноименным признакам и классам в вышеприведенных структурах.

Дескриптор заголовка очереди создается драйвером; хост-контроллер модифицирует в памяти указатель QELP: успешно отработав транзакцию, контроллер берет из DW0 ее дескриптора указатель на следующий элемент и помещает его на место QELP в заголовке очереди. Таким образом, успешно отработанный TD удаляется из очереди. Когда удаляется последний TD, в QELP устанавливается признак пустой очереди (T). В случае неисправимой ошибки при отработке какого-то дескриптора в QELP также устанавливается «заглушка» T — поток с гарантированной доставкой не позволяет пропустить какую-либо транзакцию. Поле QELP может ссылаться как на TD (тривиальный вариант планирования), так и на QH — очередь сама может содержать очереди.

Регистровая модель UHC поясняется в таблице ниже, где представлены регистры, отображенные на пространство ввода/вывода. Кроме того, как всякое устройство PCI, контроллер UHC имеет регистры в конфигурационном пространстве, в которых, в частности, задаются коды класса (0Ch — контроллер последовательной шины), подкласса (03 — USB) и программного интерфейса (00) в классификации PCI SIG.

Таблица. Регистры контроллера UHC

| Адрес | Назначение |

| Base + (00–01h) |

USBCMD — регистр команд USB Биты 15:8 — резерв Бит 6: CF (Configure Flag) — флаг, которым драйвер отмечает окончание процесса |

| Base + (02–03h) |

USBSTS — регистр состояния USB Биты [15:6] — резерв |

| Base + (04–05h) |

USBINTR — регистр разрешения прерываний Биты [15:4] — резерв |

| Base + (06–07h) | FRNUM — регистр номера кадра |

| Base + (08–0Bh) | FRBASEADD — регистр базового адреса списка кадров |

| Base + 0Ch |

SOFMOD — регистр управления частотой кадров Биты [6:0] — управление длительностью кадра: 0 — 11936 бит, 1 — 11937 бит, … |

| Base + (10–11h) |

PORTSC1 — регистр управления и состояния порта 1 Биты [15:13] — резерв (0) Бит 8: (RO) Low Speed Device Attached — признак подключения LS-устройства |

| Base + (12–13h) | PORTSC2 — регистр управления и состояния порта 2 (аналогично предыдущему) |