Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

Системные платы

Наборы микросхем системной логики

Архитектура ‘‘северный/южный мост’’

- Подробности

- Родительская категория: Системные платы

- Категория: Наборы микросхем системной логики

Большинство ранних версий наборов микросхем Intel (и практически все наборы микросхем других производителей) созданы на основе многоуровневой архитектуры и содержат следующие компоненты: северный мост, южный мост и микросхему Super I/O.

- Северный мост. Представляет собой соединение быстродействующей шины процессора (400/266/200/133/100/66 МГц) с более медленными шинами AGP (533/266/ 133/66 МГц) и PCI (33 МГц). Обозначение микросхемы северного моста зачастую дает название всему набору микросхем; например, в наборе микросхем 440BX номер микросхемы северного моста — 82443BX.

- Южный мост. Является мостом между шиной PCI (66/33 МГц) и более медленной шиной ISA (8 МГц).

- Super I/O. Отдельная микросхема, подсоединенная к шине ISA, которая фактически не является частью набора микросхем и зачастую поставляется сторонними производителями, например National Semiconductor и Standard Microsystems Corp. (SMSC). Микросхема Super I/O содержит обычно используемые периферийные элементы, объединенные в одну микросхему. Следует отметить, что впоследствии микросхемы южного моста включили в себя функциональность Super I/O, так что в современных материнских платах отдельная микросхема Super I/O отсутствует.

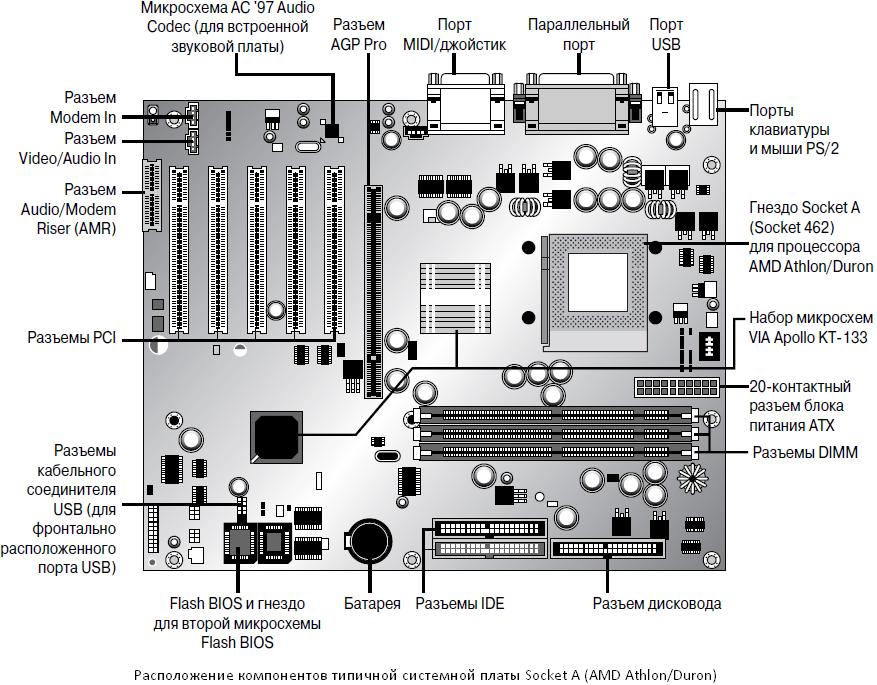

Расположение всех микросхем и компонентов типичной системной платы AMD Socket A, использующей архитектуру “северный/южный мост”, показано на рис. 4.30. Северный мост иногда называют контроллером PAC (PCI/AGP Controller). В сущности, он является основным компонентом системной платы и единственной, за исключением процессора, схемой, работающей на полной частоте системной платы (шины процессора). В современных наборах микросхем используется однокристальная микросхема северного моста; в более ранних версиях содержалось до трех отдельных микросхем, составляющих полную схему северного моста.

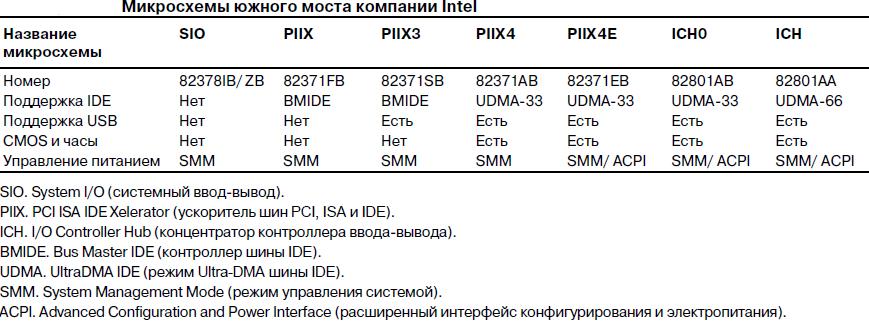

Южный мост обладает более низким быстродействием и всегда находится на отдельной микросхеме. Одна и та же микросхема южного моста может использоваться в различных наборах микросхем системной логики. (Разные типы схем северного моста, как правило, разрабатываются с учетом того, чтобы можно было использовать один и тот же компонент южного моста.) Благодаря модульной конструкции набора микросхем системной логики стало возможным снизить стоимость и расширить поле деятельности для изготовителей системных плат. Южный мост подключается к шине PCI (33 МГц) и содержит интерфейс шины ISA (8 МГц). Кроме того, обычно он содержит две схемы, реализующие интерфейс контроллера жесткого диска IDE и интерфейс USB (Universal Serial Bus — универсальная последовательная шина), а также схемы, реализующие функции памяти CMOS и часов. В старых конструкциях южный мост содержал также все компоненты, необходимые для шины ISA, включая контроллер прямого доступа к памяти и контроллер прерываний.

Микросхема Super I/O, которая является третьим компонентом системной платы, соединена с шиной ISA (8 МГц) и содержит все стандартные периферийные устройства, встроенные в системную плату. Например, большинство микросхем Super I/O поддерживают параллельный порт, два последовательных порта, контроллер гибких дисков, интерфейс “клавиатура/мышь”. К числу дополнительных компонентов могут быть отнесены CMOS RAM/Clock, контроллеры IDE, а также интерфейс игрового порта. Системы, содержащие порты IEEE-1394 и SCSI, используют для портов этого типа отдельные микросхемы.

В новых системных платах с микросхемами северного и южного мостов представлена микросхема Super-South Bridge, которая включает в себя функциональные возможности сразу двух микросхем — собственно южного моста и Super I/O.

Hub-архитектура

- Подробности

- Родительская категория: Системные платы

- Категория: Наборы микросхем системной логики

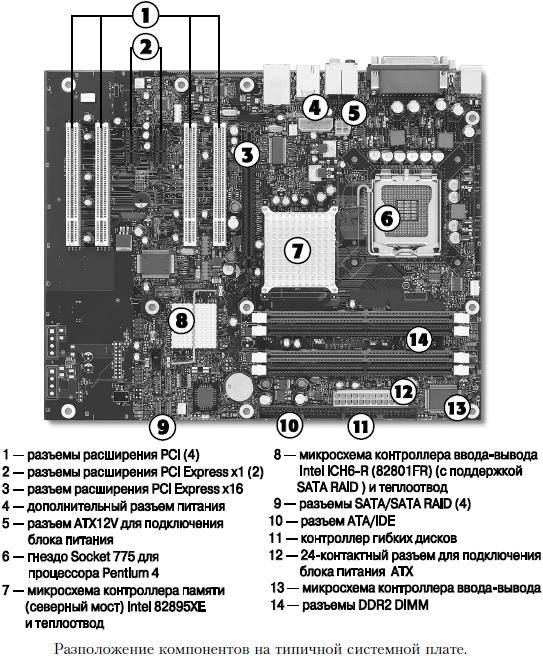

Новые наборы микросхем системной логики от Intel используют архитектуру концентратора (hub-архитектуру), в которой бывший северный мост называется концентратором контроллера памяти (Memory Controller Hub — MCH), а южный — концентратором контроллера ввода-вывода (I/O Controller Hub — ICH). Системы с интегрированной графикой вместо стандартного MCH используют концентратор контроллера графической памяти (Graphics Memory Controller Hub — GMCH).

Вместо соединения этих контроллеров через шину PCI, как в стандартной архитектуре “северный/южный мост”, взаимодействие между ними осуществляется через выделенный интерфейс концентратора, быстродействие которого вдвое выше, чем быстродействие PCI. Hub-архитектура обладает определенными преимуществами по сравнению с традиционной архитектурой “северный/южный мост”.

- Увеличенная пропускная способность. Пропускная способность интерфейса AHA (Accelerated Hub Architecture), используемой в наборах микросхем 8xx, вдвое выше пропускной способности PCI. В наборах микросхем серий 3xx и 9xx используется еще более ускоренная архитектура DMI (Direct Media Interface), которая быстрее PCI в 7,5–14 раз.

- Уменьшенная загрузка PCI. Hub-интерфейс не зависит от PCI и не участвует в перераспределении полосы пропускания шины PCI или Super I/O. Это повышает эффективность остальных устройств, подсоединенных к шине PCI, при выполнении групповых операций.

- Уменьшение монтажной схемы. Несмотря на удвоенную по сравнению с PCI пропускную способность, hub-нтерфейс имеет ширину, равную 8 разрядам, и требует для соединения с системной платой всего лишь 15 сигналов. Шине PCI для выполнения подобной операции требуется не менее 64 сигналов, что приводит к повышению генерации электромагнитных помех, ухудшению сигнала, появлению “шума” и в конечном итоге — к увеличению себестоимости плат.

Конструкция hub-интерфейса предусматривает увеличение пропускной способности устройств PCI, что связано с отсутствием южного моста, передающего поток данных от микросхемы Super I/O и загружающего тем самым шину PCI. Таким образом, hub-архитектура позволяет увеличить пропускную способность устройств, непосредственно соединенных с южным мостом, к которым относятся новые быстродействующие интерфейсы ATA-100/133, Serial ATA 3 Гбит/с и USB 2.0.

Существует два основных варианта интерфейса концентратора.

- AHA (Accelerated Hub Architecture). Используется в серии набора микросхем 8xx. Это ускоренный в четыре раза (4x) 8-разрядный интерфейс, работающий на скорости 66 МГц с пропускной способностью 266 Мбит/с, что вдвое выше, чем у PCI.

- DMI (Direct Media Interface). Используется в наборах микросхем серий 9xx и 3xx. Это выделенное 4-полосное (шириной 4 бит) соединение PCI Express, позволяющее передавать по 1 Гбит/с по каждой из полос, что в 7,5–14 раз быстрее возможностей шины PCI.

Конструкция hub-интерфейса, ширина которого равна 4 или 8 бит, довольно экономична. Ширина интерфейса может показаться недостаточной, но такая конструкция полностью себя оправдывает. Меньшее число выводов говорит об упрощенной схеме маршрутизации платы, снижении количества помех и повышении устойчивости сигнала. Это также сокращает число выводов используемых микросхем, уменьшает их размеры и себестоимость. Таким образом, посредством очень узкой, но быстродействующей архитектуры интерфейс концентратора достигает высших показателей быстродействия, чем те, на которые была способна старая архитектура “северный/южный мост”.

Кроме того, в ICH содержится новая шина Low-Pin-Count (LPC), представляющая собой 4-разрядную версию шины PCI, которая была разработана, в первую очередь, для поддержки микросхем системной платы ROM BIOS и Super I/O. Вместе с четырьмя сигналами функций данных, адресов и команд для функционирования шины требуется девять дополнительных сигналов, что составляет в общей сложности 13 сигналов. Это позволяет значительно уменьшить количество линий, соединяющих ROM BIOS с микросхемами Super I/O. Для сравнения: в ранних версиях наборов микросхем в качестве интерфейса между северным и южным мостами использовалась шина ISA, количество сигналов которой равно 98. Максимальная пропускная способность шины LPC достигает 16,67 Мбайт/с, что примерно соответствует параметрам ISA и чего более чем достаточно для поддержки таких устройств, как ROM BIOS и микросхемы Super I/O.

Высокоскоростные соединения между микросхемами северного и южного мостов

- Подробности

- Родительская категория: Системные платы

- Категория: Наборы микросхем системной логики

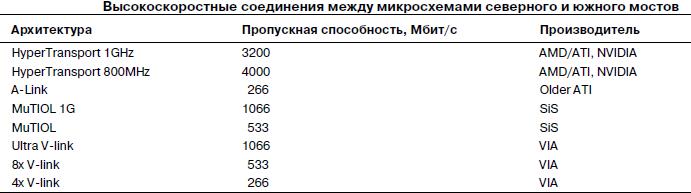

Intel — не единственная компания, которая стремится заменить медленное соединение по шине PCI между микросхемами северного и южного мостов более производительной альтернативой, не основанной на шине PCI. Ниже описываются подобные архитектуры, созданные несколькими компаниями.

- VIA. Интерфейс V-link обеспечивает взаимодействие микросхем северного и южного мостов со скоростью, равной быстродействию hub-архитектуры от Intel или превышающей его. В интерфейсе V-link применяется 8-разрядная шина данных, внедренная в нескольких версиях — V-link 4x, V-link 8x и Ultra V-link. Интерфейс V-link 4x передает данные со скоростью 266 Мбит/с (4×66 МГц), в два раза превышающей пропускную способность шины PCI и примерно равной быстродействию интерфейса AHA от Intel. В свою очередь, интерфейс V-link 8x передает данные с частотой 533 Мбайт/с (4×133 МГц), которая в два раза превышает аналогичные показатели AHA и HI 1.5. Интерфейс Ultra V-link передает данные со скоростью 1 Гбит/с, что в четыре раза выше скорости интерфейса AHA и равно быстродействию самой современной архитектуры от Intel — DMI.

- SiS. Интерфейс MuTIOL (также называемый гиперпотоковым) обеспечивает производительность, сопоставимую с интерфейсом V-link 4x; в архитектуре второго поколения MuTIOL 1G, используемой в современных наборах микросхем от SiS, производительность сравнима с Ultra V-link от SiS и DMI от Intel.

- ATI (ныне — подразделение AMD). В некоторых наборах микросхем серии IGP используется высокоскоростная шина A-Link. Этот интерфейс поддерживает передачу данных со скоростью 266 Мбайт/с, обладая производительностью, сравнимой с hub-архитектурой от Intel и первыми поколениями интерфейсов V-link и MuTIOL. В своих последних наборах микросхем ATI использует шину HyperTransport.

- NVIDIA. В наборах микросхем серии nForce внедрена шина HyperTransport, изначально разработанная компанией AMD.

Технические характеристики наборов микросхем от разных производителей представлены в таблице ниже.

Первые наборы микросхем системной логики 386/486 компании Intel

- Подробности

- Родительская категория: Системные платы

- Категория: Наборы микросхем системной логики

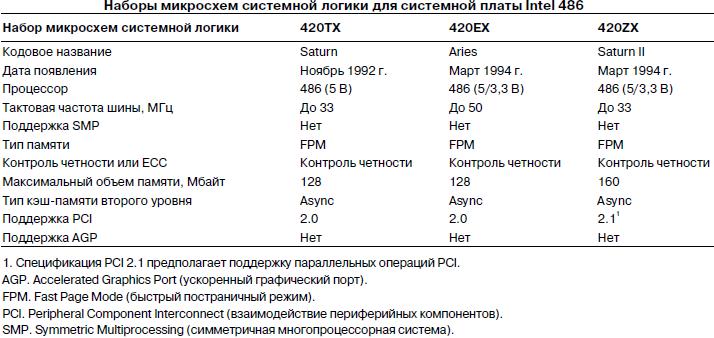

Первый набор микросхем системной логики 82350 предназначался для процессоров 386DX и 486. Но он успеха не имел, так как шина EISA не получила широкого распространения, к тому же многие производители выпускали наборы микросхем для этих процессоров. Однако ситуация на рынке постоянно изменялась, Intel отказалась от поддержки шины EISA, и последующие наборы микросхем системной логики для процессора 486 были намного удачливее.

В таблице ниже перечислены наборы микросхем системной логики для процессора Intel 486.

В наборе микросхем 420 впервые была представлена архитектура “северный/южный мост”, которая продолжает использоваться в некоторых моделях и по сей день.

Пятое поколение микросхем системной логики Pentium (P5)

- Подробности

- Родительская категория: Системные платы

- Категория: Наборы микросхем системной логики

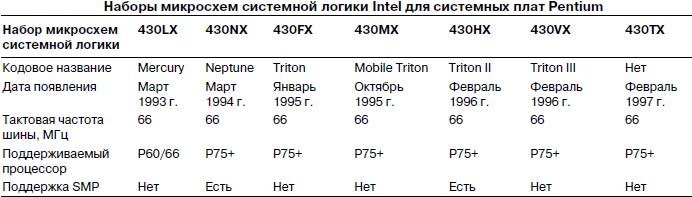

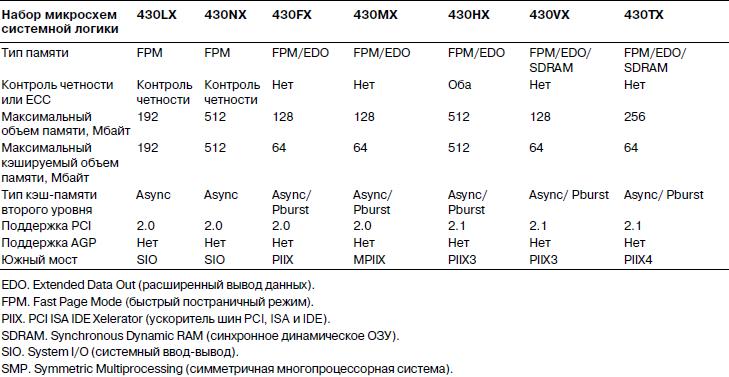

Одновременно с процессором Pentium в марте 1993 года Intel представила свой первый набор микросхем системной логики 430LX (под кодовым названием Mercury) для Pentium. Именно в этот год Intel серьезно занялась проектированием наборов микросхем системной логики и приложила все усилия, чтобы стать лидером на рынке. И поскольку у других производителей на проектирование наборов микросхем системной логики уходило несколько месяцев, а то и год, Intel очень скоро добилась своей цели. В табл. 4.14 перечислены наборы микросхем системной логики Intel для системных плат Pentium. Обратите внимание, что один из них не поддерживает порты AGP — эта поддержка была добавлена только в наборы микросхем, предназначенные для процессоров семейства Pentium II/Celeron.

Примечание!

Стандарт PCI 2.1 поддерживает параллельное выполнение операций на шине PCI.

В таблице ниже перечислены все микросхемы южного моста, составляющие вторую часть наборов микросхем системной логики пятого поколения процессоров на системных платах Intel.

Наборы микросхем для процессоров Pentium, перечисленные в таблицах, не выпускаются уже на протяжении нескольких лет. Основная часть компьютеров, в которых они использовались, уже давно находится на “свалке истории”.

Толчком к созданию наборов микросхем системной логики класса, отличного от Pentium, послужила разработка компанией AMD собственных аналогов Pentium — процессоров семейств K5 и K6. Процессор K5 не достиг больших успехов; в отличие от него процессоры семейства K6 заняли доминирующее положение на рынке недорогих систем, а также стали использоваться для модернизации систем Pentium. Компания AMD чаще использует компоненты сторонних производителей, чем собственные наборы микросхем. Но возможность своевременной поставки соответствующих наборов микросхем, позволяющих поддерживать продукты AMD, сделала процессор K6 и его наследников наиболее вероятными конкурентами процессоров семейств Intel Pentium MMX и Pentium II/III/Celeron. Эта же возможность подтолкнула других поставщиков, таких как VIA, Acer Laboratories и SiS, к поддержке процессоров AMD. К наиболее распространенным наборам микросхем для процессоров класса Pentium относятся следующие:

- AMD 640;

- VIA Apollo VP1, VP2, VPX, VP3, MVP3 и MVP4;

- ALi Aladdin 4, Aladdin 5 и Aladdin 7;

- SiS SiS540, SiS530/5595, SiS5598, SiS5581, SiS5582, SiS5571, SiS5591 и SiS5592.