Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

Шина IEEE 1394 — FireWire

Шина IEEE 1394 — FireWire

Устройство контроллера OHC

- Подробности

- Родительская категория: Шина IEEE 1394 — FireWire

- Категория: «Открытый» хост-контроллер IEEE 1394 — OHCI

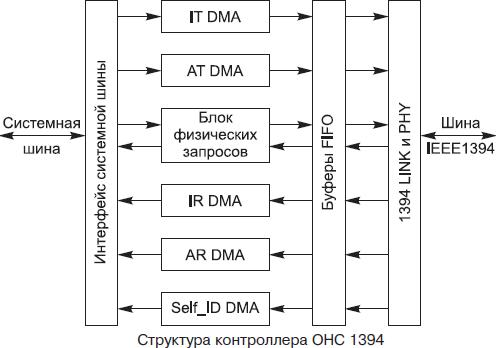

Упрощенная структурная схема OHC приведена на рисунке.

Интерфейс системной шины (Host Bus Interface) обеспечивает взаимодействие с контроллером в двух режимах:

- ведомый режим (PCI Target), обеспечивающий программный доступ к регистрам контроллера со стороны центрального процессора хоста;

- ведущий режим (PCI Bus Master), обеспечивающий контроллеру возможность прямого доступа к системной памяти хоста. В этом режиме интерфейс системной шины должен выдерживать поток данных, по крайней мере, базовой скорости S100 (100 Мбит/с) с накладными расходами на организацию прямого доступа к памяти.

Контроллеры DMA обеспечивают обмен данными между шиной и системной памятью. В OHC имеются семь типов контроллеров DMA:

- контроллер асинхронной передачи (AT DMA);

- контроллер асинхронного приема (AR DMA);

- блок физических запросов, в который входят два контроллера:

-----контроллер приема аппаратно-обрабатываемых запросов (Physical Receive);

-----контроллер ответов для аппаратно-обрабатываемых запросов (Physical Response); - контроллер изохронной передачи (IT DMA);

- контроллер изохронного приема (IR DMA);

- контроллер приема пакетов самоидентификации (Self_ID DMA).

равляющих работой канала и выборкой запросов из списков, расположенных в системной памяти. Контроллеры асинхронной передачи и приема имеют отдельные контексты для запросов и ответов шинных транзакций. Контроллеры изохронного приема и передачи могут иметь до 32 контекстов каждый. Назначение и работа контроллеров подробно описано ниже.

LINK-уровень OHC передает пакеты из FIFO-буферов передающих каналов и отдает в FIFO принятые пакеты с корректным адресом, предназначенные данному узлу. Уровень выполняет следующие действия:

- передает и принимает пакеты форматов IEEE 1394;

- генерирует соответствующие пакеты квитирования для принятых асинхронных пакетов, отрабатывая однофазный или двухфазный протокол повторов;

- выполняет функции мастера циклов;

- генерирует и проверяет корректность 32-битных CRC-кодов;

- обнаруживает пропуски пакетов начала цикла;

- взаимодействует с регистрами PHY;

- принимает изохронные пакеты (все время);

- игнорирует асинхронные пакеты во время изохронной фазы цикла.

Буферы FIFO, находящиеся между каналами DMA и LINK-уровнем, выполняют промежуточную буферизацию данных, считываемых из системной памяти для передачи в шину и принятых из шины для записи в память. Буферы FIFO обеспечивают и согласование выравнивания данных, побайтного для хоста и поквадлетного для шины 1394. При необходимости буферы FIFO вставляют байты-заполнители, выравнивающие данные до границ квадлетов. Переполнение (overflow) или переопустошение (underrun) буферов (по вине интерфейса системной шины и памяти), приводящее к потерям принимаемых или передаваемых пакетов, контролируется аппаратными средствами OHC.

Буферы могут «на лету» выполнять преобразование форматов представления квадлетов. Шина IEEE 1394 и, соответственно, LINK-eровень работают с квадлетами, представленными в формате Big Еndian (старший байт передается первым). Передача данных через хост-интерфейс может выполняться по выбору:

- в формате Big Endian, используемом на платформах фирмы Apple;

- в формате Little Endian (младший байт передается первым), используемом на платформах фирмы Intel.

Для поддержки функций управления OHC имеет 64-битный регистр уникального идентификатора (GUID, он же IEEE EUI-64), автоматически загружаемый из энергонезависимой памяти по сбросу контроллера (или однократно программируемый в самом контроллере).

Для выполнения функций диспетчера изохронных ресурсов контроллер имеет четыре автономных регистра, реализующих блокированные операции (compare_swap) как со стороны шины, так и со стороны хоста.

Архитектура сети

- Подробности

- Родительская категория: Шина IEEE 1394 — FireWire

- Категория: Основная информация

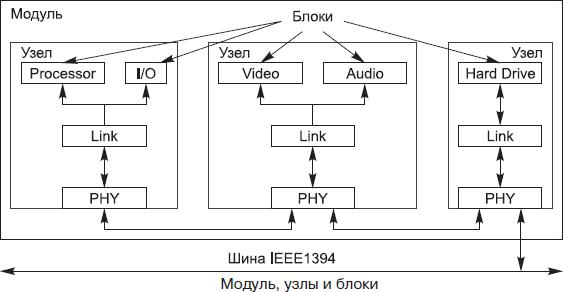

Архитектура IEEE 1394 позволяет организовывать сети, состоящие из одной или нескольких (до 1023) шин, причем не только последовательных. К шинам IEEE 1394 подключаются физические устройства, которые должны иметь по крайней мере один порт. Физическое устройство может иметь сложную внутреннюю структуру, что иллюстрирует см. рисунок. К топологии сети относятся следующие понятия:

- сеть — совокупность узлов, подключенных к одной шине или нескольким шинам, соединенным мостами. Все узлы сети имеют возможность взаимодействия друг с другом;

- шина — совокупность узлов, связанных друг с другом кабельными сегментами. Все узлы шины используют ее общую (разделяемую) среду передачи, получая право на передачу путем арбитража. Подключение-отключение узлов вызывает реконфигурацию данной шины, в ходе которой узлы получают новые номера (физические адреса);

- модуль (module) — физическое устройство («коробка»), подключаемое к шине, и содержащее один или несколько узлов;

- узел (node) — логический объект, имеющий уникальный физический адрес на шине. Узел имеет собственное адресное пространство, в котором обязательно присутствуют стандартные регистры управления и состояния (CSR), а также постоянная память (ROM) со стандартным набором структур, описывающих узел;

- порт (port) — внешний физический интерфейс узла, обеспечивающий соединение узлов в шину. Узел может иметь несколько портов, что обеспечивает связь множества узлов без использования каких-либо дополнительных устройствконцентраторов;

- блок (unit) — часть узла, обеспечивающая его отдельную функциональность: память, ввод/вывод, обработку данных. Блоки имеют свои регистры и/или области памяти, отображенные на общее адресное пространство узла. Блоки функционируют относительно независимо и управляются собственными драйверами.

Если проводить параллели с USB, блок (IEEE 1394) можно соотнести с интерфейсом (USB), узел 1394 — с устройством USB, а модуль 1394 — с композитным устройством USB, содержащим несколько функций и хаб. Понятие шины в USB и IEEE 1394 совпадает, хотя организация и возможности этих шин значительно различаются. Аналога сети в USB нет.

Шина IEEE 1394 позволяет любому узлу взаимодействовать с другими различными путями:

- выполнять асинхронные транзакции чтения и записи с регистрами и областями памяти другого (удаленного) узла. При этом сами операции в удаленном узле могут выполняться как чисто аппаратно (прямой доступ к памяти удаленного узла), так и программными средствами удаленного узла;

- передавать и принимать потоки данных по изохронным каналам (с гарантированной полосой пропускания, но без гарантий доставки);

- передавать и принимать асинхронные потоки данных (без гарантий);

- выполнять блокированные транзакции (чтение-модификация запись) со специальными регистрами удаленного узла. Эти транзакции служат для упорядочивания взаимодействия с какими-либо ресурсами, к которым может обращаться множество узлов шины;

- вызывать прерывания на удаленном узле (асинхронно транзакцией записи в специальный регистр узла).

Асинхронные транзакции могут быть как направленными (адресованными конкретному узлу), так и широковещательными. Для направленных асинхронных транзакций протокол шины обеспечивает надежную доставку. Потоковые передачи также могут быть широковещательными и направленными.

Формы выполнения транзакций

- Подробности

- Родительская категория: Шина IEEE 1394 — FireWire

- Категория: Передача данных по шине IEEE 1394

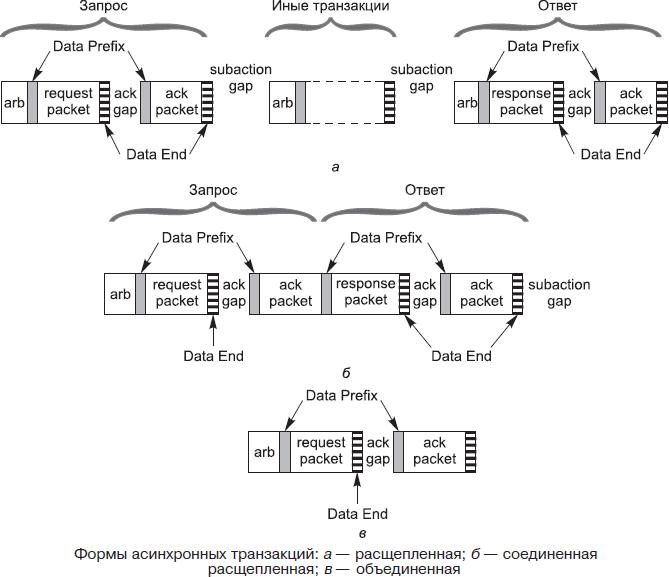

Асинхронные транзакции могут выполняться в разных формах, различающихся числом субакций, необходимостью квитирования и способом получения права передачи (количеством операций арбитража). Эти формы иллюстрирует рисунок. На рисунке показаны операции арбитража (arb), короткие зазоры подтверждений (ack gap), длинные зазоры субакций (subaction gap), признаки начала (Data Prefix) и конца (Data End) пакетов.

Расщепленные транзакции используются при обращении к медленным устройствам (рис. а). Здесь между запросом и ответом могут вклиниваться другие транзакции на шине, так что перед ответом требуется арбитраж и зазор. В этой форме могут выполняться запись (Split Write), чтение (Normal Split Read) и блокированные транзакции (Normal Split Lock);

Соединенные расщепленные транзакции используются при обращении к быстрый устройствам (рис. б). Здесь пакет ответа передается сразу за пакетом квитирования (отделяясь только префиксом данных), так что дополнительный арбитраж (и зазор) не требуется. В этой форме могут выполняться запись (Concatenated Split Write), чтение (Concatenated Read) и блокированные транзакции (Concatenated Lock);

Объединенные транзакции используются в тех случаях, когда не требуется содержательного ответа (рис. в). В этой форме возможна только запись (Unified Write) — самый быстрый вариант, предназначенный для тех операций, которые заведомо проходят успешно (или успех не волнует запросчика).

Усовершенствование арбитража в IEEE 1394a

- Подробности

- Родительская категория: Шина IEEE 1394 — FireWire

- Категория: Арбитраж и распределение времени шины IEEE 1394

Простота механизма арбитража оборачивается бесполезным расходованием времени на зазоры. Эти расходы снижают эффективную пропускную способность шины, особенно для коротких пакетов и пакетов, передаваемых на высокой скорости. Для скорости S100 на пакетах максимального размера эффективность использования шины составляет 80%, на коротких (64 байта данных) эффективность падает до 20%. При скорости S400 на длинных пакетах эффективность снижается до 50%, а на коротких — до 10%. В IEEE 1394a введен приоритетный арбитраж и ускоренные механизмы, сокращающие издержки времени на выжидание интервалов зазоров.

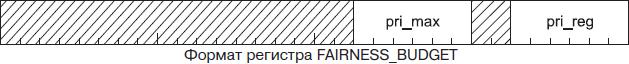

Приоритетный арбитраж (в IEEE 1394a) позволяет узлу за один интервал справедливости передать более одного асинхронного запроса. Число запросов, разрешенных узлу за один интервал, определяется полем pri_req его регистра FAIRNESS_BUDGET (смещение 218h в пространстве регистров CSR, другое имя того же регистра — PRIORITY_BUDGET, формат приведен на рисунке). Значение этого поля заносит диспетчер шины исходя из числа узлов и их потребностей, которые они сообщают в поле pri_max своих регистров. Диспетчер назначает узлам значения pri_req, так чтобы их сумма не превышала 63–N, где N — число узлов на шине.

Механизмы ускорения позволяют посылать пакеты запросов и ответов «с оказией», без задержек арбитража. Ускорения позволяют узлам, находящимся дальше от корня, обогнать в арбитраже более близкие к корню узлы, находящиеся в более выгодном положении. Однако и при использовании механизмов ускорения должен соблюдаться интервал справедливости. Ускорения используются узлами с «умным» PHY, способным анализировать пакеты. Ускорения могут быть реализованы двумя способами:

- используя ускоренный арбитраж, основанный на пакетах квитирования (ackaccelerated). Здесь возможны два варианта:

- узел, отвечающий пакетом квитирования на какой-либо запрос (ответ), может послать свой асинхронный пакет запроса (ответа) вслед за пакетом-квитанцией, отделяя его лишь префиксом данных. Таким образом производится соединение (конкатенация) двух пакетов;

- узел, желающий послать пакет запроса или ответа, дожидается прохождения пакета-квитанции и с коротким зазором (40 нс, как у изохронного арбитража) посылает запрос арбитража. При этом он опередит обычный узел, который в этом случае будет выдерживать нормальный асинхронный зазор.

- Арбитраж «на лету» (Fly-by) позволяет узлу присоединять свой пакет запроса к пакету, транслируемому им в сторону корня и не требующему квитирования (то есть к изохронным пакетам и квитанциям). При этом нельзя присоединять пакет, передаваемый на скорости S100, к пакетам, идущим на более высокой скорости (S100 передается без сигнализации о скорости, так что устройства 1394 будут ошибочно пытаться принять этот пакет на скорости пакета-«носителя»).

Во время исполнения ускоренного арбитража корневой узел не имеет возможности захватить шину. Если он работает мастером циклов (необходимым для изохронного обмена), то он может не суметь вовремя передать пакет начала цикла. Чтобы этого не происходило, узлы с ускоренным арбитражем должны иметь регистры CYCLE_TIME и запрещать ускоренный арбитраж близко к ожидаемой границе цикла, пока не получат очередной пакет начала цикла.

В бета-режиме IEEE 1394b введен новый метод арбитража — BOSS (Bus Owner/Supervisor/Selector), предназначенный как для чистых B-шин, все узлы которых работают в бета-режиме, так и для гибридных шин, часть узлов которых работает с традиционной DS-сигнализацией. Метод BOSS позволяет передавать запросы на право передачи во время передачи пакетов, что обеспечивает конвейеризацию работы шины и сокращает ее простои.

Идентификация дерева

- Подробности

- Родительская категория: Шина IEEE 1394 — FireWire

- Категория: Конфигурирование шины и узлов IEEE 1394

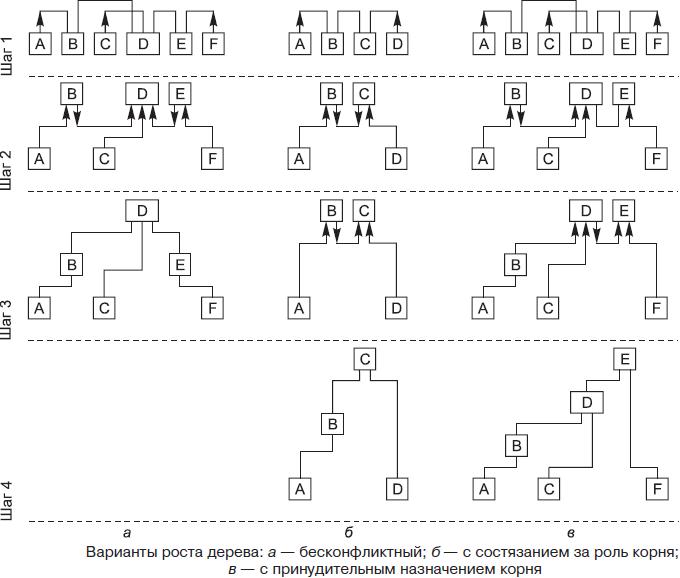

Во время идентификации дерева узлы выстраиваются в иерархическую структуру и выбирается корень шины. Для узлов идентификация дерева сводится к определению статуса активных портов: присвоение им типов: c-порт (к которому подключен дочерний узел) или p-порт (которым он подключается к родительскому). Этап идентификации дерева начинается после сброса. Для идентификации используется сигнализация арбитража.

В начале идентификации дочерние узлы ищут своих родителей, посылая им сигнал уведомления Parent_Notify, а родители признают свои дочерние узлы сигналом Child_Notify. Сигнал Parent_Notify безусловно посылают узлы-листья (имеющие всего по одному порту). Узлы-ветви могут послать сигнал Parent_Notify только на один из своих портов, при условии, что на все остальные активные порты пришли аналогичные сигналы. При этом порты, на которые пришел сигнал Parent_Notify, помечаются как c-порты. На эти порты посылается уведомление Child_Notify, но не раньше, чем когда сигнал Parent_Notify будет обнаружен на всех активных портах, кроме одного. Порт, на который пришел сигнал Child_Notify, помечается как p-порт; он перестает посылать сигнал Parent_Notify, что является подтверждением приема сигнала Child_Notify.

Узел, у которого на все порты приходят сигналы Parent_Notify, становится корнем. Все его порты становятся c-портами. Он посылает на эти порты сигнал Child_Notify, а получив подтверждение (снятые сигналы Parent_Notify), и сам прекращает подавать сигналы Child_Notify. На этом идентификация дерева заканчивается, и шина переходит к этапу самоидентификации узлов.

Возможна ситуация, когда два соединенных узла пытаются друг в друге найти своих родителей, посылая сигнал Parent_Notify. При этом столкновение данных сигналов приводит к приему каждым портом состояния Root_Contention — признака состязания за роль корня. В этом случае оба узла перестают подавать сигнал на эти порты и через случайный интервал проверяют их состояние. Узел, обнаруживший состояние покоя на данном порте, посылает сигнал Parent_Notify. Узел, обнаруживший этот сигнал, посылает сигнал Child_Notify и становится корнем. В начале состязания каждый узел случайным образом устанавливает для себя время задержки из двух вариантов:

- ROOT_CONTEND_FAST (0,24–0,26 мкс) — быстрый участник;

- ROOT_CONTEND_SLOW (0,57–0,6 мкс) — медленный участник.

Тот узел, который окажется быстрее, корнем не станет (он раньше начнет искать родителя). Если оба участника выберут одинаковое время, то они опять столкнутся и повторят состязание с новыми значениями задержки.

На том, что в состязании за роль корня побеждает самый медленный участник, построен механизм принудительного назначения корня. У каждого PHY есть бит RHB, единица в котором заставляет этот узел задерживать подачу сигнала поиска родителей на 83–167 мкс от начала идентификации дерева. Специальный пакет физического конфигурирования позволяет установить этот бит у заданного узла и сбросить у всех остальных, что обеспечит победу данному узлу в последующих выборах корня по ближайшему сигналу сброса. Если вдруг окажется, что бит RHB установлен у нескольких узлов, то они разыграют право стать корнем по вышеописанному правилу случайных состязаний.

На рисунке приведены пошаговые сценарии роста дерева, на каждом шаге определяется очередной уровень иерархии узлов. Стрелками на рисунке обозначены сигналы Parent_Notify, определяющие роли портов и узлов. На рисунке изображены три различных пошаговых сценария вырастания дерева:

- бесконфликтный (рис. а);

- с состязанием между узлами B и C (рис. б);

- с принудительным назначением роли корня для узла E (рис. в). В этом примере показано, как благодаря выдержке узла E из той же топологии соединений, что была и на рис. а, вырастает иное дерево.

В случае образования петли процесс идентификации дерева «зависает». Эта ситуация выявляется по срабатывании тайм-аута арбитража (167 мкс); она сигнализируется через LINK приложению и пользователю, который должен принять меры к разрыву петли (физическим переключением кабелей). В 1394b приняты меры по автоматической борьбе с петлями путем запрещения работы какого-либо порта по результатам проверки.

Еще статьи...

Подкатегории

-

Основная информация

- Кол-во материалов:

- 8

-

Физический уровень шины IEEE 1394

- Кол-во материалов:

- 13

-

Управление шиной IEEE 1394

- Кол-во материалов:

- 9

-

Конфигурирование шины и узлов IEEE 1394

- Кол-во материалов:

- 8

-

Арбитраж и распределение времени шины IEEE 1394

- Кол-во материалов:

- 5

-

Передача данных по шине IEEE 1394

- Кол-во материалов:

- 12

-

«Открытый» хост-контроллер IEEE 1394 — OHCI

- Кол-во материалов:

- 11

-

Взаимодействие с физическим уровнем шины IEEE 1394

- Кол-во материалов:

- 7