Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

http://xcoffee.ru чай в треугольных пакетиках название: просторечное название.

Шина IEEE 1394 — FireWire

Устройство контроллера OHC

- Подробности

- Родительская категория: Шина IEEE 1394 — FireWire

- Категория: «Открытый» хост-контроллер IEEE 1394 — OHCI

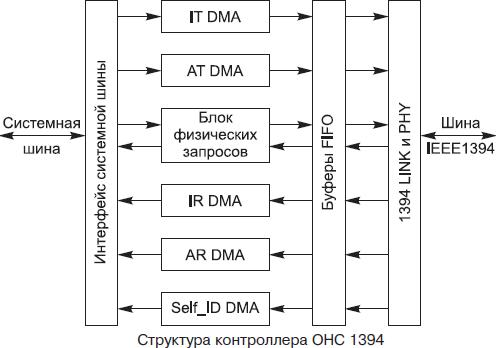

Упрощенная структурная схема OHC приведена на рисунке.

Интерфейс системной шины (Host Bus Interface) обеспечивает взаимодействие с контроллером в двух режимах:

- ведомый режим (PCI Target), обеспечивающий программный доступ к регистрам контроллера со стороны центрального процессора хоста;

- ведущий режим (PCI Bus Master), обеспечивающий контроллеру возможность прямого доступа к системной памяти хоста. В этом режиме интерфейс системной шины должен выдерживать поток данных, по крайней мере, базовой скорости S100 (100 Мбит/с) с накладными расходами на организацию прямого доступа к памяти.

Контроллеры DMA обеспечивают обмен данными между шиной и системной памятью. В OHC имеются семь типов контроллеров DMA:

- контроллер асинхронной передачи (AT DMA);

- контроллер асинхронного приема (AR DMA);

- блок физических запросов, в который входят два контроллера:

-----контроллер приема аппаратно-обрабатываемых запросов (Physical Receive);

-----контроллер ответов для аппаратно-обрабатываемых запросов (Physical Response); - контроллер изохронной передачи (IT DMA);

- контроллер изохронного приема (IR DMA);

- контроллер приема пакетов самоидентификации (Self_ID DMA).

равляющих работой канала и выборкой запросов из списков, расположенных в системной памяти. Контроллеры асинхронной передачи и приема имеют отдельные контексты для запросов и ответов шинных транзакций. Контроллеры изохронного приема и передачи могут иметь до 32 контекстов каждый. Назначение и работа контроллеров подробно описано ниже.

LINK-уровень OHC передает пакеты из FIFO-буферов передающих каналов и отдает в FIFO принятые пакеты с корректным адресом, предназначенные данному узлу. Уровень выполняет следующие действия:

- передает и принимает пакеты форматов IEEE 1394;

- генерирует соответствующие пакеты квитирования для принятых асинхронных пакетов, отрабатывая однофазный или двухфазный протокол повторов;

- выполняет функции мастера циклов;

- генерирует и проверяет корректность 32-битных CRC-кодов;

- обнаруживает пропуски пакетов начала цикла;

- взаимодействует с регистрами PHY;

- принимает изохронные пакеты (все время);

- игнорирует асинхронные пакеты во время изохронной фазы цикла.

Буферы FIFO, находящиеся между каналами DMA и LINK-уровнем, выполняют промежуточную буферизацию данных, считываемых из системной памяти для передачи в шину и принятых из шины для записи в память. Буферы FIFO обеспечивают и согласование выравнивания данных, побайтного для хоста и поквадлетного для шины 1394. При необходимости буферы FIFO вставляют байты-заполнители, выравнивающие данные до границ квадлетов. Переполнение (overflow) или переопустошение (underrun) буферов (по вине интерфейса системной шины и памяти), приводящее к потерям принимаемых или передаваемых пакетов, контролируется аппаратными средствами OHC.

Буферы могут «на лету» выполнять преобразование форматов представления квадлетов. Шина IEEE 1394 и, соответственно, LINK-eровень работают с квадлетами, представленными в формате Big Еndian (старший байт передается первым). Передача данных через хост-интерфейс может выполняться по выбору:

- в формате Big Endian, используемом на платформах фирмы Apple;

- в формате Little Endian (младший байт передается первым), используемом на платформах фирмы Intel.

Для поддержки функций управления OHC имеет 64-битный регистр уникального идентификатора (GUID, он же IEEE EUI-64), автоматически загружаемый из энергонезависимой памяти по сбросу контроллера (или однократно программируемый в самом контроллере).

Для выполнения функций диспетчера изохронных ресурсов контроллер имеет четыре автономных регистра, реализующих блокированные операции (compare_swap) как со стороны шины, так и со стороны хоста.