Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

Шина IEEE 1394 — FireWire

Интерфейс PHY-LINK 1394 и 1394a

- Подробности

- Родительская категория: Шина IEEE 1394 — FireWire

- Категория: Взаимодействие с физическим уровнем шины IEEE 1394

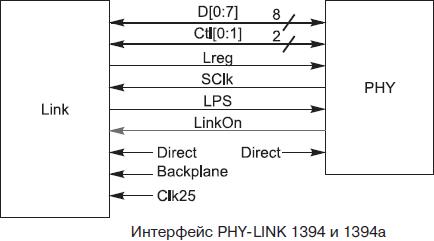

Интерфейс PHY–LINK изображен на рисунке ниже, назначение сигналов раскрыто в следующей таблице. Интерфейс содержит небольшое количество сигналов, и именно для этих сигналов и возможно введение гальванической развязки.

На рисунке приведены сигналы для обоих вариантов шины — кабельной и кроссшины. Описание интерфейса, приведенное ниже, относится к самому распространенному варианту — кабельной шине. В этом варианте не используются (отсутствуют) сигналы Clk25 и Bacкlplane.

Для кросс-шины в интерфейсе LINK-PHY сигнал SClk имеет пониженную частоту (24,756 или 12,288 МГц для S50 и S25 соответственно); для идентификации используемой частоты введен сигнал Clk25 (0 — 12,288 МГц, 1 — 24,576 МГц). Признаком подключения LINK-уровня к Backplane PHY является дополнительный сигнал Backplane (от PHY к LINK’у).

Таблица. Сигналы интерфейса LINK-PHY

| Сигнал | Назначение |

| D[0:7] | Двунаправленная шина данных. На S100 используются только линии D[0:1], на S200 — D[0:3], на S400 — D[0:7] |

| Ctl[0:1] | Состояние интерфейса |

| LReq | Link Request, последовательный интерфейс, по которому LINK инициирует запрос к PHY (для передачи пакетов и обращения к регистрам) |

| SClk | Синхронизация (49,152 МГц) для вышеприведенных сигналов. Источник меняет состояние сигнала по спаду SClk, приемник фиксирует состояние по фронту SClk |

| LPS | Link Power Status, признак активности (включения) LINK-уровня |

| LinkOn | Сигнал для включения LINK-уровня |

| Direct | Признак непосредственного соединения LINK-PHY (нет дифференцирования сигналов) |

Интерфейсом управляет PHY; LINK может посылать запросы только в определенных состояниях интерфейса. Право передачи информации по двунаправленным линиям данных LINK получает от PHY. Текущее состояние интерфейса (использование шины данных) определяется сигналами Ctl[0:1] в соответствии с со следующей таблицей.

Таблица. Состояние интерфейса LINK-PHY

| Ctl[0:1] | Состояние интерфейса |

| Линиями Ctl[0:1] управляет PHY: | |

| 00 | Idle — нет активности (LINK может посылать запрос) |

| 01 | Status — PHY по шине данных посылает информацию о событиях или ответ на запрос чтения регистра |

| 10 | Receive — PHY передает LINK-уровню пакет, принимаемый с шины, или генерируемый им (PHY-пакет), или пакет ответа на запрос к регистрам PHY |

| 11 | Grant — PHY передает LINK’у право использования шины данных |

| Линиями Ctl[0:1] управляет LINK: | |

| 00 | Idle — нет активности: LINK завершил передачу и отдает управление интерфейсом уровню PHY |

| 01 | Hold — LINK удерживает шину, готовясь к передаче пакета (или после передачи пакета, собираясь послать следующий без повторного арбитража) |

| 10 | Transmit — LINK передает данные PHY (для передачи в шину или обращения к регистрам PHY) |

| 11 | Не используется |

В состоянии Status PHY по линиям данных D[0:1] за два такта передает 4 бита состояния (Stat[0:1] в первом такте и Stat[2:3] во втором

Таблица. Состояние, сообщаемое PHY

| Бит | Значение |

| 0 | ARB_RESET_GAP — обнаружение зазора сброса арбитража (указание на начало нового интервала справедливости) |

| 1 | SUBACTION_GAP — обнаружение нормального зазора арбитража (можно запрашивать право посылки очередного асинхронного пакета) |

| 2 | BUS_RESET_START — обнаружение сброса на шине |

| 3 | PHY_INTERRUPT — прерывание от PHY, причина уточняется чтением PHY-регистра 0101b. Возможные события: обнаружение петли во время идентификации дерева; обнаружение снижения питающего напряжения (ниже 7,5 В); обнаружение тайм-аута арбитража; обнаружение изменения напряжения смещения |

Доступ к регистрам PHY

Обращение к регистрам PHY (см. далее) через запросы от LINK разрешено в любом состоянии интерфейса, за исключением времени, когда PHY занят обработкой предыдущего запроса чтения. Запросы обращения к регистрам выполняются всегда, их может отменить только сигнал сброса. Запрос передается в последовательном коде по линии LReq. Для запросов обращения к регистрам PHY в теле передается адрес регистра, а в запросе записи — и сами данные записи. В запросе чтения в битах [4:7] передается адрес запрашиваемого регистра, бит 8=0 — стоп бит. В запросах записи после адреса в битах [8:15] передается записываемый байт. Ответ на запрос чтения регистра передается по линиям D[0:1] в состоянии Status за 8 тактов (передаются 16 бит). За первые 2 такта передается текущее значение состояния, далее передается 4-битный адрес регистра и 8 бит считанных данных.

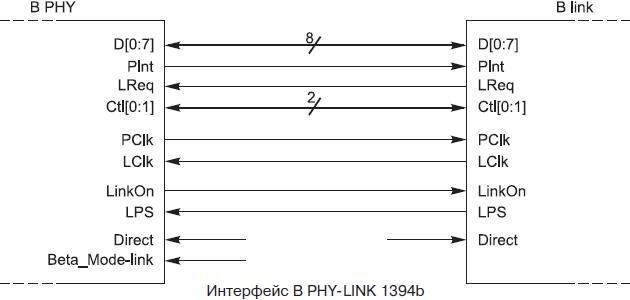

Параллельный интерфейс B PHY-LINK 1394b

В IEEE 1394b параллельный интерфейс между физическим уровнем и LINK-уровнем модифицирован для поддержки высоких скоростей и бета-режима, и этот вариант интерфейса называется B PHY-LINK. Схема интерфейса приведена на следующем рисунке, назначение сигналов — в следующей таблице. Этот интерфейс обеспечивает передачу данных на скоростях вплоть до S800. Здесь в шине данных всегда используются все 8 бит, а при передаче на более низких скоростях байты данных растягиваются до 2, 4 или 8 тактов. Интерфейс может работать и в традиционном режиме (1394/1394a), при этом он синхронизируется от линии PClk (она будет играть роль SCLK), частота этого сигнала становится 49,152 МГц. Сигналы LClk и PInt при этом не используются.

Таблица. Сигналы интерфейса LINK-PHY 1394b

| Сигнал | Назначение |

| D[0:7] | Двунаправленная шина, по которой передаются данные, код скорости и тип запроса. Данные от PHY синхронизируются по PClk, данные от LINK — по LClk |

| Pint | PHY Interrupt, линия для последовательной передачи информации о состоянии PHY, содержимого регистров и прерываний по событиям |

| Ctl[0:1] | Состояние (фаза) интерфейса синхронизируется по PClk, когда интерфейсом управляет PHY, и по LClk, когда интерфейсом управляет LINK |

| LReq | Link Request, последовательный интерфейс, по которому LINK инициирует запрос к PHY (для передачи пакетов и обращения к регистрам) Синхронизируется по LClk |

| PClk | Синхронизация (98,304 МГц) для сигналов, передаваемых от PHY. Источник синхронизации — PHY |

| LClk | Синхронизация для сигналов, передаваемых от LINK. Сигнал вырабатывается LINK’ом из PClk и совпадает с ним по частоте |

| LPS | Lint Power Status, признак активности (включения) LINK-уровня |

| LinkOn | Сигнал для включения LINK-уровня |

| Beta_Mode_link | Признак работы интерфейса в режиме 1394b (при отсутствии сигнала интерфейс работает в режиме 1394a) |

| Direct | Признак непосредственного соединения LINK-PHY (нет дифференцирования сигналов) |

Интерфейсом управляет PHY или LINK, текущее состояние интерфейса (использование шины данных) определяется сигналами Ctl[0:1] в соответствии с таблицей ниже. По сравнению с 1394a интерфейс изменен в том, что все обращения к регистрам PHY происходят без использования шины данных: записываемые данные передаются по линии LReq, а считываемые данные и прерывания от PHY приходят по линии PInt.

Таблица. Состояние интерфейса B PHY-LINK (1394b)

| Ctl[0:1] | Состояние интерфейса |

| Линиями Ctl[0:1] управляет PHY: | |

| 00 | Idle — нет активности (дежурное состояние) |

| 01 | Status — PHY по шине данных посылает информацию о состоянии шины |

| 10 | Receive — PHY передает LINK-уровню пакет, принимаемый с шины |

| 11 | Grant — PHY передает LINK’у право использования шины данных |

| Линиями Ctl[0:1] управляет LINK: | |

| 00 | Idle — нет активности: LINK завершил передачу и отдает управление интерфейсом уровню PHY |

| 01 | Transmit — LINK передает данные PHY |

| 10 | Не используется |

| 11 | Hold/More_Info — LINK удерживает шину, готовясь к передаче пакета. В конце передачи пакета указывает на передачу следующего запроса |

Данные, принимаемые и передаваемые по параллельной шине, растягиваются на n-тактов, в зависимости от скорости передачи: для S100 n = 8, для S200 n = 4, для S400 n = 2, для S800 каждый байт передается только в одном такте (n = 1). Более высокие скорости данным интерфейсом не поддерживаются.