Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

http://www.bereg.net/ высококачественная пухлая Мелованная бумага. Закрытые шкафы для документов moi-goda.ru.

Шина IEEE 1394 — FireWire

Архитектурные регистры CSR

- Подробности

- Родительская категория: Шина IEEE 1394 — FireWire

- Категория: Конфигурирование шины и узлов IEEE 1394

Шина IEEE 1394 основана на стандарте ISO/IEC13213, известном под названием «CSR-архитектура», и наследует его основные регистры и структуры данных в памяти конфигурации. Архитектурные регистры CSR занимают первые 512 байт в начальном адресном пространстве узла. Часть регистров CSR-архитектуры в IEEE 1394 не используется, их описание здесь опущено.

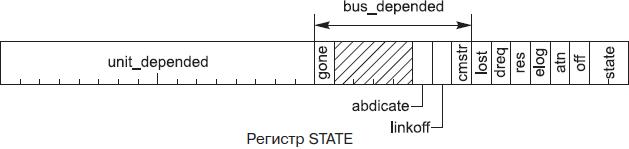

Регистр состояния и управления STATE (см. рисунок ниже) доступен для чтения по двум адресам — State_Clear (000h) и State_Set (004h). Некоторые биты доступны лишь для чтения (RO), другие биты допускают программный сброс (записью единиц в биты State_Clear) и аналогичную установку (через регистр State_Set). Назначение полей регистра состояния и управления:

- unit_depended — биты, специфичные для устройства;

- bus_depended — биты, специфичные для шины:

-----gone — бит, устанавливаемый по любому сбросу (устройства или шины) или по команде. Запрещает устройству посылку запросов. Обнуляется программно (возможно, и удаленно) при инициализации, когда устройство становится способным отвечать на запросы;

-----abdicate — бит, предназначенный для смены диспетчера шины. Устанавливается у узла, который должен стать диспетчером шины после грядущего сброса. При этом он не будет ждать положенных 125 мс (как «честные» кандидаты) перед тем, как сделать попытку блокированной транзакции с регистром BUS_MANAGER_ID;

-----linkoff — состояние питания LINK-уровня, питающегося от шины (1 — отключено). Может быть установлен программно, обнуляется (и включается питание) по приему пакета Link_On;

-----cmstr — признак мастера циклов. Может быть установлен только у корневого узла. - lost — потеря работоспособного состояния (по сбросу питания или фатальной ошибке;

- dreq (disable request) — запрет генерации запросов транзакций;

- atn, off — резервные биты в 1394;

- elog — признак обновления информации в журнале ошибок;

- state (RO) — состояние узла: 00 — рабочее (running), инициализация завершена; 01 — идет инициализация; 10 — тестирование (по запуску через запись в регистр Test_Start); 11 — фатальная ошибка (узел неработоспособен).

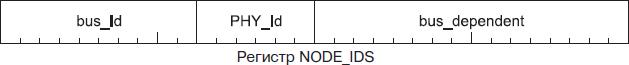

Регистр идентификатора узла NODE_IDS (см. следующий рисунок) содержит поля:

- bus_id — идентификатор шины (по умолчанию 0), команда сброса на него не влияет; этот идентификатор записывается и считывается программно;

- PHY_ID — идентификатор узла, устанавливаемый при автоконфигурировании;

- Bus_dependent — поле, зарезервированное для нужд шины.

Регистр команды сброса Reset_Start (00Ch) служит для подачи команды сброса (операцией записи), при этом значим только бит nt (no test, бит 31), единица в котором отменяет начальное тестирование узла при сбросе.

Регистры тайм-аута расщепленных транзакций позволяют задать предельное время ожидания ответа на запрос транзакции в пределах 8 с с дискретностью 125 мкс. Начальное значение — 100 мс, по сбросу не изменяется. В младших трех битах SPLIT_TIMEOUT_HI (018h) содержится число секунд, в старших 13 битах SPLIT_TIMEOUT_LO (01Ch) содержится число 125-микросекундных интервалов.

Регистры тестирования (необязательные) служат для запуска теста (TEST_START, 028h), передачи параметров теста (ARGUMENT_HI, 020h, ARGUMENT_LO, 022h) и сообщения состояния выполнения (TEST_STATUS, 02Ch).

Регистры прерываний (необязательные) служат для управления прерываниями, вызываемыми транзакциями записи в регистр INTERRUPT_TARGET (050h). Каждый бит этого регистра соответствует одному из условий (событий) прерывания; самый старший бит соответствует прерыванию с самым высоким приоритетом. Регистр INTERRUPT_MASK позволяет селективно выбирать условия, вызывающие сигнализацию прерывания приложению (процессору) данного узла (единичное значение бита маски разрешает прерывание по данному условию). Прерывания по шине могут посылаться широковещательно (адресуясь к регистру INTERRUPT_TARGET при Dest_ID = 63) или направленно, с указанием в целевом адресе идентификатора требуемого узла.

Регистры синхронизации (Clock_Value, Clock_Tick_Period, Clock_Strobe_Arrived, Clock_Info) в IEEE 1394, как правило, не используются — их функции выполняет регистр CYCLE_TIME).

Регистры сообщений (необязательные) Message_Request, Message_Response служат для передачи и приема широковещательных сообщений, адресованных всем узлам шины или всем блокам узла.