Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

Как бурят скважины на воду как пробурить скважину.

Память. Верхний уровень

Поддержка многозадачности в защищенном режиме процесоров 386+

- Подробности

- Родительская категория: Память. Верхний уровень

- Категория: Трансляция адреса в защищенном режиме в проц-х x86

В защищеном режиме процессоров 386+ имеется аппаратная поддержка переключения задач, что облегчает работу создателя многозадачных операционных систем. Переключение на новую задачу во многом напоминает вызов подпрограммы, но при переключении задач автоматически сохраняется гораздо больше информации о состоянии процессора в специальных системных структурах данных.

Далее перечислены эти структуры, а также регистры процессора, поддерживающие многозадачность:

1) Сегменты состояния задачи (Task State Segment TSS);

2) Дескрипторы сегмента состояния задачи;

3) Дескрипторы шлюзов вызова задачи;

4) Регистр задач.

Рассмотрим эти элементы подробнее.

Сегмент состояния задачи TSS

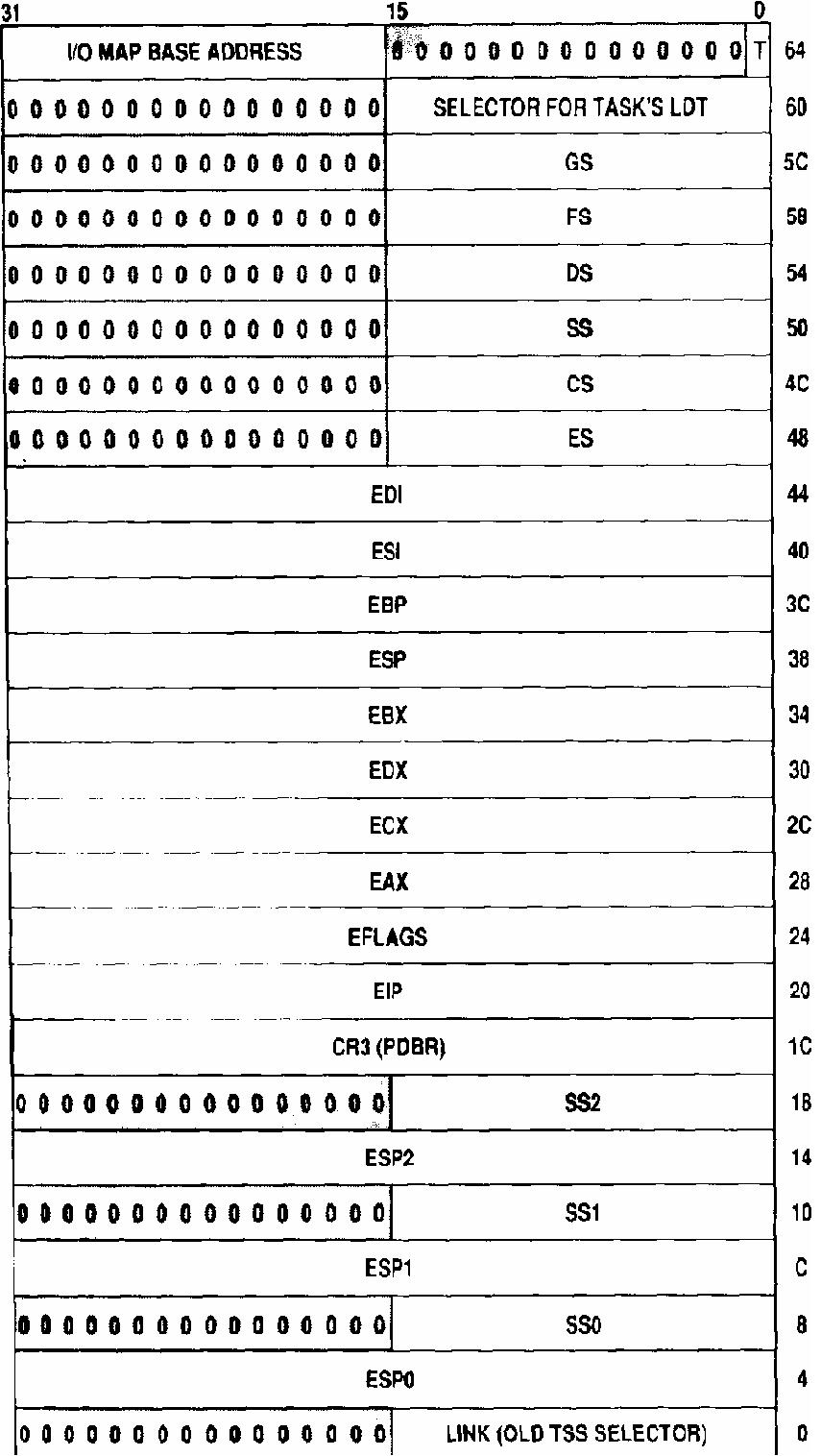

Его структура изображена на рисунке (см. рисунок ниже). Каждая задача имеет собственный TSS.

Поля TSS можно разделить на две категории:

•Динамические. Процессор обновляет их значения при каждом переключении данной задачи. В эту категорию входят следующие поля:

- регистры общего назначения EAX, ECX, EDX, EBX, ESP, EBP, ESI и EDI;

- сегментные регистры ES, CS, SS, DS, FS и GS;

- регистр флагов EFLAGS;

- счетчик команд IP;

- селектор сегмента TSS предыдущей задачи.

Формат сегмента TSS

•Статические. При переключении задачи процессор только читает, но не обновляет эти поля. Их значения устанавливаются операционной системой при создании задачи. К этим полям относятся следующие:

- Селектор локальной дескрипторной таблицы задачи (каждая задача может иметь одну собственную LDT, но может и не иметь);

- Управляющий регистр CR3 (это BDPR — регистр базового адреса таблицы каталогов страниц;

- Логические адреса стеков для уровней привилегий 0, 1 и 2;

- Значение T-бита (включения режима пошаговой отладки);

-Базовый адрес карты разрешения портов ввода/вывода и карты переназначения прерываний (необязательные элементы). Если эти элементы присутствуют, то они сохраняются в верхних адресах TSS.

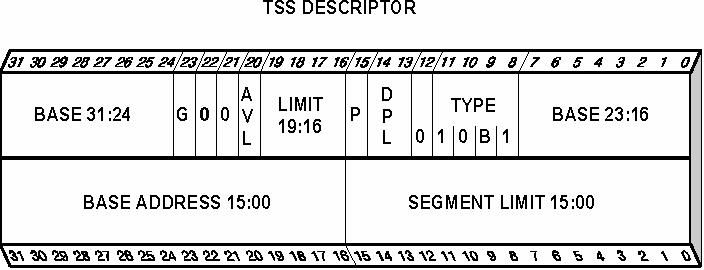

Дескриптор TSS

Сегмент состояния задачи, подобно другим сегментам, описывается дескриптором, имеющим следующий формат (см. рисунок ниже):

Формат дескриптора TSS

Рассмотрим особенности полей дескриптора. Поля базы, предела и DPL имеют то же назначение, что и для сегментов данных. Предел сегмента TSS должен быть равен или больше величины 67h (на 1 меньше минимального размера TSS — 68h). Размер TSS может быть и больше, при этом добавочное пространство может быть использовано операционной системой по своему усмотрению).

Задача не реентерабельна (т.е. не допускает рекурсивных вызовов). Для выявления попыток рекурсивного вызова служит бит занятости B (Busy Bit). Если задача была вызвана (и затем, возможно, прервана, например, вызовом друтой задачи), бит занятости устанавливается и остается установленным, что и будет признаком рекурсивного вызова при попытке вызвать эту задачу.

Переключение задачи происходит вследствие передачи управления через дескриптор TSS командами JMP или CALL, а также при прерываниях или исключениях через этот дескриптор.

Регистр задачи

Его содержимое показывает местонахождение в памяти текущего TSS. Этот регистр имеет видимую (т.е. программно доступную) часть, содержащую селектор TSS выполняемой в данный момент задачи и "теневую", которая автоматически заполняется процессором при переключении задачи и которая содержит базу и предел сегмента TSS. Селектор TSS является индексом дескриптора TSS, который может находиться только в GDT.

Привилегированные команды LTR и STR позволяют читать и писать этот регистр.

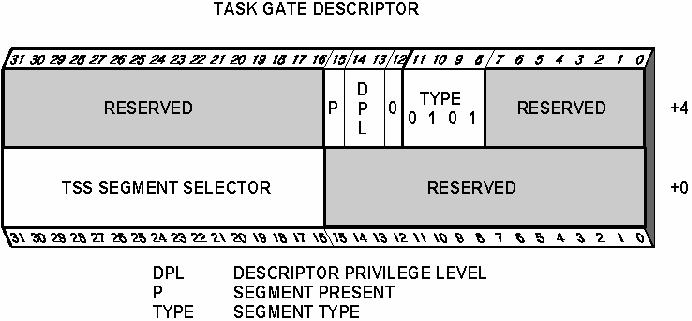

Дескриптор шлюза задачи

Дескриптор TSS обычно имеет высокий уровень привилегий, что исключает его использование "обычной" программой. Для обеспечения защищенного доступа к задаче используется шлюз задачи — дескриптор, имеющий низкий уровень привилегий, но обеспечивающий "косвенный" вызов на дескриптор TSS с высоким уровнем привилегий (см. рисунок ниже).

Формат шлюза TSS

Обратите внимание, что при использовании шлюза задачи защита анализирует DPL дескриптора шлюза, а не DPL дескриптора TSS.

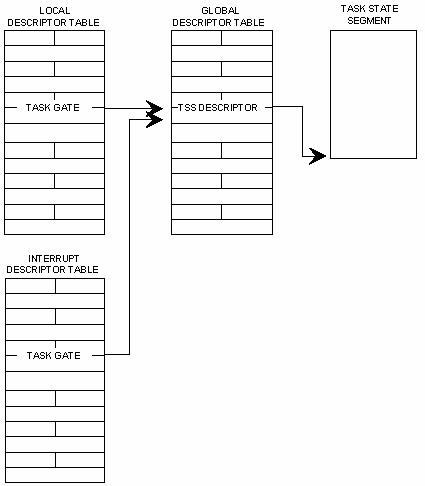

Схема переключения задачи

Рисунок ниже иллюстрирует схему переключения задачи.

Процессор передает управление другой задаче в одном из четырех случаев:

1) Текущая задача выполняет JMP или CALL на дескриптор TSS.

2) Текущая задача выполняет JMP или CALL на шлюз задачи.

3) Прерывание или исключение происходит через шлюз задачи, находящийся в IDT.

4) Текущая задача выполняет команду IRET при установленном флаге NT (в CR0).

Схема переключения задачи

Вложенные задачи

При переключении задачи в ее TSS происходит заполнение ссылки на TSS предыдущей задачи. Эта информация используется для возврата на прерванную задачу после окончания задачи, ее прервавшей. Операционная система может модифицировать эти связи, изменяя записи в TSS. Каждая задача может иметь собственную LDT и систему трансляции страниц. Регистр PDBR (Page Directory Base Register) (CR3) загружается новым значением из TSS при переключении задачи.