Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

PCI и PCI-X

Прерывания PCI: INTx#, PME#, MSI и SERR#

Сигнализация событий управления энергопотреблением — PME#

Линия PME#, введенная в PCI 2.0, служит для сигнализации в системе управления энергопотреблением PM (Power Management): смены состояния устройств, генерации пробуждения системы по событию. Эта линия электрически доступна всем устройствам PCI; как и линии INTx#, PME# никак не обрабатывается мостами, а лишь доводится до всех абонентов. Логика сигнализации аналогична INTx#: устройство сигнализирует о событии, замыкая линию PME# на «землю», таким образом, сигналы о событиях логически собираются по функции ИЛИ. Обработчик этого прерывания может выявить устройство, подавшее сигнал, путем программных обращений к конфигурационным регистрам всех устройств, способных к генерации этого сигнала. Устройства (функции), имеющие отношение к управлению энергопотреблением, имеют в конфигурационном пространстве структуру с идентификатором Capability ID = 01 и набор регистров:

- PMC (Power Management Capabilities) — регистр возможностей PM: версия спецификации, какие состояния поддерживаются, в состояниях возможна генерация PME#, нужен ли сигнал CLK для генерации PME#, каково потребление по линии 3,3VAux;

- PMCSR (Power Management Control/Status Register) — регистр управления и состояния PM: признак введения PME#, его сброс и разрешение; состояние PM, управление данными, выводимыми через регистр Data;

- Data — регистр (необязательный), через который может выводиться, например, информация о потребляемой мощности;

- PMCSR_BSE (Bridge Support Extensions) — регистр расширенного управления мостом: признак поддержки мостом управления вторичной шиной в зависимости от состояния PM; состояние вторичной шины при переходе в состояние потребления D3 (останов синхронизации или еще и снятие питания).

Подробности управления энергопотреблением в PCI и форматы соответствующих конфигурационных регистров приведены в PCI PM 1.1.

Прерывания сообщениями — MSI

На шине PCI имеется прогрессивный механизм оповещения об асинхронных событиях, основанный на передаче сообщений MSI (Message Signaled Interrupts). Здесь для сигнализации запроса прерывания устройство запрашивает управление шиной и, получив его, посылает сообщение. Сообщение выглядит как обычная запись двойного слова в ячейку памяти, адрес (32-битный или 64-битный) и шаблон сообщения на этапе конфигурирования устройств записываются в конфигурационные регистры устройства (точнее, функции). В сообщении старшие 16 бит всегда нулевые, а младшие 16 бит несут информацию об источнике прерывания. Устройство (функция) могут нуждаться в сигнализации нескольких типов запросов; в соответствии с его потребностями и своими возможностями система указывает устройству (функции), сколько различных типов запросов оно может вырабатывать.

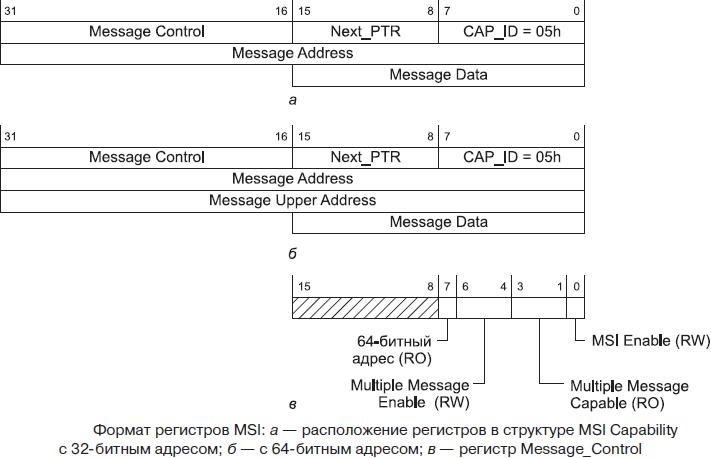

Возможность использования MSI описывается в конфигурационном пространстве структурой MSI Capability (CAP_ID = 05h), которая должна присутствовать в пространстве каждой функции, поддерживающей MSI. В структуре имеется 3 или 4 регистра (см. рисунок ниже):

- Message Address — 32-разрядный адрес памяти, по которому передается сообщение (биты [1:0] = 00). Если используется 64-битный адрес (установлен бит 7 в регистре Message Control), то его старшая часть располагается в регистре Message Upper Address. Значения в регистры адреса заносит системное ПО на этапе конфигурирования;

- Message Data — 16-битный шаблон данных, передаваемых в сообщении по линиям AD[15:0]. Значение шаблона записывается системным ПО на этапе конфигурирования. В сообщении, передаваемом функцией, для различения разных условий прерывания могут модифицироваться только несколько младших бит, количество которых определяется значением поля Multiple Message Enable. Остальные биты сообщения должны соответствовать шаблону; биты [31:16] всегда нулевые;

- Message Control — управление сообщениями (16 бит). Битом 7 функция сообщает о способности генерировать 64-битный адрес. В поле Multiple Message Capable функции задается ее способность генерировать различимые условия прерывания, в поле Multiple Message Enable система указывает функции допустимое число условий. Здесь значения 000–101 двоично кодируют число младших бит шаблона, которые устройство может модифицировать для идентификации источника прерывания: 000 — ни одного (устройству доступен лишь один идентификатор), 101 — пять, значения 110 и 111 зарезервированы. Бит MSI_Enable разрешает использование MSI.

По аппаратному сбросу MSI запрещен; его можно разрешить программно установкой бита MSI Enable (после программирования адреса и шаблона сообщения), и тогда генерация прерываний по линиям INTx# запрещается. Самая «богатая» прерываниями функция (для которой Multiple Message Enable = 101) при записи сообщения идентифицирует конкретное условие прерывания (одно из 32 возможных) по линиям AD[4:0].

Отметим, что быстрая посылка подряд двух и более одинаковых сообщений может быть воспринята системой как одно прерывание (из-за низкой реактивности). Если требуется обработка каждого из них, обработчик должен обеспечивать уведомление устройства, а оно не должно посылать следующее сообщение до получения уведомления, чтобы прерывания не терялись. Различающиеся сообщения друг другу не мешают.

Прерывания через MSI позволяют избежать бед разделяемости, обусловленной дефицитом линий запросов прерывания в PC. Кроме того, они решают проблему целостности данных: все данные, записываемые устройством до посылки MSI, дойдут до получателя гарантированно раньше начала обработки MSI. Прерывания через MSI от одних устройств в одной системе могут использоваться наряду с обычными INTx# от других устройств. Но каждое устройство (функция), использующее MSI, не должно использовать прерывания через линии INTx#.

Механизм MSI может использоваться на системных платах, имеющих «продвинутый» контроллер прерываний APIC. Правда, конкретная реализация поддержки MSI может потенциальные возможности облегчения идентификации большого числа запросов прерывания свести лишь к увеличению числа доступных запросов прерываний (и используемых ими векторов). Так, например, для системных плат на чипсетах с хабом ICH2 и ICH3 фирмы Intel поддержка MSI сводится к организации альтернативных путей подачи запросов IRQ[1:23] на входы APIC (запросы IRQ с номерами 0, 2, 8 и 13 через MSI не передаются). Всем устройствам PCI назначается один и тот же адрес сообщений (Message Address = FEC00020h), по которому в APIC находится регистр IRQ Pin assertion. В сообщении используются лишь младшие 5 бит, в которых указывается номер взводимого запроса прерывания в диапазоне 1–23 (исключая 2, 8 и 13). Линии запросов, используемые в MSI, программируются на чувствительность к перепаду (сообщения имитируют только фронт сигнала). По этой причине прерывания с номерами, используемыми в MSI, не могут использоваться совместно (разделяемо) с прерываниями, полученными другими способами (по линиям запросов от устройств PCI и от других устройств системной платы). Возможно, что в других платформах прерывания через MSI используются более эффективно.