Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

Шина IEEE 1394 — FireWire

Шина IEEE 1394 — FireWire

Организация изохронных соединений

- Подробности

- Родительская категория: Шина IEEE 1394 — FireWire

- Категория: Передача данных по шине IEEE 1394

Для установления логических связей между источниками и приемниками изохронных потоков служат регистры управления входными и выходными штекерами — PCR (Plug Control Register), описанные ниже. Штекер (Plug) в 1394 — это метафора разъема, по которому передавался бы аудио- или видеосигнал в аналоговой системе. В 1394 штекеры, которыми соединяются между собой источники и приемники изохронных данных, отображаются регистрами PCR. Эти регистры используются для организации двухточечных и широковещательных соединений.

Для изохронных передач могут быть установлены соединения одного из трех основных типов:

- точка-точка (point-to-point) — соединение, явно видимое в PCR-регистрах участников: один из регистров OUTPUT_PLUG передающего узла и один из регистров INPUT_PLUG принимающего узла содержат одинаковый номер канала channel и у обоих ненулевые значения поля point_to_point;

- широковещательная передача (broadcast out), ведущаяся без каких-либо признаков «слушателей». В регистре OUTPUT_PLUG передающего узла устанавливается бит b — признак широковещания и указывается номер канала channel;

- широковещательный прием (broadcast in), ведущийся без индикации присутствия передатчика. В регистре INPUT_PLUG передающего узла устанавливается бит b — признак широковещания и указывается номер канала channel.

Для каждого штекера может быть установлено несколько соединений точка-точка (или ни одного); широковещательное соединение может быть только одно (или ни одного). Эти типы соединений могут независимо сосуществовать на одном штекере. Установление нового двухточечного соединения увеличивает значение поля point_to_point, разрыв соединения — уменьшает (в пределе до нуля). Глава 18. Передача данных по шине IEEE 1394 Номер канала при установлении широковещательной передачи для штекера, не имеющего двухточечного соединения, определяется номером штекера и базовым адресом для данного узла (полем broadcast_base регистра OUTPUT_MASTER_PLUG).

Если broadcast_base ≠ 63, то номер канала будет суммой (по модулю 64) базового адреса и номера штекера, иначе устанавливается номер канала 63.

Приемник и передатчик изохронных данных могут соединяться двояко, различия касаются прав на разрыв соединения:

- двухточечным соединением, установленным в каждом из них. Это соединение может разорвать только тот, кто его устанавливал;

- установлением широковещательной передачи в одном узле и широковещательного приема в другом. Это соединение может разорвать любой из участников.

Интерфейс для кросс-шины (Backplane)

- Подробности

- Родительская категория: Шина IEEE 1394 — FireWire

- Категория: Физический уровень шины IEEE 1394

Физический интерфейс для использования в кросс-шине имеет ряд особенностей, отличающих его от кабельного варианта. Эти особенности касаются только PHY-уровня; на работе LINK-уровня и вышестоящих они не сказываются. Интерфейс отличается следующими моментами.

Вместо двух дифференциальных пар (TPA и TPB), соединяющих порты узлов попарно, используются два сигнальных провода STRB и DATA, к которым подключены все соединяемые порты 1394 на шасси. Уровни сигналов на этих линиях стандартом не оговариваются. Для работы шины существенно лишь, чтобы в случае столкновения передач логического «0» и «1» состояние линии воспринималось бы всеми узлами как «1». То есть шина должна обеспечивать логическую функцию «Проводное ИЛИ». В случае ТТЛ-интерфейса шины логической единице соответствует низкий уровень напряжения и передатчиками являются элементы с открытым коллектором. Приемопередатчики узлов должны быть способными одновременно и передавать, и принимать сигнал.

Здесь также используется DS-кодирование, но с более низкими скоростями: формальной скорости S100 соответствует скорость около 50 Мбит/с, S200 — 100 Мбит/с.

Механизм арбитража для такой физической шины изменен. Для получения доступа к шине устройство должно послать 10-битную последовательность арбитража. Последовательность арбитража передается с использованием DS-кодирования, причем всегда на низкой скорости (49,152 Мбит/с). Последовательность начинается с 4-битного кода приоритета, за которым следует 6-битный арбитражный номер узла (его PHY_ID). Посылая эту последовательность, узел следит за состоянием линии (принимает эту последовательность). Как только узел видит, что очередной принимаемый бит отличается от передаваемого, он понимает, что арбитраж в данной попытке проигран. Последовательность арбитража узел имеет право посылать, только дождавшись покоя шины. При этом последовательность одновременно могут начать посылать несколько узлов. Выиграет арбитраж тот узел, который посылает последовательность с самым большим значением кода приоритета, а из узлов с одинаковым приоритетом — тот, у которого самый большой номер. Исходя из этого код приоритета 0000 используется для запроса справедливого арбитража, код 1111 — для запроса передачи пакета мастером циклов.

Межпакетные зазоры в кросс-шине значительно сокращены; здесь они определяются в арбитражных тактах (частоты 49,152 МГц):

- зазор пакета подтверждения Acknowledge Gap — 4 такта на обнаружение (около 183 нс), на шину пакет подтверждения выдается после 8 тактов покоя;

- зазор между субакциями (Subaction Gap) — 16 тактов на обнаружение, пакет передается после 20 тактов покоя (около 410 нс);

- зазор сброса арбитража (Arbitration Reset Gap) — 28 тактов на обнаружение, шину можно занимать после 32 тактов покоя (около 651 нс).

Сигнал сброса по кросс-шине не передается. Подключение/отключение узлов на ходу допускается, но механизм автоконфигурирований (самоидентификации узлов) не используется — физические идентификаторы узлам назначаются какимилибо сторонними способами.

Кросс-шина 1394 используется как дополнительная шина в составе параллельных шин VME64, FutureBus, GTLP. Здесь ее роль является вспомогательной (как SMBus в PCI). Несмотря на низкую (по отношению к кабельному варианту) скорость, последовательная шина остается высокопроизводительным каналом связи, поддерживающим все передачи 1394.

Блок физических запросов

- Подробности

- Родительская категория: Шина IEEE 1394 — FireWire

- Категория: «Открытый» хост-контроллер IEEE 1394 — OHCI

Ряд запросов к памяти и регистрам узла отрабатывается на аппаратном уровне OHC, без привлечения программного обеспечения хоста. Отработкой этих запросов занимается блок физических запросов, в котором имеется контроллер DMA принимающий с шины запросы на транзакции, и контроллер DMA, посылающий на них ответы. Запросы в зависимости от смещения, указанного в адресе назначения, отрабатываются по разному.

Если смещение попадает в область нижних адресов узла, то запрос направляется к памяти хоста. При этом смещение трактуется как физический адрес памяти в пространстве хоста. В этой области физически (обменом с памятью по каналу DMA) отрабатываются запросы чтения, записи и блокированных транзакций с нулевым кодом расширенной команды, прошедшие фильтр по идентификатору источника (см. выше). Остальные запросы будут переданы в контекст AR DMA Request.

Запросы блокированных транзакций compare_swap и чтения квадлета по адресам автономных регистров диспетчера изохронных ресурсов направляются к этим регистрам. На другие запросы по этим адресам OHC отвечает квитанцией ошибки типа запроса (ack_type_error). К адресам автономных регистров относятся следующие:

- FFFFF000021Ch — регистр идентификатора диспетчера шины BusManagerID;

- FFFFF0000220h — регистр доступной полосы пропускания BandwidthAvailable;

- FFFFF0000224h — старший квадлет регистра доступных каналов, Channels-AvailableHi;

- FFFFF0000228h — младший квадлет регистра доступных каналов, Channels-AvailableLo.

Запросы чтения квадлета по специальным адресам памяти конфигурации направляются к регистрам OHC. На другие запросы по этим адресам, а также при некорректности образа памяти OHC отвечает квитанцией ошибки типа запроса ack_type_error. К специальным адресам памяти конфигурации относятся следующие:

- FFFFF0000400h — заголовок памяти конфигурации (Config ROM header), запрос направляется к регистру ConfigROMhdr;

- FFFFF0000404h — идентификатор шины, первый квадлет Bus_Info_Block, запрос направляется к регистру BusID;

- FFFFF0000408h — опции шины, второй квадлет Bus_Info_Block, запрос направляется к регистру BusOptions;

- FFFFF000040Ch и FFFFF0000410h — глобальный идентификатор, 3-й и 4-й квадлеты Bus_Info_Block, запрос направляется к регистрам GlobalIDHi и GlobalIDLo.

Запросы чтения памяти конфигурации по адресам FFFFF0000414–FFFFF00007FFh направляются к памяти хоста. Память конфигурации отображается на 1-килобайтный блок системной памяти в соответствии со значением регистра ConfigROMmap. При некорректности образа памяти (в регистре HCControl бит BIBimageValid = 0) OHC на эти запросы отвечает квитанцией ошибки ack_type_error.

Если принятый пакет запроса содержит ошибку CRC поля данных или имеет неправильную длину, контроллер ответит на него квитанцией ack_busy_* (вместо * подставляется буква A, B или X в соответствии с используемым однофазным или двухфазным протоколом). Это вынудит инициатора повторить запрос.

Генерируемые ответы на аппаратно-обрабатываемые запросы содержат метку транзакции, соответствующую запросу, и адрес назначения, соответствующий адресу источника запроса. Если на ответ контроллер получает квитанцию ack_busy, то число повторов ограничивается полем MaxPhysRespRetries регистра ATRetries.

Запросы записи могут выполняться как отправленные записи (Posted Writes) — подтверждение на них посылается сразу, не дожидаясь фактической записи. Если выполнение фактической записи не удается, то в регистре IntEvent устанавливается бит PostedWriteErr, а 48-битное смещение из адреса неудавшегося шинного запроса фиксируется в регистрах PostedWriteAddressLo, PostedWriteAddressHi (038h, 03Ch).

Запросы прерываний при нормальном выполнении аппаратно-обрабатываемых запросов не вырабатываются; прерыванием сигнализируется только ошибка при выполнении отправленной записи и невозможность доставки ответа на блокированные транзакции.

После сброса на шине все аппаратно-обрабатываемые запросы, на которые OHC должен был ответить, аннулируются. После сброса OHC автоматически начинает отрабатывать только запросы к регистрам диспетчера изохронных ресурсов (в CSR), остальные запросы будут отрабатываться только после инициализации фильтров.

Регистры управления штекерами (PCR)

- Подробности

- Родительская категория: Шина IEEE 1394 — FireWire

- Категория: Передача данных по шине IEEE 1394

Регистры управления штекерами (PCR) располагаются в адресном пространстве узлов, причастных к изохронным передачам. Они занимают место в начале пространства, отведенного под блоки узла. Регистры PCR допускают только операции чтения и блокированные операции (чтение с условной модификацией). Операции записи в эти регистры отвергаются. В состав регистров PCR входят следующие:

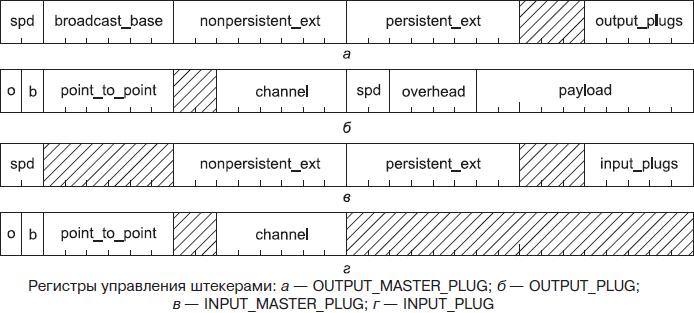

- общий регистр выходных штекеров OUTPUT_MASTER_PLUG (0900h, рис. а) определяет общие характеристики узла как изохронного передатчика. Поле output_plugs определяет количество выходных штекеров (0–31). Поле spd задает максимальную скорость передачи по любому из штекеров (0 — S100, 1 — S200, 2 — S400, 3 — S800). Поле broadcast_base задает базовый номер широковещательного канала. Поля persistent_ext, nonpersistent_ext и r зарезервированы. Этот регистр должен быть у узлов, поддерживающик как изохронную передачу, так и прием;

- регистры выходных штекеров OUTPUT_PLUG (0904–097Ch, рис. б) присутствуют только у узлов, способных вести изохронную передачу. Присутствующие регистры (их число определяется регистра OUTPUT_MASTER_PLUG) располагаются по смежным адресам. Каждый из этих регистров описывает широковещательную или двухточечную передачу потока, исходящего от узла через соответствующий штекер. Бит o (online) указывает на возможность конфигурирования и использования данного штекера для передачи (o=0 — передача невозможна). Поле channel определяет номер канала, фигурирующий в качестве адреса исходящих изохронных пакетов. Бит b (broadcast) указывает на наличие широковещательного соединения для данного штекера. Поле point_to_point определяет число двухточечных соединений, установленных для данного штекера. Поле spd задает скорость передачи пакетов (0 — S100, 1 — S200, 2 — S400, 3 — S800). Поле payload задает максимальный размер поля данных изохронного пакета в квадлетах (0 соответствует 1024 квадлетам). Поле overhead позволяет более точно вычислить запрашиваемое значение полосы пропускания bw, запрашиваемое для данного канала (значение, вычитаемое из значения регистра BANDWIDTH_AVAILABLE):

bw = overhead × 32 + (payload+3)×24–spd (при overhead ≠ 0);

Если overhead = 0, то запрашиваемая полоса определяется по формуле

bw = 512 + (payload + 3) × 24–spd.

- Общий регистр входных штекеров INPUT_MASTER_PLUG (0980h, рис. в) определяет количество входных штекеров (input_plugs в диапазоне 0–31) и максимальную поддерживаемую скорость (по любому из штекеров). Поля persistent_ext, nonpersistent_ext и r зарезервированы. Этот регистр должен быть у узлов, поддерживающих как изохронную передачу, так и прием;

- регистры входных штекеров INPUT_PLUG (0984–09FCh, рис. г) присутствуют только у узлов, способных вести изохронный прием. Присутствующие регистры (их число определяется регистром INPUT_MASTER_PLUG) располагаются по смежным адресам. Каждый из этих регистров описывает широковещательное или двухточечное соединение для соответствующего штекера. Бит o (online) указывает на возможность конфигурирования и использования данного штекера для приема (o = 0 — прием невозможен). Поле channel определяет номер принимаемого канала. Бит b (broadcast) указывает на наличие широковещательного соединения для данного штекера. Поле point_to_point определяет число двухточечных соединений, установленных для данного штекера.

Трансляция сигналов (функции повторителя)

- Подробности

- Родительская категория: Шина IEEE 1394 — FireWire

- Категория: Физический уровень шины IEEE 1394

Соединение более двух узлов в шину IEEE 1394 возможно только при использовании многопортовых узлов. Многопортовость реализуется в PHY-уровне узла, который для этого должен иметь в своем составе несколько интерфейсных портов и повторитель. Повторитель (Repeater) служит для передачи пакетов между портами и кодером-декодером своего узла:

- пакет, исходящий с другого узла и не предназначенный для данного узла, транслируется с порта, на который он пришел, во все остальные активные порты, для которых согласованная скорость достаточна для передачи данного пакета;

- пакет, исходящий с другого узла и предназначенный данному узлу, транслируется в другие порты (с учетом скорости), а также декодируется и передается LINK-уровню (если он поддерживает эту скорость);

- пакет, исходящий из данного узла, посылается во все порты (с учетом скорости).

Повторитель узла выполняет ресинхронизацию данных по своему тактовому генератору. Поскольку тактовая частота узлов не может совпадать абсолютно точно, ресинхронизация требует применения эластичного буфера (с FIFO-организацией). Принимаемая битовая последовательность помещается в буфер на частоте входного сигнала. Биты на передачу начинают выбираться из FIFO-буфера после того, как там наберется некоторое начальное количество бит. Это вводит неизбежную задержку трансляции данных повторителем. В процессе трансляции число бит в FIFO может колебаться: если частота вывода (определяется частотой данного узла) чуть ниже частоты принятого сигнала, то в буфере биты будут накапливаться. Если частота вывода выше, то буфер будет опустошаться. Переопустошение буфера, естественно, недопустимо — оно приведет к ошибке данных. Начальный порог заполнения выбирается исходя из максимально допустимого расхождения частот и максимальной длины передаваемого пакета.

Подкатегории

-

Основная информация

- Кол-во материалов:

- 8

-

Физический уровень шины IEEE 1394

- Кол-во материалов:

- 13

-

Управление шиной IEEE 1394

- Кол-во материалов:

- 9

-

Конфигурирование шины и узлов IEEE 1394

- Кол-во материалов:

- 8

-

Арбитраж и распределение времени шины IEEE 1394

- Кол-во материалов:

- 5

-

Передача данных по шине IEEE 1394

- Кол-во материалов:

- 12

-

«Открытый» хост-контроллер IEEE 1394 — OHCI

- Кол-во материалов:

- 11

-

Взаимодействие с физическим уровнем шины IEEE 1394

- Кол-во материалов:

- 7