Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

Станок пристрелочный 51 купить www.huntmania.ru. фингерпринт браузера на сайте.

USB

Хост USB

Общая информация о хосте USB

Хост является главным действующим лицом в организации конфигурирования и выполнения транзакций USB. У каждой шины USB должен быть один (и только один!) хост — компьютер с контроллером USB. Однако понятие компьютер отнюдь не означает лишь привычные варианты настольных, напольных, портативных компьютеров. Компьютер — это сочетание процессора, памяти и периферийных устройств; в таком понимании в большинстве современных устройств присутствуют встроенные компьютеры. Если «интеллекта» этого компьютера и его возможностей диалога с пользователем оказывается достаточно, то он может взять на себя роль хоста USB. Такой вариант хоста рассматривается в последнем параграфе данной главы.

«Классический» хост USB делится на три основных уровня:

- интерфейс шины USB обеспечивает физический интерфейс и протокол шины. Интерфейс шины реализуется хост-контроллером, имеющим встроенный корневой хаб, обеспечивающий точки физического подключения к шине (гнезда USB типа «A»). Хост-контроллер отвечает за генерацию микрокадров. На аппаратном уровне хост-контроллер обменивается информацией с основной памятью компьютера, используя прямое управление шиной (bus-mastering) с целью минимизации нагрузки на центральный процессор;

- система USB, используя хост-контроллер(ы), транслирует клиентское «видение» обмена данными с устройствами — запросы IRP (I/O Request Packet — пакет запроса ввода/вывода) — в транзакции, выполняемые с реальными устройствами шины. Система отвечает и за распределение ресурсов USB — полосы пропускания и мощности источников питания (для устройств, питающихся от шины). Система состоит из трех основных частей:

- драйвер хост-контроллера — HCD (Host Controller Driver) — модуль, привязанный к конкретной модели контроллера, обеспечивающий абстрагирование драйвера USB и позволяющий в одну систему включать несколько разнотипных контроллеров;

- драйвер USB — USBD (USB Driver) — обеспечивает основной интерфейс (USBDI) между клиентами и устройствами USB. Интерфейс HCDI (Host Controller Driver Interface) между USBD и HCD спецификацией USB не регламентируется. Он определяется разработчиками ОС и должен поддерживаться разработчиками хост-контроллеров, желающих иметь поддержку своих изделий конкретными ОС. Клиенты не могут пользоваться интерфейсом HCDI; для них предназначен интерфейс USBDI. USBD обеспечивает механизм обмена в виде пакетов IRP, запрашивающих транспортировку данных по заданному каналу. Кроме того, USBD отвечает за некоторое абстрактное представление устройства USB клиенту, которое позволяет выполнять конфигурирование и управление состоянием устройств (включая и стандартное управление через конечную точку «0»). Реализация интерфейса USBDI определяется операционной системой; в спецификации USB излагаются только общие идеи;

- программное обеспечение хоста реализует функции, необходимые для функционирования системы USB в целом: обнаружение подключения и отключения устройств и выполнение соответствующих действий по этим событиям (загрузки требуемых драйверов), нумерацию устройств, распределение полосы пропускания и потребляемой мощности, управление состоянием энергопотребления и т. п.

- клиенты USB — программные элементы (приложения или системные компоненты), взаимодействующие с устройствами USB. Клиенты могут взаимодействовать с любыми устройствами (наборами их доступных конечных точек, входящих в выбранные интерфейсы), подключенными к системе USB. Однако система USB изолирует клиентов от непосредственного обмена с какими-либо портами (в пространстве ввода/вывода) или ячейками памяти, представляющими интерфейсную часть контроллера USB.

В совокупности уровни хоста предоставляют следующие возможности:

- обнаружение подключения и отсоединения устройств USB;

- манипулирование потоками управления между устройствами и хостом;

- манипулирование потоками данных;

- сбор статистики активности и состояний устройств;

- управление электрическим интерфейсом между хост-контроллером и устройствами USB, включая управление электропитанием.

Программная часть хоста в полном объеме реализуется операционной системой. До загрузки ОС может функционировать лишь усеченная часть ПО USB, поддерживающая только устройства, требующиеся для загрузки. Так, в BIOS современных системных плат имеется поддержка клавиатуры USB, реализующая функции сервиса Int 9h. После загрузки системы USB эта «дозагрузочная» поддержка игнорируется — система начинает работу с контроллером «с чистого листа», то есть со сброса и определения всех подключенных устройств. В спецификации PC’2001 выдвигается ряд требований к BIOS, в частности требование поддержки загрузки ОС с устройств USB.

Хост-контроллер

Хост-контроллер является аппаратным посредником между устройствами USB и хостом. В настоящее время имеется три спецификации хост-контроллеров, каждой из которых соответствует свой комплект драйверов хост-части:

- UHC (Universal Host Controller) — универсальный хост-контроллер для шины USB 1.x, разработанный Intel;

- OHC (Open Host Controller) — «открытый» хост-контроллер для шины USB 1.x, разработанный Compaq, Microsoft и National Semiconductor;

- EHC (Enhanced Host Controller) — расширенный хост-контроллер для поддержки высокой скорости шины USB 2.0.

Все эти варианты контроллеров выполняют одни и те же задачи: организуют физические транзакции с устройствами по шине USB в соответствии с описаниями (дескрипторами) этих транзакций, помещенными в системное ОЗУ драйвером хост-контроллера. При этом транзакции разных типов обрабатываются по-разному. В плане обработки ошибок проще всего устроены изохронные транзакции, где ошибки не требуют повторов. Транзакции передач с гарантированной доставкой в случае ошибок требуют повторов до победного конца или признания неудачи (исчерпания допустимого числа повторов). С точки зрения планирования следует выделить периодические транзакции, которые должны выполняться строго по графику, остальные — как получится, и их ставят в очереди. Из-за особенностей планирования и возможных повторов порядок завершения обработки дескрипторов транзакций (успешных или нет) будет отличаться от порядка их помещения в память1, что прибавляет забот хост-контроллеру и его драйверу. Три варианта хостконтроллеров решают эти задачи по-разному и используют разные стратегии планирования транзакций, что иллюстрирует таблицы ниже.

План распределения времени в кa)адре: a — UHC; б — OHC; в — EHC (в микрокадре)

а)

| SOF | Изохронные транзакции | Транзакции прерываний | Транзакции управления | Транзакции передач массивов | Свободное время |

б)

| SOF | Непереодические транзакции (Т1) | Переодические транзакции | Непереодические транзакци |

В)

| SOF | Непереодические транзакци | Переодические транзакции |

«Универсальный» хост-контроллер — UHC

Хост-контроллер UHC от Intel появился в микросхеме PIIX3 (мост PCI-ISA) чипсетов системных плат для процессоров Pentium и используется во многих последующих изделиях Intel. Это FS/LS хост-контроллер, который большую часть забот по планированию транзакций перекладывает на ПО, — драйвер контроллера UHC (UHCD). Интерфейс контроллера UHC описан в документе Universal Host Controller Interface (UHCI) Design Guide, версия 1.1 вышла в 1996 году.

Драйвер UHC формирует для хост-контроллера дескрипторы, называемые в UHCI «дескрипторами передач» (TD — Transfer Descriptor), на самом деле описывающие каждую шинную транзакцию. Напомним, что в терминах спецификации USB одна передача (transfer) может состоять из нескольких транзакций, а в управляющих передачах используется еще и свой тип транзакции для каждой фазы. Для транзакций передач с гарантированной доставкой дескрипторы TD приходится организовывать в очереди. Очереди нужны для таких передач, поскольку заранее не известно, сколько раз придется пытаться их исполнить. Продвижение очереди возможно только по успешному выполнению транзакции, находящейся в голове очереди, — это правило обеспечивает гарантированный порядок (в пределах своей очереди) доставки пакетов. Каждая очередь имеет свой заголовок (QH). Изохронные передачи исполняются всегда однократно (здесь нет гарантированной доставки), что упрощает их планирование. Драйвер размещает дескрипторы TD и QH в памяти и связывает их между собой в соответствии с планом выполнения транзакций в каждом кадре. Драйверу UHC приходится составлять детальное «расписание» для каждого будущего кадра, для чего используется список Frame List на 1024 кадра. Хост-контроллер обходит списки дескрипторов, начиная с точки, на которую указывает Frame List для текущего кадра, и выполняет соответствующие транзакции. Результат исполнения транзакции помечается в ее дескрипторе, отработанная транзакция помечается как «неактивная», и контроллер, встретив ее при очередном обходе, просто переходит к следующей. Драйвер должен периодически просматривать дескрипторы, извлекая уже отработанные и передавая результаты выполнения клиентскому драйверу. Логика работы контроллера подразумевает, что одному запросу ввода/вывода (IRP) от клиентского драйвера может соответствовать несколько «передач» — элементов очереди. Драйвер UHC разбивает запрос на транзакции и помещает дескрипторы этих транзакций в соответствующую очередь, а очередь включает в ближайшие планы. Драйвер отвечает за балансировку загрузки шины в каждом кадре, в частности, за гарантию предоставления не менее 10% полосы для транзакций управляющих передач. Планированием кадров также обеспечивается требуемая частота обращений к точкам периодических передач.

Контроллер UHC является активным устройством PCI (Bus-Master). Основное взаимодействие драйвера с хост-контроллером происходит с помощью дескрипторов, расположенных в памяти. Контроллер имеет регистры (в пространстве ввода/вывода), с помощью которых можно управлять его поведением: выполнять сброс, глобальную приостановку и пробуждение, подстраивать частоту кадров, управлять запросами прерываний, управлять портами встроенного корневого хаба. Контроллер позволяет работать в отладочном режиме, останавливаясь после выполнения каждой транзакции.

В процессе отработки плана контроллер считывает из памяти дескрипторы и данные, необходимые для начала транзакции. Как только в FIFO-буфер контроллера из памяти поступает информация, достаточная для начала транзакции, контроллер начинает транзакцию на шине USB. В процессе ее исполнения производится передача данных, после завершения контроллер модифицирует дескрипторы в памяти в соответствии с условиями завершения транзакции. В процессе отработки транзакции могут возникать ошибки переполнения или переопустошения FIFO-буфера, связанные с перегрузкой контроллера системной памяти или шины PCI. Эти серьезные ошибки инициируют аппаратные прерывания. В состав хостконтроллера входит и корневой хаб на 2 или более порта.

Прерывания от UHC могут инициироваться различными событиями, такими как выполнение транзакций (избранных), обнаружение приема короткого пакета, прием сигнала возобновления, или в результате ошибки. Прерываний по подключению-отключению устройств контроллер не вырабатывает.

В контроллере UHC имеется специальная поддержка традиционного интерфейса клавиатуры и мыши через контроллер 8042 — перехват обращений к портам 60h и 64h пространства ввода/вывода. При разрешенной эмуляции по обращениям ПО к этим портам UHC вызывает системное прерывание SMI (System Management Interrupt), обрабатывающееся в ПК на процессорах x86 в режиме SMM (System Management Mode), невидимо для обычных программ. Обработчик SMI, перехватывающий эти обращения, формирует последовательности действий, необходимые для их исполнения с помощью клавиатуры и (или) мыши USB. Единственное исключение делается при перехвате команд, управляющих вентилем GateA20, — вместо генерации SMI манипуляции этим вентилем выполняются аппаратно (как это давно делается и в 8042). Эта аппаратная поддержка включается установкой соответствующих параметров CMOS Setup.

Большое неудобство работы с UHC возникает из-за необходимости программного просмотра всех дескрипторов передач на предмет выявления завершенных. Дескрипторы завершенных передач необходимо программно извлекать из цепочек, сохраняя связанность элементов. Планирование транзакций (составление списков дескрипторов и заголовков) — тоже достаточно трудоемкая задача для драйвера. Очевидно, преследовалась цель упрощения аппаратных средств хост-контроллера. Однако это может обернуться зависимостью эффективной производительности шины USB от мощности и загрузки центрального процессора. Такой подход к организации ввода/вывода трудно назвать эффективным.

Структуры данных и регистры контроллера UHC

Драйвер в системной памяти создает список кадров Frame List, состоящий из 1024 элементов. Каждый элемент этого списка содержит 32-битный указатель на связанный список структур данных, по которым контроллер выполняет транзакции в данном кадре. Хост-контроллер имеет регистр базового адреса списка кадров, указывающий на начало списка. Текущий номер отрабатываемого элемента определяется десятью младшими битами счетчика кадров, находящегося в контроллере и инкрементируемого каждую миллисекунду. Период счета кадров можно немного варьировать, изменяя константу, занесенную в регистр модификации длительности кадра (SOF Modify Register), что обеспечивает возможность подстройки частоты кадров для синхронизации изохронных обменов.

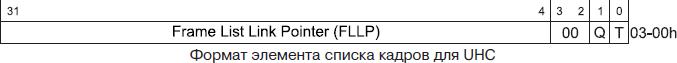

Элемент списка кадров может указывать либо на дескриптор изохронной передачи TD (Transfer Descriptor), либо (если в данном кадре изохронный обмен не планируется) на заголовок очереди QH (Queue Head). Если в данном кадре вообще не планируются передачи, то в элементе устанавливается признак-«заглушка» T (Terminate, конец связанного списка, в данном случае — пустого). Еще раз напомним, что здесь слово «передача» (Transfer, согласно спецификации UHCI) употребляется в узком смысле — она соответствует одной транзакции (передаче не более одного пакета данных). Элемент (32-битное слово) имеет формат, приведенный на рисунке ниже. Поле FLLP (Frame List Link Pointer) — указатель на элемент; бит T — признак последнего элемента (при T = 1 указатель FLLP недействителен). Бит Q задает класс связанного элемента, на который указывает FLLP (0 — TD, 1 — QH).

Для каждого кадра из списка устанавливается своя цепочка дескрипторов изохронных передач (возможно и пустая), последний из этой цепочки должен ссылаться на цепочку заголовков очередей. Цепочки заголовков QH могут быть общими для группы кадров или даже для всех кадров списка. Общая идея построения очередей состоит в том, чтобы создавать свою очередь для каждого установленного канала (для всех сконфигурированных точек, кроме изохронных). «Дежурный» метод обслуживания — по горизонтали, тогда после выполнения транзакции с одной точкой контроллер перейдет к другой точке (другой очереди). Связывание TD и QH через указатели позволяет формировать произвольные конфигурации переходов от одной очереди к другой и даже делать петли — в последнем случае возможно, что с одной точкой в кадре успеют пройти несколько транзакций. Однако это нетипичный способ планирования. Если очередей много (установлено много каналов), то они распределяются по кадрам (из 1024-элементного списка) так, чтобы цепочка каждого кадра обязательно прошла по горизонтали до конца. Это можно спланировать, поскольку максимальное время для отработки одного элемента каждой очереди (как и изохронных транзакций) заранее известно (оно определяется типом передачи, максимальным размером пакета и скоростью устройства, что известно системе USB). При необходимости «горизонтальную справедливость» можно нарушить, задав вертикальный порядок обслуживания, — контроллер, успешно обработав из очереди передачу с признаком V = 1, перейдет к следующему дескриптору из этой же очереди, а не к следующей очереди.

Дескрипторы передач и заголовки очередей размещаются драйвером в ОЗУ по адресам, выровненным по границе параграфа, поскольку в качестве указателей используются лишь старшие 28 бит (биты [3:0] используются для служебных признаков).

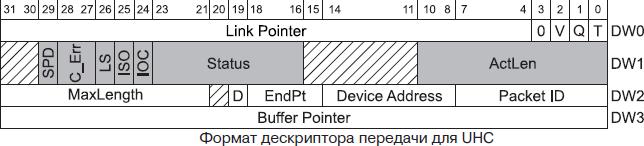

Дескриптор передачи (TD) состоит из 32 байтов, из которых хост-контроллер использует только первые четыре 32-битных слова DW0–DW3. Слова DW4–DW7 зарезервированы для использования драйвером UHC (для организации «сборки мусора» — повторного использования отработанных областей). Формат дескриптора передачи приведен на рисунке ниже. Серым цветом выделены поля, модифицируемые хост-контроллером.

В слове DW0 поле Link Pointer аналогично полю FLLP, а биты T и Q аналогичны одноименным битам элемента списка кадров. Бит V — метод обслуживания TD (1 — в глубину, 0 — в ширину).

Слово DW1 используется для управления и определения состояния выполнения передачи, модифицируется хост-контроллером. Поле ActLen — действительная длина переданных данных; поле Status — состояние выполнения передачи:

длина переданных данных; поле Status — состояние выполнения передачи:

- бит 23: Active — «надо исполнять», устанавливается драйвером, сбрасывается контроллером по успешному исполнению или исчерпанию лимита повторов;

- бит 22: Stalled — точка ответила пакетом STALL;

- бит 21: Data Buffer Error — ошибка буфера данных (переполнение или переопустошение FIFO при выполнении транзакции), транзакция остается активной (при переопустрошении контроллер генерирует пакет с ошибочным CRC, при переполнении не отвечает подтверждением);

- бит 20: Babble — при выполнении данной транзакции обнаружена «болтливость» устройства (оно отключается и устанавливается бит Stalled);

- бит 19: NAK — получение соответствующего ответа (в транзакции SETUP получение NAK устанавливает и признак ошибки тайм-аута);

- бит 18: CRC/Time Out Error — обнаружена ошибка передачи (CRC или таймаут);

- бит 17: Bitstuff Error — обнаружена ошибка вставки бит.

Биты [24:31] используются для управления передачей. Бит IOC заказывает прерывание по исполнению (прерывание генерируется в конце кадра, даже если транзакция уже неактивна, выборка ее дескриптора вызовет прерывание). Бит ISO — признак изохронной передачи (указание не делать повторных попыток). Бит LS — признак LS-устройства, использовать преамбулу перед передачей. Поле C_ERR — счетчик повторных попыток, декрементируемый по каждой ошибке. Переход в 1 или 0 вызывает перевод дескриптора в неактивное состояние. Если драйвер устанавливает нулевое значение, то число повторов неограниченно. Бит SPD — детектор короткого пакета: если в транзакции IN, стоящей в очереди, успешно принято меньше данных, чем ожидалось, то в конце кадра вырабатывается условие прерывания.

В слове DW2 содержится информация для выполнения транзакции: Packet ID — тип используемого маркера IN (69h), OUT (E1h) или SETUP (2Dh); Device Address— адрес устройства USB; EndPt — номер и направление конечной точки. Бит D (Data Toggle) — состояние переключателя для передаваемого или посылаемого пакета. Поле MaxLength — длина передаваемых данных (максимальная длина принимаемых), 000 — 1 байт, 001 — 2, 3FF — 1024; 7FFh — 0 (пустой пакет). Допустимые значения до 4FFh — 1280 байт, теоретический предел емкости кадра. Значения 500–7FEh недопустимы, вызывают фатальную ошибку контроллера.

В слове DW3 содержится Buffer Pointer — указатель на буфер в ОЗУ, используемый для данных этой передачи.

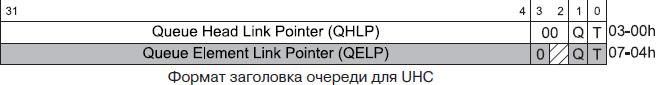

Заголовок очереди (QH) связывает очереди друг с другом (по горизонтали) и ссылается на первый элемент (TD) данной очереди. Хост-контроллер использует два 32-битных слова (см. следующий рисунок). В поле QHLP (Queue Head Link Pointer) содержится указатель на следующий заголовок очереди (горизонтальная связка). В поле QELP (Queue Element Link Pointer) содержится указатель на элемент очереди (вертикальная связка). Признаки последнего элемента (T) и класс связанного элемента (Q) аналогичны одноименным признакам и классам в вышеприведенных структурах.

Дескриптор заголовка очереди создается драйвером; хост-контроллер модифицирует в памяти указатель QELP: успешно отработав транзакцию, контроллер берет из DW0 ее дескриптора указатель на следующий элемент и помещает его на место QELP в заголовке очереди. Таким образом, успешно отработанный TD удаляется из очереди. Когда удаляется последний TD, в QELP устанавливается признак пустой очереди (T). В случае неисправимой ошибки при отработке какого-то дескриптора в QELP также устанавливается «заглушка» T — поток с гарантированной доставкой не позволяет пропустить какую-либо транзакцию. Поле QELP может ссылаться как на TD (тривиальный вариант планирования), так и на QH — очередь сама может содержать очереди.

Регистровая модель UHC поясняется в таблице ниже, где представлены регистры, отображенные на пространство ввода/вывода. Кроме того, как всякое устройство PCI, контроллер UHC имеет регистры в конфигурационном пространстве, в которых, в частности, задаются коды класса (0Ch — контроллер последовательной шины), подкласса (03 — USB) и программного интерфейса (00) в классификации PCI SIG.

Таблица. Регистры контроллера UHC

| Адрес | Назначение |

| Base + (00–01h) |

USBCMD — регистр команд USB Биты 15:8 — резерв Бит 6: CF (Configure Flag) — флаг, которым драйвер отмечает окончание процесса |

| Base + (02–03h) |

USBSTS — регистр состояния USB Биты [15:6] — резерв |

| Base + (04–05h) |

USBINTR — регистр разрешения прерываний Биты [15:4] — резерв |

| Base + (06–07h) | FRNUM — регистр номера кадра |

| Base + (08–0Bh) | FRBASEADD — регистр базового адреса списка кадров |

| Base + 0Ch |

SOFMOD — регистр управления частотой кадров Биты [6:0] — управление длительностью кадра: 0 — 11936 бит, 1 — 11937 бит, … |

| Base + (10–11h) |

PORTSC1 — регистр управления и состояния порта 1 Биты [15:13] — резерв (0) Бит 8: (RO) Low Speed Device Attached — признак подключения LS-устройства |

| Base + (12–13h) | PORTSC2 — регистр управления и состояния порта 2 (аналогично предыдущему) |

«Открытый» хост-контроллер — OHC

Спецификация интерфейса «открытого» хост-контроллера OpenHCI (OHCI) разработана компаниями Compaq, Microsoft и National Semiconductor и описана в документе «Open Host Controller Interface Specification for USB». Версия 1.0a этого документа опубликована в 1999 году. Контроллер OHC, как и UHC, предназначен для поддержки скоростей FS/LS. Однако аппаратные средства OHC берут на себя большую часть забот планирования, разгружая ЦП от рутины постоянной обработки дескрипторов. Контроллер OHC оперирует дескрипторами конечных точек и дескрипторами передач.

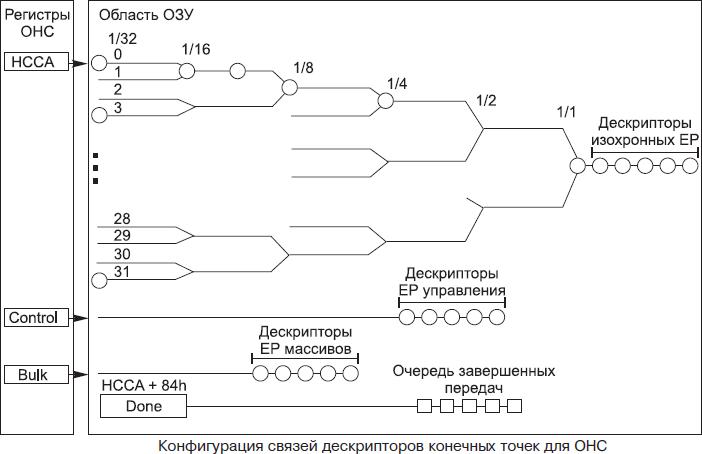

Дескрипторы конечных точек ED (Endpoint Descriptor) создаются для всех сконфигурированных конечных точек всех подключенных устройств. Эти дескрипторы размещаются в памяти и связываются между собой; конфигурация связей задает порядок их обслуживания хост-контроллером. Дескриптор конечной точки описывает ее полный адрес и направление, тип, допустимый размер пакета, скорость, состояние точки и дескриптора, указатели на очереди передач, связанных с данной точкой, указатель на дескриптор следующей точки. Для всех точек управления (Control) и всех точек передач массивов (Bulk) создаются отдельные цепочки ED, на начала этих цепочек указывают специальные регистры OHC. Дескрипторы точек периодических передач организуются в «поваленное» двоичное дерево (см. рисунок ниже), в «ветвях» которого размещаются дескрипторы точек прерываний, а в «стволе» — дескрипторы точек прерываний с минимальным интервалом обслуживания и все дескрипторы точек изохронных передач. У дерева имеются 32 конечных ветви, проход по дереву осуществляется от конечных ветвей к стволу. В каждом из 32 смежных кадров вход осуществляется со своей ветви. Для этого в OHC имеется регистр базового адреса HCCA (Host Controller Communication Area, область коммуникаций хост-контроллера), указывающий на ветвь с номером 0, и счетчик кадров, 5 младших бит которого задают номер ветви входа для очередного кадра. Таким образом, через каждую ветвь пятого уровня (конечного) обработчик дескрипторов проходит 1 раз за 32 кадра (T = 32 мс), четвертого — 1 раз за 16 кадров (T = 16 мс), для третьего уровня — T = 8 мс, для второго — T = 4 мс, для первого — T = 2 мс, для нулевого (ствола) — T = 1 мс.

Дескрипторы передач TD (Transfer Descriptor), в отличие от TD UHC, для OHC действительно описывают передачи USB. Каждая передача может разбиваться на несколько транзакций, и это разбиение выполняет хост-контроллер исходя из размера пакета, установленного в дескрипторе конечной точки. Буфер данных для передачи может располагаться в одной или двух физических страницах памяти, возможно, разрозненных. В виртуальном пространстве логических адресов буфер должен быть непрерывной областью. Размер передачи может достигать 8 Кбайт, но если буфер начинается не с начала страницы, то допустимый размер передачи сократится (в худшем случае до 4097 байт). Дескрипторы передач собираются в очереди, которые прикрепляются к дескрипторам конечных точек.

Хост-контроллер OHC имеет таймеры, с помощью которых он осуществляет планирование транзакций в кадре. После SOF контроллер начинает обход цепочки ED для управляющих передач и выполняет столько из них, сколько успеет за время T1. Далее он начинает обход дерева периодических передач, от n-й конечной ветви до ствола, пока не пройдет по всем встретившимся ED. Если у него еще остается время в кадре, он снова берется за непериодические передачи (Bulk и Control). Отработанные (успешно или снятые по превышению порога ошибок) дескрипторы контроллер собирает в специальную очередь обработанных дескрипторов Done Queue, откуда их без труда извлекает драйвер. Контроллер может вырабатывать прерывания по завершению обработки TD, причем с заданной (для каждого TD) задержкой (или не вырабатывать запрос). Контроллер OHC имеет регистр для подстройки частоты кадров. В контроллер входит и корневой хаб на 2 или более порта.

Контроллер OHC, как и UHC, обычно является активным устройством PCI (Bus Master), но по сравнению с UHC наделен большим интеллектом. В контроллере предусмотрена поддержка контроллера клавиатуры и мыши (KBC) с помощью прерываний SMI, но, в отличие от UHC, в OHC имеются и специальные регистры, упрощающие задачу эмуляции.