Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

подготовка документации по охране труда. Инструментальный шкаф.

Память. Верхний уровень

Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Подробности

- Родительская категория: Память. Верхний уровень

- Категория: Трансляция адреса в защищенном режиме в проц-х x86

Страничный механизм в процессорах 386+

Для реализации виртуальной памяти очень желательно, чтобы заменяемые блоки имели одинаковый размер и были в памяти выровнены (т.е. лежали с адресов, кратных этому размеру) — это позволит избежать фрагментации памяти при свопинге. Такой механизм имеется в процессорах i386+.

Если включен страничный механизм, то все физическое адресное пространство разбивается на блоки одинакового размера — страницы. В процессорах семейства х86 страницы могут иметь размер 4 кбайт либо 4Мбайт. Существующие операционные системы используют в основном маленькие 4 К-байтные страницы. Дальнейшее рассмотрение идет применительно именно к этому варианту.

Механизм трансляции страниц

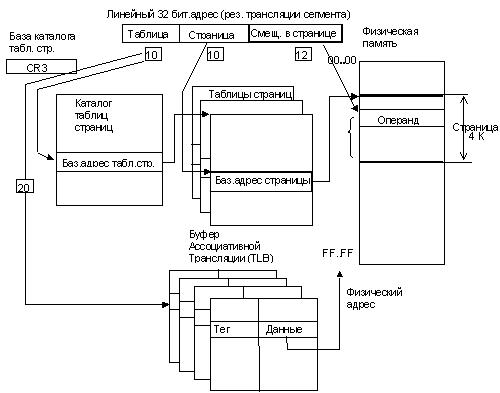

Линейный адрес (результат трансляции сегмента) интерпретируется процессором как состоящий из трех частей. Младшие 12 разрядов адреса определяют относительный адрес внутри страницы.

Старшие 20 разрядов линейного адреса (индекс страницы) задают одну из 220 страниц. Это делается с помощью двухступенчатого табличного преобразования. Старшие 20 разрядов линейного адреса интерпретируются как два 10-битовых поля. Разряды 12…20 задают номер дескриптора страницы (Page Table Entry) в таблице страниц (Page Table — см. рисунок ниже).

Страничный механизм трансляции адреса

Дескриптор страницы имеет длину 4 байта. Одна таблица содержит 1024 дескриптора.

Старшие 20 разрядов дескриптора страницы содержат ее базовый адрес. Процессор формирует физический адрес операнда с помощью конкатенации базового адреса (из дескриптора) и внутристраничного смещения (младшая часть линейного адреса).

Табличное преобразование адреса при включенном страничном механизме выполняется один или несколько раз при выполнении каждой команды. Для того, чтобы страничная трансляция присходила быстро, для хранения индексов недавно использовавшихся страниц и их базовых адресов используется небольшая память с ассоциативным доступом — Буфер Ассоциативной Трансляции (Translation LookAside Buffer, TLB), которая обычно выполняется как полностью ассоциативная (Fully Assocciative).

Таблица страниц сама представляет собой 4 Кбайт-страницу. Одна программа использует много страниц (иногда больше, чем 1024), т.е. ей может требоваться больше, чем одна таблица страниц. В схеме трансляции страниц может одновременно использоваться до 1024 таблиц страниц. Каждая таблица страниц (поскольку тоже является страницей) в свою очередь описывается дескриптором в еще одной таблице — в каталоге таблиц страниц (Page Directory).

Старшие десять битов линейного адреса задают индекс дескриптора в каталоге таблиц страниц, т.е. используемую при данном обращении таблицу страниц.

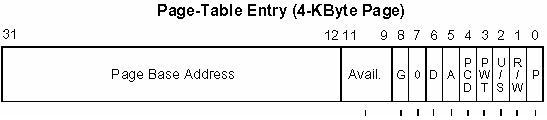

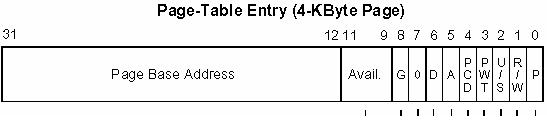

Теперь рассмотрим структуру дескриптора страницы более подробно.

Дескрипторы страниц (любые), кроме базового адреса, содержат еще набор битовых полей, облегчающих реализацию виртуальной памяти и защиты (см. рисунки ниже):

P — бит присутствия страницы в памяти;

R/W — бит разрешения записи на данную страницу — позволяет ограничить доступ к отдельным диапазонам адресов;

U/S — бит уровня привилегий — пользовательская/системная страница;

PWT — алгоритм работы данной страницы с КЭШ-памятью — разрешение "сквозной" записи (Write-Throuhg);

PCD — бит запрета кэширования страницы (Page Cache Disabled);

A — признак того, что к элементам страницы производился доступ (Accessed);

D — признак того, что на страницу производиласть запись (флаг модификации — Dirty);

G — признак "глобальной" (Global) страницы, используется для страниц, постоянно находящихся в памяти (например, чдля ядра операционной системы. Этот признак запрещает удалять дескриптор такой страницы из Буфера Ассоциативной Трансляции.

Структура дескриптора страницы