Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

Ввод-вывод

Ввод-вывод

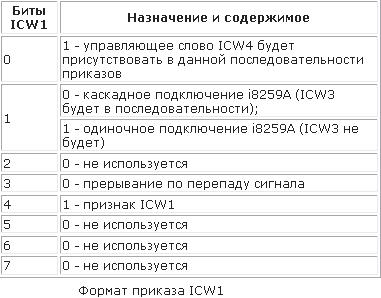

Первое.ICW1 — определить особенности последовательности приказов

- Подробности

- Родительская категория: Ввод-вывод

- Категория: Программирование контроллера прерываний i8259А

Состояние битов этого приказа (табл ниже) определяет особенности в последовательности приказов при инициализации контроллера. Данный приказ посылается в порт 20h.

Программирование

- Подробности

- Родительская категория: Ввод-вывод

- Категория: Прямой доступ к памяти (ПДП)

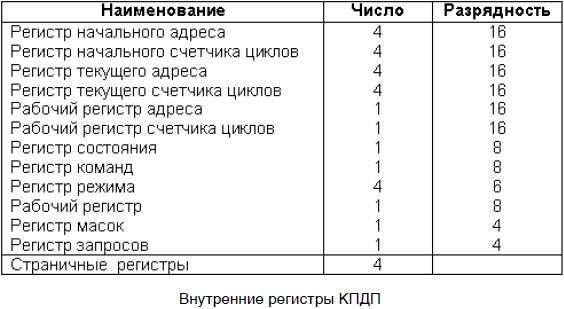

Перед началом работы необходимо запрограммировать все регистры, представленные в таблице (см. таблица ниже). Часть из них программируется при инициализации системы.

Программируются:

•начальный адрес памяти для обмена;

•уменьшенное на единицу число передаваемых байтов;

•направление обмена,

•требуемые режимы работы (разрешить или запретить циклическое изменение приоритетов, автоинициализацию, задать направление изменения адреса при обмене и т. д.);

•запрограммированный канал должен быть демаскирован (бит маски канала устанавливается при этом в 0), после чего он может принимать сигналы "Запрос на ПДП", генерируемые тем внешним устройством, которое обслуживается через этот канал. Сигнал "Запрос на ПДП" может быть также инициирован установкой в 1 бита запроса данного канала в регистре запросов контроллера.

Модель внешнего устройства для программиста

- Подробности

- Родительская категория: Ввод-вывод

- Категория: Подключение периферийных устройств к ЭВМ

Каждое периферийное устройство имеет в своем составе один или несколько регистров, содержимое которых можно прочитать или записать командами программы. Сложные периферийные устройства могут содержать несколько десятков регистров. Таким образом, общее количество регистров периферийных устройств в системе может быть значительным.

Словосочетанием “модель периферийного устройства для программиста” будем называть набор регистров в периферийном устройстве, которые можно прочитать-записать программно.

Простейшая модель для программиста внешнего устройства может содержать довольно мало регистров: — регистр состояния (статуса), регистр управления, регистр (буфер) данных.

Применяют два основных способа доступа к регистрам ПУ:

- Произвольной адресации регистров;

- С индексацией регистров (SB).

В первом случае процессор по команде может записать/считать данные в любой регистр ПУ. Если ПУ имеет большое количество регистров, например, более 100, как в sound blaster, используют второй способ. В этом случае ПУ имеет два регистра: индексный регистр и регистр данных. При записи в индексный регистр заносим номер регистра ПУ, в который хотим записать, затем в регистр данных заносим записываемое число.

Адресация регистров внешнего устройства:

- изолированный ввод-вывод (порты);

- отображение на память.

В некоторых процессорах доступ к регистрам периферийных устройств осуществляется аналогично доступу к ячейкам памяти. Каждому регистру присвоен адрес в адресном пространстве памяти. В этом случае для обращения к регистрам ПУ можно использовать те же команды, что и для доступа к ячейкам памяти. Такая организация носит название "ввод-вывод, отображаемый на память". Обычно разработчики вычислительной системы выделяют для адресации регистров ПУ какой-либо фиксированный диапазон адресов.

В других процессорах регистры ПУ имеют свою систему адресации, никак не связанную с адресацией ячеек памяти. Для обращения к регистрам ПУ в системе команд имеются специальные команды ввода- вывода. Такая организация обмена с ПУ носит название "изолированный ввод-вывод". Для обозначения программно- доступных регистров периферийных устройств в компьютерной литературе используют термин "порты ввода-вывода".

Пример 1. Нулевой канал таймера имеет порт данных с адресом 40h

и порт управления с адресом 43h.

Пример 2. Приемник последовательного интерфейса COM1 имеет

порт данных с адресом 0378h и порт состояния (статуса) с адресом

03FDh. Младший бит в порте состояния (флаг окончания приема)

устанавливается в 1, если приемник принял извне байт.

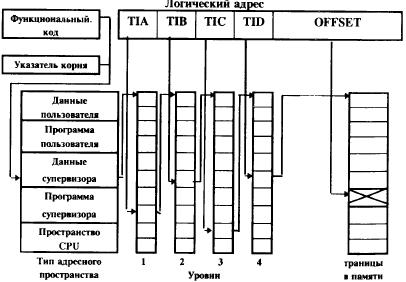

Оба вида адресации аппаратно поддержаны со стороны процессора. В первом случае в адресном пространстве процессора выделяется область адресов для ПУ. Адреса из этой области транслируются напрямую, без использования схемы преобразования (логический адрес равен физическому). В процессоре Motorola 68040 этот механизм называется “прозрачная трансляция адресов”. Для указания выделенной области регистров ПУ используются специальные регистры. В этих регистрах дополнительно имеются поля, определяющие разрешение/запрещение КЭШирования, тип доступа r/w и др. На рисунке (см. рисунок ниже) представлена схема страничной трансляции.

Схема страничной трансляции процессора МС68040

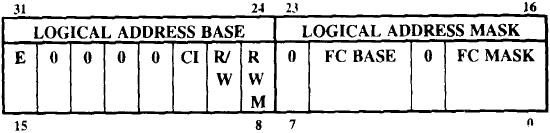

Регистры прозрачной трансляции ТТО и ТТ1 (см. рисунок ниже) определяют блоки адресного пространства, которые транслируются прозрачно (прямо): в этих блоках логические адреса являются физическими.

Формат регистров прозрачной трансляции

Значения полей регистров ТТО и ТТ1:

LOGICAL ADDRESS BASE — значение А31 — А24, определяют блок прозрачной трансляции;

LOGICAL ADDRESS MASK — игнорируемые разряды А31 — А24;

Е (Enable) — разрешение: определяет возможность прозрачной трансляции (Е=1 разрешена).

Cl (Cashe Inhibit) — КЭШ запрещен: определяет возможность использования КЭШа ( С1=0 означает, что КЭШ используется);

R/W — чтение/запись: определяет тип доступа в транслируемом блоке: (R/W=0 — запись; R/W=1 — чтение);

RWM (Read/Write Mask) — маска чтения-записи: определяет достоверность поля R/W (RWM=0 — поле используется);

FC BASE (Function Code Base) — значение функционального кода блока прозрачной трансляции;

FC MASK (Function Code Mask) — игнорируемые биты функциональною кода.

При изолированном вводе-выводе процессор должен иметь: специальные команды работы с ПУ, специальные сигналы на шине, различающие обращение к памяти и к ПУ.

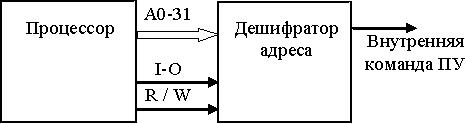

В процессорах семейства х86 использован изолированный ввод-вывод. На шине процессора имеются специальные сигналы. При обращении к памяти вырабатываются стробы MEMR, MEMW, а к ПУ — стробы I/OR, I/OW. Схема подключения приведена на рисунке (см. рисунок ниже).

Схема подключения ПУ

В составе системы команд имеются следующие две команды ввода-вывода:

- in — ввод 1/2/4-байтового элемента данных из порта в регистр процессора al/ax/eax;

- out — вывод 1/2/4-байтового элемента данных из регистра al/ax/eax в порт.

Номер порта операнда-источника в команде in или операнда-приемника в команде out можно задать двумя способами: непосредственной адресацией или косвенно-регистровой с использованием только регистра dx.

!Примеры.

in al,040h; ввести байт в al из порта 40h

mov dx,0378h; записать номер порта 0378h в регистр dx

in al,dx; ввести байт в al из порта 0378h

mov al,049h; записать байт 49h в регистр al

out dx,al; вывести байт из al в порт, номер которого содержится в dx

Кроме того, в системе команд есть две строковые (цепочечные) команды ввода-вывода:

- insb / insw / insd - ввод из порта цепочки (строки) байтов/слов/двойных слов в последовательные адреса памяти;

- outsb / outsw /outsd — вывод цепочки (строки) байтов/слов/двойных слов из последовательных адресов памяти в порт.

Структурная схема модуля на базе шины ISA

- Подробности

- Родительская категория: Ввод-вывод

- Категория: Шина ISA

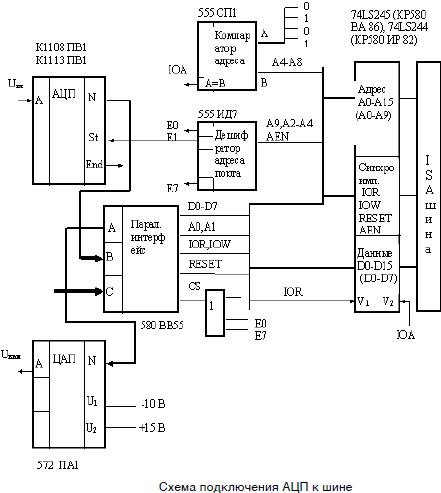

Подробная структурная схема модуля Plug in Data Acquisition Board приведена на рисунке (см. рисунок ниже). На рисунке показаны не только составляющие модуль элементы, но и перечислены микросхе-мы для их реализации.

В модуле можно выделить следующие элементы:

•буфер системной ши-ны,

•схему декодирования адреса порта,

•параллельный ввод-вывод КР580 ВВ55 (Intel 8255),

•микросхемы АЦП и ЦАП.

Аппаратные прерывания и проблема приоритетов

- Подробности

- Родительская категория: Ввод-вывод

- Категория: Прерывания

Термином “аппаратное прерывание” называют ситуацию, когда источник прерывания — устройство, внешнее по отношению к вычислительному ядру, а событие, вызвавшее прерывание, не синхронизировано с процессом выполнения программы. Иногда источник запроса может быть интегрирован в одну микросхему с процессором (например, таймер в однокристальном микроконтроллере), но логически процессор и таймер независимы (и даже могут тактироваться от разных генераторов).

Типичный пример использования внешнего прерывания: по сигналу готовности принтера (говорящему о том, что предыдущая порция текста напечатана) выдать на него следующую порцию текстовой информации.

Используются две основные схемы подключения источников запросов к процессору: радиальная и магистральная.

При магистральной схеме запросы от всех источников поступают на одну и ту же линию запроса. После приема запроса процессор проводит с устройствами обмен сигналами с целью выяснить источник запроса. При этом усложняются схемы обслуживания прерываний и увеличивается время реакции на запрос, что в некоторых случаях оказывается нежелательным.

При радиальной схеме каждый источник запроса использует индивидуальный вход запроса, в результате чего процессор может определить источник запроса и осуществить переход на соответствующую подпрограму обработки.

В том случае, когда несколько запросов требуют обработки одновременно, может оказаться, что некоторые из запросов более важны и должны быть обработаны в первую очередь. Для этого система управления прерываниями должна давать программисту возможность определять приоритеты, т.е. порядок реакции на запросы.

Еще статьи...

Подкатегории

-

Прямой доступ к памяти (ПДП)

- Кол-во материалов:

- 2

-

Программирование контроллера прерываний i8259А

- Кол-во материалов:

- 11

-

Прерывания

- Кол-во материалов:

- 9

-

Синхронизация программ с внешними процессами

- Кол-во материалов:

- 2

-

Шина ISA

- Кол-во материалов:

- 4

-

Подключение периферийных устройств к ЭВМ

- Кол-во материалов:

- 3