Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

Шина IEEE 1394 — FireWire

Архитектура узла

- Подробности

- Родительская категория: Шина IEEE 1394 — FireWire

- Категория: Основная информация

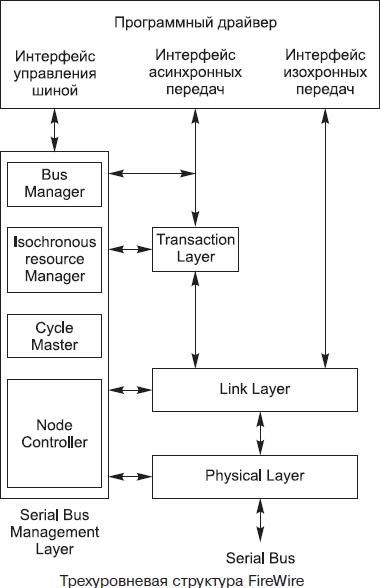

В плане описания работы шины наибольший интерес представляет узел. Узел имеет явно выраженную трехуровневую структуру средств FireWire, к которой обращаются драйверы прикладного и системного ПО (см. рисунок ниже):

- физический уровень — PHY (Physical Layer) выполняет основные функции, связанные с подключением узла к шине:

- подключение узла к шине (механическое и электрическое);

- автоматическое конфигурирование шины и узла при инициализации;

- арбитраж при передаче данных;

- кодирование и декодирование сигналов состояния шины и потоков данных;

- предоставление сервисов канальному уровню;

- связь сегментов сети в единую шину, если он имеет более одного порта IEEE 1394 (трансляцию сигналов между своими портами);

- предоставление питания по кабельной шине.

- Физический уровень допускает несколько вариантов физического интерфейса:

- кабельная шина 1394/1394a с DS-кодированием, поддерживающая скорости S100, S200 и S400 на экранированной витой паре;

- кросс-шина (backplane serial bus, BPSB) с DS-кодированием, поддерживающая скорости S50 и S100 при связи узлов в пределах шасси;

- кабельная шина 1394b с кодированием 8B10B (так называемый бета-режим), поддерживающая скорости от S100 до S1600 и разные варианты кабелей: экранированная витая пара, неэкранированная (UTP-5), пластиковое и стеклянное многомодовое оптоволокно.

- канальный уровень LINK (Link Layer) из данных физического уровня формирует пакеты и выполняет обратные преобразования. При этом он формирует (при передаче) и проверяет (при приеме) формат пакета и контрольные поля (CRC-коды). Он обеспечивает асинхронный обмен узлов дейтаграммами (пакетами запросов, ответов и пакетами квитирования), а также передачу и прием изохронных потоков. Канальный уровень отвечает за адресацию — выявление и прием пакетов, предназначенных данному узлу:

- широковещательных;

- по адресу узла (для асинхронных транзакций);

- по номеру канала (для изохронных и асинхронных потоков);

- уровень транзакций (Transaction Layer) предоставляет приложениям сервисы для асинхронных обменов с регистрам и памятью любых узлов сети, состоящей из множества шин, объединенных мостами. Операции обменов включают чтение, запись, блокированные операции (чтение-модификация-запись). Операцией записи в специальный регистр узла можно вызвать прерывание для данного узла, при этом биты данного регистра будут нести информацию о соответствующих условиях прерывания. Уровень транзакций реализует протокол запросовответов, соответствующий стандарту ISO/IEC 13213:1994 (ANSI/IEEE 1212, редакция 1994 года) архитектуры регистров управления и состояния CSR (Control and Status Register) для микрокомпьютерных шин. Это облегчает связь шины 1394 со стандартными параллельными шинами. На уровне транзакций выполняется часть действий по обработке ошибок и организации повторов передач (канальный уровень только сообщает об обнаруженных ошибках).

Драйверы прикладного и системного ПО для организации асинхронных транзакций пользуются сервисами уровня транзакций. В плане обработки ошибок уровень транзакций предоставляет только уведомления об успехе или неудаче выполнения транзакции. В последнем случае организация повторов ложится на драйвер. Для изохронных передач (и потоковых асинхронных) драйвер пользуется сервисами канального уровня, который в данном случае обеспечивает лишь передачу пакетов, прием пакетов требуемых каналов с индикацией наличия или отсутствия ошибки в данных.

Управление шиной (Bus management) затрагивает все вышеперечисленные уровни. Шина может иметь различные степени управляемости: полностью управляемая, частично управляемая (с диспетчером изохронных ресурсов, необходимым, если есть узлы с изохронным обменом) и даже неуправляемая шина.

Узел может быть вырожденным до простого кабельного сетевого концентратора — иметь только компоненты физического уровня. Его многопортовый PHY будет выполнять функции повторителя, не нуждаясь в вышестоящих уровнях.

Интерфейс IEEE 1394 реализуется аппаратно-программными средствами устройства. Аппаратная часть FireWire обычно состоит из двух специализированных микросхем — трансивера физического уровня (PHY Transceiver) и моста связи с микропроцессорной шиной (LINK Chip). Интерфейс между ними описан стандартом IEEE 1394. Микросхема LINK выполняет все функции канального уровня и часть функций уровня транзакций; остальная часть уровня транзакций выполняется программно. Микросхема PHY выполняет сигнальное кодирование-декодирование данных, распознавание адресов, функции арбитража, а также трансляцию сигналов между своими портами. Уровень PHY достаточно автономен, все «общественнополезные» функции узла он может выполнять и при отключенных вышестоящих уровнях. Физический уровень может быть (но не обязательно) гальванически развязан с канальным уровнем. В бета-режиме (1394b) гальваническая развязка (более эффективная) возможна на уровне кабельного интерфейса. Гальваническая развязка необходима для предотвращения возникновения паразитных контуров общего провода, которые могут появиться через провода защитного заземления блоков питания.

Физический и канальный уровни могут различаться в плане поддерживаемых скоростей передачи. Если многопортовый PHY поддерживает более высокие скорости, чем LINK, то он способен транслировать высокоскоростные пакеты между своими портами. Однако скорость, на которой сам узел может общаться с остальными узлами шины, определяется самым слабым звеном в данной паре PHY-LINK. В этом случае она будет ограничиваться возможностями LINK-уровня; эти возможности могут зависеть от организации узла. Для компьютера, подключаемого к 1394, поддерживаемая скорость LINK зависит от производительности шины, которой подключен адаптер, и производительности его контролера памяти. Физический уровень для различных устройств практически одинаков, различия касаются поддерживаемых скоростей передачи, а в 1394b — и используемой среды передачи (разновидностей медных и оптических кабелей). Канальный уровень существенно зависит от прикладной части устройства — микропроцессора, на котором базируется устройство, и интерфейса подключения канального уровня.