Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

Процессоры

Архитектура AMD K7

Особенности микроархитектуры Athlon

- Подробности

- Родительская категория: Процессоры

- Категория: Архитектура AMD K7

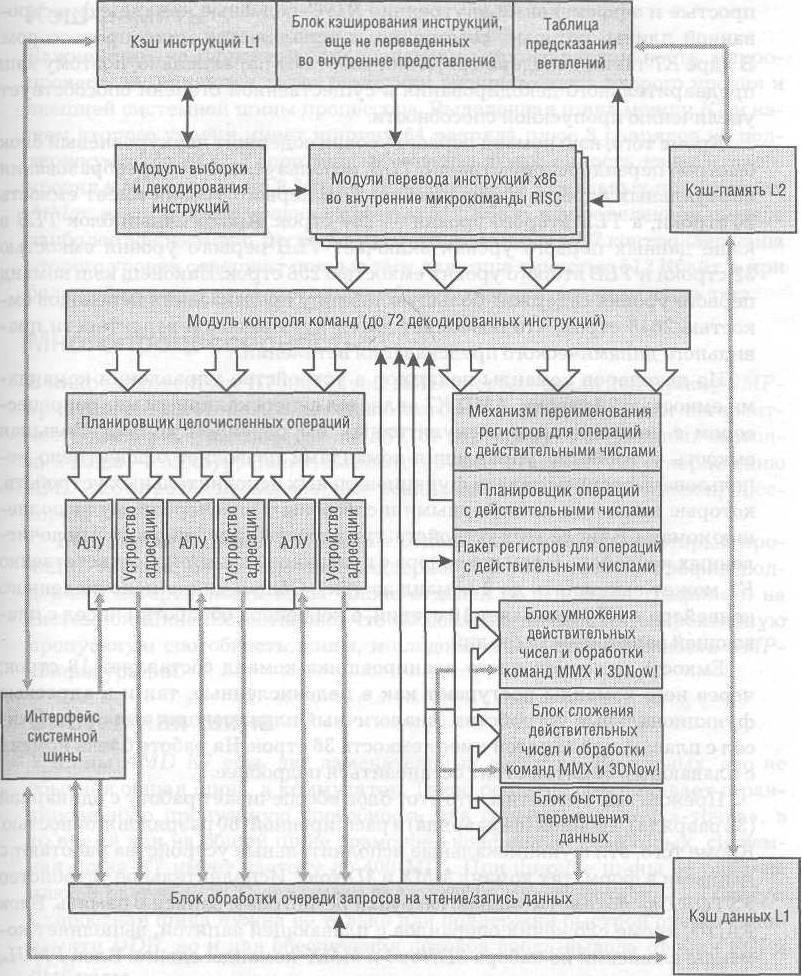

Создание в 1999 г. процессорного ядра К7 седьмого поколения стало значительным достижением компании AMD. В процессоре Athlon были реализованы выдающиеся технические решения: три параллельных исполнительных конвейера, системная шина с удвоенной частотой за счет передачи данных по фронту и спаду сигнала, асинхронная шина памяти, блоки декодера и предварительной выборки данных высокой интеллектуальности.

Кэш-память первого уровня включает двухканальные частично-ассоциативные (наборно-ассоциативные) кэш команд и кэш данных емкостью по 64 Кбайт каждый. Кэш данных К7 обеспечивает одновременный доступ к двум 64-разрядным величинам при выполнении команд загрузки регистров и записи в память. Другой важной особенностью К7 является наличие в блоке кэша команд специальной кэш-памяти предварительного декодирования, которая используется декодерами команд. Напомним, что в современных х86-совместимых процессорах прямого выполнения х86-команд не происходит, поскольку они неудобны для достижения максимума производительности. х86-инструкции декодируются в более простые и эффективные внутренние RISC -подобные команды фиксированной длины, которые, собственно, и исполняются микропроцессором.

В ядре К7 таких декодера три, и они работают параллельно, поэтому кэш предварительного декодирования в существенной степени способствует увеличению пропускной способности.

Кроме того, кэш команд первого уровня содержит двухуровневый блок быстрой переадресации страниц TLB, используемый для преобразования виртуальных адресов в физические: TLB первого уровня имеет емкость 24 строки, a TLB второго уровня — 256 строк. Аналогичный блок TLB в кэше данных первого уровня включает TLB первого уровня емкостью 32 строки и TLB второго уровня емкостью 256 строк. Наконец, кэш команд первого уровня содержит большую таблицу предсказания переходов емкостью 2048 строк, что позволяет достигнуть высокой вероятности правильного динамического предсказания ветвлений.

Из декодеров команды попадают в устройство управления командами емкостью 72 строки. AMD K7 является суперскалярным микропроцессором с внеочередным спекулятивным выполнением команд. Большая емкость устройства управления командами позволяет эффективно использовать ресурсы девяти функциональных исполнительных устройств, которые являются конвейерными и способны к внеочередному выполнению команд. В числе этих устройств: три адресных конвейера, три целочисленных конвейера и три конвейера с плавающей запятой. Соответственно К7 может выполнять до 9 команд за такт. Общая длина целочисленного конвейера в К7 составляет 10 стадий, а конвейера обработки чисел с плавающей запятой — 15 стадий.

Емкость целочисленного планировщика команд составляет 18 строк; через него команды поступают как в целочисленные, так и в адресные функциональные устройства. Аналогичный планировщик команд для чисел с плавающей запятой имеет емкость 36 строк. На работе блока команд с плавающей запятой стоит остановиться подробнее.

Прежде всего отметим, что этот блок обеспечивает работу с одинарной (32 разряда), двойной (64 разряда) и расширенной (80 разрядов) точностью. Кроме того, эти функциональные исполнительные устройства работают с данными в форматах команд ММХ и 3DNow!, Исполнительное устройство FSTORE выполняет команды загрузки регистров и записи в память. Блок FADD, кроме сложения операндов с плавающей запятой, выполняет команды сложения из набора 3DNow! и ММХ-команды сдвига. Блок FMUL, кроме умножения чисел с плавающей запятой, выполняет ММХ-команды, команды 3DNow! и специальные операции деления. Таким образом, К7 может одновременно выполнять сложение и умножение чисел с плавающей запятой в блоках FADD и FMUL. Это дает пиковую производительность в две операции с действительными за такт.

Функциональная схема микроархитектуры К7

Кэш-память

- Подробности

- Родительская категория: Процессоры

- Категория: Архитектура AMD K7

Важнейшим компонентом, определяющим производительность микропроцессора, являются характеристики внешнего кэша второго уровня и внешней системной шины процессора. Выделенная шина между К7 и кэшем второго уровня имеет ширину 64 разряда плюс 8 разрядов на под- держку кодов ЕСС. Теоретически максимальная емкость кэша второго уровня в К7 составляет 8 Мбайт. Использование в реальных процессорах Athlon кэша второго уровня емкостью 512 Кбайт в определенном смысле наиболее эффективно, поскольку интегрированный в К7 контроллер кэша второго уровня содержит полные теги для кэша емкостью 512 Кбайт, а при большей ёмкости кэша контроллер будет содержать только часть тега.

Многопроцессорность

- Подробности

- Родительская категория: Процессоры

- Категория: Архитектура AMD K7

В микроархитектуре К7 инженеры AMD впервые ввели поддержку SMP-архитектур. Протокол, с помощью которого поддерживается когерентность кэша в К7, называется MOESI (от первых букв возможных состояний кэша — Modify, Owner, Exclusive, Shared, Invalid). По утверждению AMD, этот протокол был впервые реализован в х8б-совместимых процессорах.

Кэш первого уровня в К7 имеет отдельный порт, через который проходит трафик, обусловленной поддержкой когерентности. Трафик поддержки когерентности кэша также отделен от основного трафика и на системной шине. Естественно, что обособление повышает эффективную пропускную способность шины, и следовательно, эффективность SMP-конфигураций.

Системная шина

- Подробности

- Родительская категория: Процессоры

- Категория: Архитектура AMD K7

У шины AMD K7 есть два замечательных свойства. Во-первых, это не обычная общая шина, а коммутатор. Такое решение обеспечивает гарантированную пропускную способность для соединений «точка-точка», в то время как на общей шине возможны конфликты. Во-вторых, системная шина К7 имеет частоту до 400 МГц. При ширине шины 64 разряда плюс 8 разрядов ЕСС она имеет пропускную способность до 3,2 Гбайт/с. Скоростная шина нужна не только для поддержки быстрой оперативной памяти DDR, но и для обеспечения потоков ввода-вывода от шин PCI и AGP.

Интерфейс системной шины К7 электрически совместим с протоколом шины Alpha EV6. Микропроцессор К7 подсоединяется к шине через интерфейс Socket A (Socket 462). Важной особенностью, влияющей на пропускную способность шины К7, является объем передаваемых по шине пакетов. Такая пакетная передача данных способствует конвейеризации обработки транзакций на шине. Для К7 размер пакета составляет 64 байта (длина строки кэша), что вдвое больше, чем у процессоров поколения Р6. Эффективному использованию системной шины способствует раздельная обработка транзакций. Она позволяет перекрывать выполнение различных транзакций во времени, разрешая начинать обработку новых транзакций, не дожидаясь завершения предыдущих. Теоретически максимальная емкость адресуемой шиной оперативной памяти в К7 составляет 8 Тбайт, но реально наборы системной логики поддерживают до 4 Гбайт.

Особенности микроархитектуры Athlon XP

- Подробности

- Родительская категория: Процессоры

- Категория: Архитектура AMD K7

В октябре 2001 г. на рынок поступили первые процессоры Athlon на ядре Palomino. Этой модификации был присвоен индекс XP (eXtreme Perfomance), подчеркивающий новшества архитектуры в сравнении с «обычным» Athlon. Так, в частности, существенной переделке подвергся механизм трансляции адресов команд и данных в физические адреса памяти. Для ускорения доступа к командам и данным все современные процессоры имеют Translation Look-aside Buffer (TLB). Этот буфер осуществляет кэширование, но не данных или команд, а их физических адресов. В предыдущих процессорах Athlon этот буфер был двухуровневым. Первый уровень (L1) емкостью 24 значения для адресов инструкций и 32 значения для адресов данных. Второй уровень (L2) мог хранить до 256 адресов данных и 256 адресов инструкций.

В ядре Palomino увеличен размер буфера первого уровня, теперь он может хранить до 40 значений адресов данных. Кроме того, теперь TLB, также как и основной кэш, стал «исключающим» — exclusive. Это означает, что содержимое буфера первого уровня не дублирует содержимого буфера второго уровня. И наконец, в новом ядре реализован механизм опережающей загрузки новых значений адресов (до того, как они могут потребоваться) — speculatively reload.

Существенно улучшен механизм опережающей загрузки данных из памяти в кэш. Этот механизм опережающей загрузки данных был реализован и в ранних процессорах, но только для инструкций, включенных в 3DNow! и SSE. В ядре процессоров Athlon XP осуществляется непрерывный анализ адресов затребованных процессором данных и последовательности, в которой они были затребованы. На основании анализа делается попытка предсказания адресов данных, которые будут затребованы, и опережающая загрузка этих данных в кэш процессора. Во многих случаях, например, при циклической обработке больших массивов данных, предсказание будет успешным. Это позволяет повысить производительность даже для неоптимизированных приложений.

В ядре Palomino полностью реализованы как система команд 3DNow!, так и система команд SSE. Этот комплексный набор получил название 3DNow! Professional Technology.

Перечисленные изменения потребовали очередного увеличения количества транзисторов — до 37,5 миллионов. Однако это не привело к повышению потребляемой мощности. Более того, процессор Athlon ХР стал примерно на 20% «холоднее» своего предшественника.

Еще статьи...

Интегративный нутрициолог: блог Нутрициолога читать сайт.