Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

Аренда теплохода на свадьбу цена заказать свадьбу на теплоходе teplohod-piter.ru. Свежая информация американские окна на сайте.

Процессор

Процессор — аппаратный уровень.

Процессор — аппаратный уровень. Операционные устройства

- Подробности

- Родительская категория: Процессор

- Категория: Процессор — аппаратный уровень.

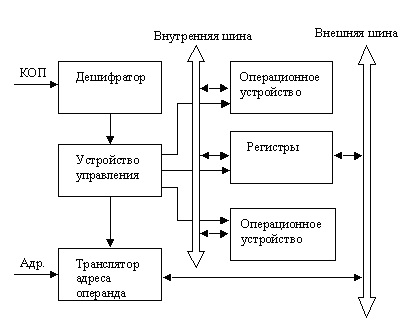

Процессор — это ядро и мотор компьютера, обеспечивает как выполнение операций, так и функционирование всех узлов. Обычно простой процессор включает в себя декодер команд, арифметико-логическое устройство (АЛУ), регистры, транслятор адресов операндов и устройство управления. Отдельные элементы связаны внутренней шиной. Связь с внешними устройствами осуществляется через внешнюю шину.

Структура процессора

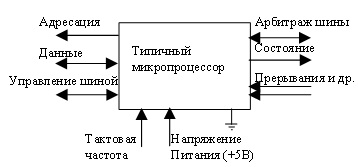

Все перечисленные элементы могут помещаться в одной микросхеме — микропроцессоре. Они доступны через выводы микросхемы при выполнении команд, загружаемых из ОЗУ. На следующем рисунке показаны выводы типичного микропроцессора. Рассмотрим как работает процессор изнутри, на аппаратном и микропрограммном уровне. Далее будет представлено рассмотрение конкретного процессора i8086.

Типичный процессор

Аппаратный уровень процессора в настоящее время не является ни программно доступным, ни даже наблюдаемым, однако представление о нем помогает пониманию таких вопросов, как скорость выполнения команд, возможность конвейеризации и т.д.

Для того чтобы понять как выполняются команды в процессоре рассмотрим работу операционных устройств. В машине фон Неймана в качестве операционного устройства применяется АЛУ. Учитывая разнообразие выполняемых операций и обрабатываемых данных, можно говорить не об одном устройстве, а о целом комплексе специализированных операционных устройств, каждое из которых выполняет свое подмножество операций (команд). Следует выделить операционные устройства:

- целочисленной арифметики;

- логических операций;

- десятичной арифметики;

- чисел с плавающей запятой.

Кроме указанных устройств процессоры в зависимости от их назначения могут иметь и другие операционные устройства: управления потреблением, графических операций, упаковки/распаковки изображений и др. В минимальном варианте операционное устройство целочисленной арифметики (АЛУ) должно содержать аппаратуру для реализации лишь основных логических операций, сдвигов, инвертирования, а также сложения чисел в формате с фиксированной запятой. Опираясь на этот набор, можно программным способом обеспечить выполнение остальных арифметических и логических операций как для чисел с фиксированной запятой, так и для других форм представления информации. Следует отметить, что подобный вариант не позволяет добиться высокой скорости вычислений, поэтому по мере расширения технологических возможностей доля аппаратных средств в составе АЛУ постоянно возрастает. Набор элементов, на основе которых строятся структуры различных операционных устройств, называется структурным базисом. Структурный базис операционных устройств включает в себя:

- регистры, обеспечивающие хранение слов данных;

- шины, связывающие регистры и предназначенные для передачи слов данных;

- комбинационные схемы, реализующие вычисления по управляющим сигналам от устройства управления.

Выполнение команды может быть сведено к нескольким (одновременно или последовательно во времени) операциям пересылки из регистра в регистр(на рисунке). Возможно с промежуточным преобразованием пересылаемых двоичных слов на комбинационных логических схемах. В следующей теме подробно рассмотрим регистры.

Регистры операционного устройства

Регистры. Шины. Вентили (Gates)

- Подробности

- Родительская категория: Процессор

- Категория: Процессор — аппаратный уровень.

Регистры

Регистр хранит двоичное слово. Регистр — это линейка триггеров, которые имеют входы для изменения состояния, влияющее на выходы.

Регистры могут быть:

- программно-видимые явно;

- видимые косвенно, такие, накпример, как "теневые" регистры дескрипторов сегментов;

- внутренние, предназначенные для специальных целей, например, регистр адреса памяти и регистр данных для обмена с памятью — про них ,по крайней мере, известно, для чего они предназначены;

- внутренние — для хранения внутренних промежуточных результатов и т.д.

Кроме того, в процессоре могут быть "псевдо-регистры", хранящие константы: 0, 1, -1, и др. (м.б. такие, как , e,...).

Шины

Это просто группа параллельных проводов, связывающих между собой два адресата и позволяющих передать слово данных параллельным кодом.

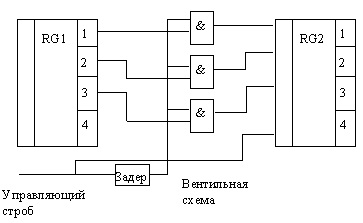

Вентили

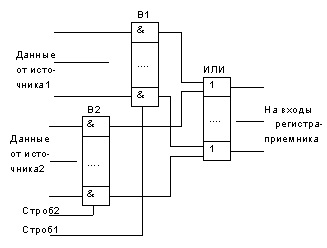

Регистры операционного устройства

Это логические элементы (коньюнкторы), разрешающие передачу данных (например, на вход триггера). Схема передачи слова данных от источника к приемнику изображена выше на рисунке. Она обеспечивает возможность управлять моментом передачи, подавая в нужный момент сигнал "строб". Слово данных от источника данных (им может быть другой регистр) подается на входы элементов "И". Выходы элементов "И" (вентилей) действуют на входы установки регистра-приемника. Для записи нового кода в регистр-приемник надо последовательно выполнить два действия:

- сбросить старый код в регистре,

- разрешить запись сигналом, подаваемым на вторые входы вентилей. Второй сигнал задержан относительно первого (в элементе задержки).

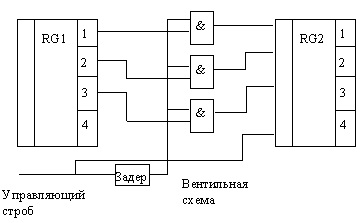

Несколько вентильных линеек В1, В2,...могут быть объединены по выходам линейкой элементов "ИЛИ". Такая структура позволяет передавать слово данных на вход регистра-приемника от одного из нескольких источников при действии разных стробовых сигналов. Такую структуру принято называть мультиплексором (ниже на рисунке).

Простейший мультиплексор

Арифметико логическое устройство (АЛУ)

- Подробности

- Родительская категория: Процессор

- Категория: Процессор — аппаратный уровень.

Общие сведения об арифметико логическом устройстве

Арифметико логическое устройство - это комбинационная схема, (т.е. она не содержит внутри элементов памяти), выполняющая следующие функции:

- принимающая на два входа два операнда (например, содержимое двух регистров);

- формирующая на выходе результат операции.

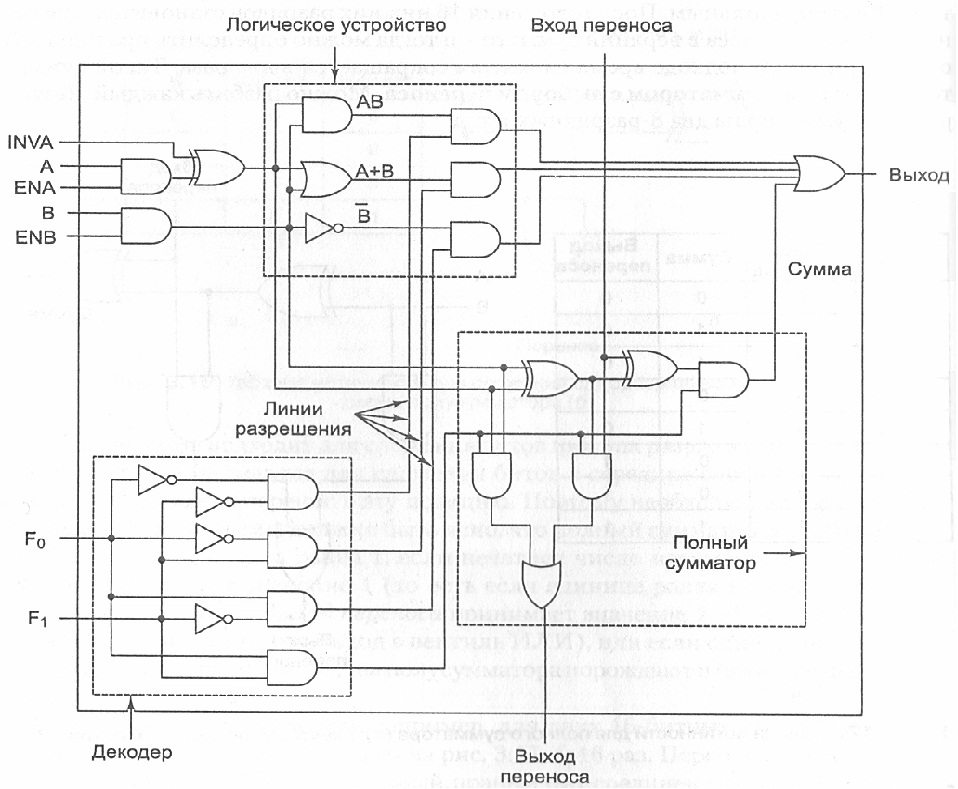

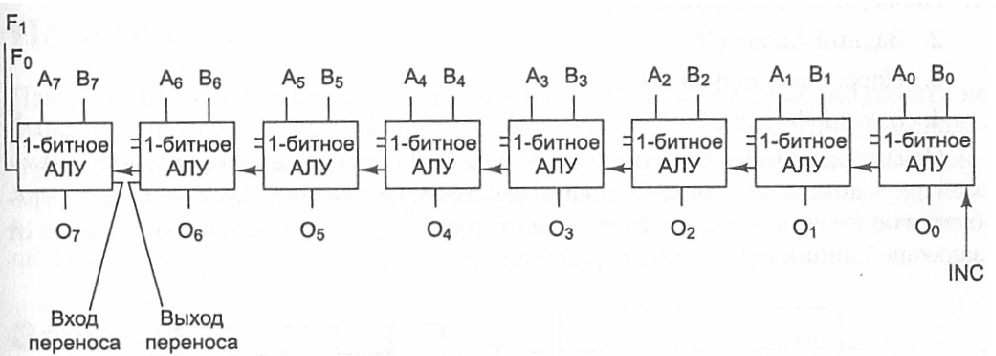

Большинство компьютеров содержат одну общую схему для выполнения операций И, ИЛИ и сложения над двумя машинными словами. Обычно такая схема для n-битных слов состоит из n идентичных схем для индивидуальных битовых позиций. На рисунке изображена схема одноразрядного АЛУ. Это устройство может вычислять одну из 4 следующих функций: А И В, А ИЛИ В, В- и А + В. Выбор функции зависит от того, какие сигналы поступают на линии F0 и F1: 00, 01, 10 или 11 (в двоичной системе счисления). Отметим, что здесь А+В означает арифметическую сумму А и В, а не логическую операцию И. В левом нижнем углу схемы находится двухразрядный декодер, который порождает сигналы включения для четырех операций. Выбор операции определяется сигналами управления F0 и F1. В зависимости от значений F0 и F1 выбирается одна из четырех линий разрешения, и тогда выходной сигнал выбранной функции проходит через последний вентиль ИЛИ. В верхнем левом углу схемы находится логическое устройство для вычисления А И В, А ИЛИ В и В-, но по крайней мере, один из этих результатов проходит через последний вентиль ИЛИ в зависимости от того, какую из разрешающих линий выбрал декодер. Так как ровно один из выходных сигналов декодера будет равен 1, то и запускаться будет ровно один из четырех вентилей И.

Схема одноразрядного АЛУ

Остальные три вентиля будут выдавать 0 независимо от значений А и В.АЛУ может выполнять не только логические и арифметические операции над А и В, но и делать их равными нулю, отрицая ENA (сигнал разрешения А) или ENB (сигнал разрешения В). Можно также получить А-, установив INV А (инверсию А). При нормальных условиях и ENA, и ENB равны 1, чтобы разрешить поступление обоих входных сигналов, а сигнал INV А равен 0. В этом случае А и В просто поступают в логическое устройство без изменений. В нижнем правом углу находится полный сумматор для подсчета суммы А и В и для осуществления переносов. Переносы необходимы, поскольку несколько таких схем могут быть соединены для выполнения операций над целыми словами. Одноразрядные схемы, подобные той, которая изображена выше, называются разрядными микропроцессорными секциями. Они позволяют разработчику сконструировать АЛУ любой желаемой ширины. АЛУ можно представить как комбинационную схему, имеющую две входные шины (туда подаются два операнда) и одну выходную (на ней получается результат). Кроме того, АЛУ имеет несколько управляющих входов, сигналы на которых определяют выполняемую операцию(рисунок ниже).

Схема восьмиразрядного АЛУ и его обозначение

Операционные устройства с плавающей запятой

- Подробности

- Родительская категория: Процессор

- Категория: Процессор — аппаратный уровень.

Операции над числами с плавающей запятой имеют существенные отличия от операций целочисленной арифметики, поэтому их реализуют с помощью самостоятельного операционного устройства (ОП). Минимальный набор операций этого устройства включает четыре действия: сложение, вычитание, умножение и деление. Операции выполняются над числами в формате IEEE 754. Особенностью ОП является то, что операции над тремя составляющими чисел с ПЗ (знаками, мантиссами и порядками операндов) выполняются раздельно:

- блоком обработки знаков;

- блоком обработки порядков;

- блоком обработки мантисс.

Для хранения операндов и результата предусмотрены соответствующие регистры. В арифметике с плавающей запятой сложение и вычитание — более сложные операции, чем умножение и деление. Это обусловлено тем, что необходимо выравнивать порядки операндов. Алгоритм сложения включает следующие этапы:

- Подготовительный этап.

- Определение операнда, имеющего меньший порядок, и сдвиг его мантиссы вправо на число разрядов, равное разности порядков операндов.

- Приравнивание порядка результата большему из порядков операндов.

- Сложение мантисс.

- Проверка на переполнение.

- Заключительный этап.

Подготовительный этап осуществляет "распаковку" чисел с ПЗ, загрузку трех составляющих. В старший разряд мантиссы восстанавливается единица. Здесь может быть выполнена проверка на равенство нулю одного или обоих операндов. Это позволяет исключить ненужные операции. Действия на заключительном этапе сводятся к выявлению нулевого значения мантиссы, нормализации мантиссы, выявлению отрицательного переполнения порядка (появляется денормализованный операнд), "упаковке" составляющих результата. В отличие от целочисленной арифметики, в операциях с ПЗ сложение и вычитание производятся приближенно, так как при выравнивании порядков происходит потеря младших разрядов одного из слагаемых. В этом случае погрешность всегда отрицательна и может доходить до единицы младшего разряда. Умножение чисел с ПЗ включает следующую последовательность этапов:

- Подготовительный этап.

- Проверка на равенство нулю одного из сомножителей. Если один из них ноль, то в качестве результата выдается нуль в формате чисел с ПЗ.

- Сложение порядков. Если используется смещенный порядок, то из полученной суммы вычитается величина смещения. Проводится анализ переполнения и антипереполнения поля порядка (возникает прерывание по особому случаю).

- Перемножение мантисс с учетом знака. Результат округляется до длины поля мантиссы.

- Заключительный этап.