Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

Самая свежая информация полимерные полы цена за м2 у нас на сайте. Актуальная информация kerabond здесь.

Память. Верхний уровень

Сиситемные регистры процессоров Intel хх86

Сиситемные регистры процессоров Intel х86

- Подробности

- Родительская категория: Память. Верхний уровень

- Категория: Сиситемные регистры процессоров Intel хх86

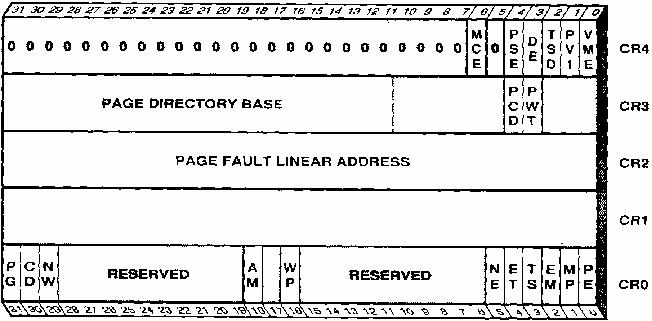

На рисунке ниже показан формат управляющих регистров CR0, CR2, CR3 и CR4. В большинстве систем загрузка управляющих регистров из прикладных программ невозможна (хотя в незащищенных системах такая загрузка разрешается).

Формат регистров управления

Прикладные программы имеют возможность считывать эти регистры, например, для определения наличия математического сопроцессора. Некоторые разновидности команды MOV позволяют загружать управляющие регистры из регистров общего назначения, и наоборот.

Например,

MOV EAX, CR0

MOV CR3, EBX

Назначения регистров: СRO, CR4 — управляющие. CR1 — резерв. CR2 — линейный адрес страничной ошибки. CR3 — база каталога таблиц страниц.

Регистры CR0, CR4 содержат системные управляющие флаги, которые управляют режимами или указывают на состояние процессора в целом, а не относительно выполнения конкретных задач. Программа не должна пытаться изменить состояние каких-либо битов в зарезервированных позициях. Эти зарезервированные биты всегда должны устанавливаться в то состояние, которое они имели ранее при считывании.

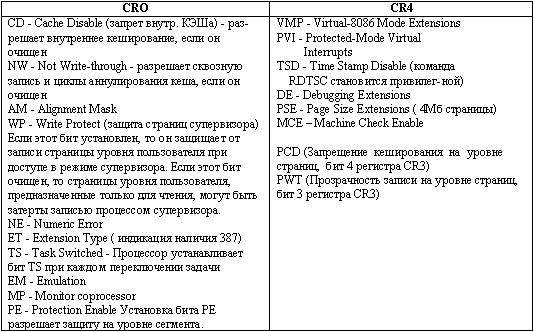

Назначение большинства битов управляющих регистров приведено в нижеследующей таблице (см. таблица ниже).

Биты управляющих регистров

Отладка и отладочные регистры

- Подробности

- Родительская категория: Память. Верхний уровень

- Категория: Сиситемные регистры процессоров Intel хх86

Процессор обеспечивает расширенные отладочные средства, которые, в частности, полезны для разработки сложных программных систем, таких, как мультизадачные операционные системы. Условия сбоя для этих программных систем могут быть очень сложными и зависимыми от времени. Отладочные средства процессора предоставляют системному программисту мощный инструмент просмотра динамического состояния процессора.

Отладка поддерживается посредством отладочных регистров. Они содержат адреса точек памяти, называемых контрольными точками (точками останова), которые запускают отладочное программное обеспечение. При выполнении операции с памятью по одному из этих адресов генерируется исключение. Контрольная точка задается для конкретной формы доступа к памяти, например, выборки команды или операции записи двойного слова. Отладочные регистры поддерживают как контрольные точки команд, так и контрольные точки данных.

Для других процессоров контрольные точки команд устанавливаются заменой нормальных команд командами контрольных точек. При выполнении команды контрольной точки вызывается отладчик. Однако в случае отладочных регистров процессора 386+ это не обязательно. При исключении необходимости записи в пространство кода процесс отладки упрощается (не требуется установки отображения сегментов данных в ту же область памяти, что и кодовый сегмент) и контрольные точки могут устанавливаться в ПЗУ-резидентном программном обеспечении. Кроме того, контрольные точки могут быть установлены для чтения и записи данных, что позволяет контролировать состояние данных в режиме реального времени. Доступ к этим регистрам имеют только программы с наивысшим уровнем привилегированности.

В число средств архитектуры, поддерживающих отладку, входят:

•Отладочные адресные регистры — задают адреса до четырех контрольных точек.

•Отладочный управляющий регистр — задает формы доступа к памяти для контрольных точек.

•Отладочный регистр состояния — сообщает об условиях, которые существовали в момент генерации исключения.

•Бит ловушки в TSS (T-бит) — генерирует отладочное исключение при попытке выполнить переключение задачи на задачу, для которой этот бит был установлен.

•Флаг возобновления (RF) — подавляет возобновление множественных исключений для одной и той же команды.

•Флаг трассировки (TF) — генерирует отладочное исключение после каждого выполнения команды.

•Команда контрольной точки — вызывает отладчик (генерирует отладочное исключение). Данная команда является альтернативным способом установки контрольныхточек в коде. Она особенно полезна, когда желательно иметь более четырех контрольных точек, либо при помещении контрольных точек в исходный код.

•Резервируемый вектор прерывания для исключения контрольной точки — вызывает процедуру или задачу при выполнении команды контрольной точки.

Эти средства позволяют вызывать отладчик как отдельную задачу или процедуру в контексте текущей задачи.

Для вызова отладчика могут быть использованы следующие условия:

•Переключение на конкретную задачу.

•Выполнение команды контрольной точки.

•Выполнение любой команды.

•Выполнение команды по заданному адресу.

•Чтение или запись байта, слова или двойного слова по конкретному заданному адресу.

•Запись в байт, слово или двойное слово по заданному адресу.

•Попытка изменить содержимое отладочного регистра.

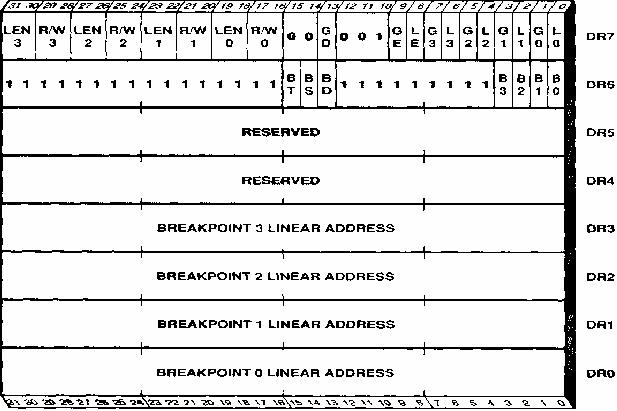

Формат регистров отладки

Отладочные адресные регистры. Отладочный управляющий регистр (DR7)

- Подробности

- Родительская категория: Память. Верхний уровень

- Категория: Сиситемные регистры процессоров Intel хх86

Отладочные адресные регистры (DR0-DR3)

Каждый из этих регистров содержит линейный адрес одной из четырех контрольных точек. При разрешенной подкачке страниц эти адреса транслируются в физические адреса по алгоритму подкачки страниц. Условие каждой контрольной точки определяется содержимым регистра DR7.

Отладочный управляющий регистр (DR7)

Отладочный управляющий регистр задает вид доступа к памяти, связанный с каждой контрольной точкой. Каждый адрес в регистрах DR0 — DR3 соответствует полю R/W0 — R/W3 в регистре DR7.

Процессор интерпретирует их следующим образом:

00 — прерывание только при выполнении команды;

01 — прерывание только при записи данных;

10 — не определено;

11 — прерывание при чтении и записи данных, но не при выборке команды.

Поля LEN0 — LEN3 регистра DR7 задают размер позиции памяти, для которой установлены контрольные точки. Может быть задан размер в 1, 2 или 4 байта. Поля длины интерпретируются следующим образом:

00 — длина один байт;

01 — длина два байта;

10 — не определено;

11 — длина четыре байта.

Младшие восемь битов регистра DR7 (поля от L0 до L3 и от G0 до G3) по отдельности разрешают условия контрольных точек в четырех адресах. Существует два уровня их разрешения: локальный (от L0 до L3) и глобальный (от G0 до G3).

Локальные биты разрешения автоматически очищаются процессором при каждом переключении задачи, чтобы избежать нежелательных условий контрольных точек в новой задаче. Они используются для установки контрольных точек в одной отдельной задаче. Глобальные биты разрешения при переключении задачи не очищаются. Они используются для разрешения условий контрольной точки, применимых ко всем задачам.