Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

Ввод-вывод

Прерывания

Программные прерывания

- Подробности

- Родительская категория: Ввод-вывод

- Категория: Прерывания

После введения в процессоры прерывания как способа реакции на асинхронные события оказалось, что этот же механизм удобно использовать для обращения к подпрограммам, наряду с обычной командой call.

Особенности вызова-возврата при прерывании:

1) сохранение большей части контекста, чем при выполнении call,

2) хранение адреса перехода в определенном месте (в векторе прерывания).

Эти особенности в некоторых случаях могут дать определенные преимущества.

В системах команд многих процессоров есть команда (команды) программных прерываний (software interrupt), позволяющие запустить механизм прерывания программно. Чаще всего для таких команд используются мнемоники int (от interrupt — прерывание) или trap (англ. ловушка). Команда обычно имеет один параметр, указывающий номер прерывания (т.е. фактически задающей адрес вектора — местоположение ячеек, хранящих адрес перехода на соответствующую подпрограмму).

В виде программных прерываний оформляют во многих операционных системах обращения к стандартным функциям ОС. Преимуществом такого способа является то, что разработчики ОС могут свободно модифицировать как код, реализующий системную функцию, так и его расположение в адресном пространстве, оставляя неизменным лишь адрес вектора, через который происходит обращение к этой системной функции. Таким образом, прикладная программа оказывается относительно независимой от версии ОС, если сохраняется интерфейс функции и адрес вектора.

Действия, которые должен выполнить программист, чтобы прерывание было работоспособным

- Подробности

- Родительская категория: Ввод-вывод

- Категория: Прерывания

В дальнейшем описании предполагается, что используется "свободное" прерывание.

1. Если используется аппаратное прерывание, предусмотреть соединение источника запроса с одним из свободных входов запроса. Вход надо выбирать с учетом требуемого приоритета добавляемого прерывания и возможностей контроллера прерываний по управлению приоритетами. Если используется программное прерывание, надо убедиться, что выбранный вектор свободен.

2. Написать подпрограмму реакции на запрос (обработчик, handler). Не забыть обеспечить в ней сохранение контекста на входе в обработчик и его восстановление на выходе из прерывания (иногда существуют соглашения о "свободных регистрах"). Выход надо делать командой возврата из прерывания. Примите решение, допускаете ли Вы вложенные прерывания, и, если да, то в обработчике надо разрешить прерывания процессору, так как обычно при входе в прерывания повторные прерывания процессору автоматически запрещаются.

3. Занести начальный адрес обработчика в ячейки вектора для выбранного прерывания. Это лучше делать явными присваиваниями в инициализирующей части Вашей программы.

4. Настроить контроллер прерываний на нужный режим: задать приоритет выбранного входа, задать форму сигнала запроса (для аппаратного прерывания).

5. Разрешить запрос прерывания от выбранного источника (для аппаратного прерывания).

6. Разрешить прерывания процессору.

Контроллер прерываний

- Подробности

- Родительская категория: Ввод-вывод

- Категория: Прерывания

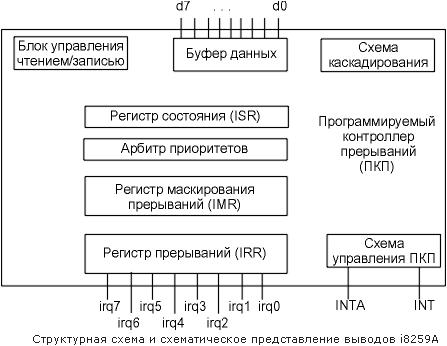

На наш взгляд, знакомство с системой прерываний микропроцессора Intel следует начать с обсуждения организации обработки аппаратных прерываний. Как видно из рис. 15.1, центральное место в схеме обработки аппаратных прерываний занимает программируемый контроллер прерываний (ПКП), выполненный в виде специальной микросхемы i8259А. Как мы уже говорили, эта микросхема может обрабатывать запросы от восьми источников внешних прерываний. Этого явно мало, поэтому в стандартной конфигурации вычислительной системы обычно используют две последовательно соединенные микросхемы i8259A. В результате такого соединения количество возможных источников внешних прерываний возрастает до 15.

Для того чтобы разобраться с обработкой аппаратных прерываний, нам придется проникнуть внутрь микросхемы i8259A. Перечислим функции, выполняемые микросхемой контроллера прерываний:

- фиксирование запросов на обработку прерывания от восьми источников, формирование единого запроса на прерывание и подача его на вход INTR микропроцессора;

- формирование номера вектора прерывания и выдача его на шину данных;

- организация приоритетной обработки прерываний;

- запрещение (маскирование) прерываний с определенными номерами.

На рисунке ниже показано схематическое представление внутренней структуры и физических выводов микросхемы i8259А.

Рассмотрим назначение представляющих для нас интерес выводов i8259А:

- d0...d7 - выводы i8259A, замыкающиеся на системную шину данных. По ним передается номер вектора прерывания и принимается управляющая информация;

- INT — вывод выходного сигнала запроса на прерывание, который подается на вход микропроцессора INTR;

- INTA - вывод для сигнала от микропроцессора, подтверждающего факт принятия им прерывания на обслуживание;

- irq0...irq7 — выводы для входных сигналов запросов на прерывания от внешних устройств.

Важное свойство данного контроллера — возможность его программирования, что позволяет достаточно гибко изменять алгоритмы обработки аппаратных прерываний. Исходя из этого, микросхема i8259А имеет два состояния:

- состояние настройки параметров обслуживания прерываний, во время которого путем посылки в определенном порядке так называемых управляющих слов производится инициализация контроллера;

- состояние работы — это обычное состояние контроллера, в котором производится фиксация запросов на прерывание и формирование управляющей информации для микропроцессора в соответствии с параметрами настройки.

Рассмотрим назначение основных структурных компонентов контроллера прерываний (см. рис. 15.2):

- регистр запросов на прерывания IRR (Interrupt Request Register) — восьмиразрядный регистр, фиксирующий поступление сигнала на один из входов i8259А — irq0...irq7. Фиксация выражается в установке соответствующего бита в единичное состояние;

- регистр маскирования прерываний IMR (Interrupt Mask Register) — восьмиразрядный регистр, с помощью которого можно запретить обработку запросов на прерывания, поступающих на соответствующие входы (уровни) irq0...irq_7. Для запрещения (маскирования) определенных уровней прерываний необходимо установить соответствующие биты регистра IMR. Эта операция осуществляется путем программирования порта 21h;

- регистр обслуживаемых прерываний ISR (Interrupt Service Register) — восьмиразрядный регистр, единичное состояние разрядов которого показывает, прерывания каких уровней обрабатываются в данный момент в микропроцессоре;

- арбитр приоритетов PR (Priority Resolver) — функцией данного блока является разрешение конфликта при одновременном поступлении запросов на входы irq0...irq7;

- блок управления - основной функцией данного блока является организация информационного обмена контроллера прерываний и микропроцессора через шину данных. На этот блок замыкаются как выводы d0...d7, так и некоторые другие (см. рис. 15.2).

Рассмотрим возможные прохождение и обработку сигнала прерывания от некоторого внешнего устройства. При этом воспользуемся структурной схемой контроллера прерываний и обозначениями на ней (см. рис. 15.2).

Допустим, на вход irq0 поступает сигнал прерывания, что приводит к установке нулевого бита регистра IRR. Этот регистр связан с регистром маски IMR, состояние битов которого определяет, какие уровни прерываний запрещены (единичные биты) или разрешены к обработке (нулевые биты). Управление данным регистром осуществляется через порт 21h. Таким образом, если бит 0 в IMR равен нулю, то прерывание уровня 0 разрешено. Далее сигнал поступает к арбитру приоритетов. Как мы уже отметили, функция этого блока — разрешение конфликтов при одновременном поступлении запросов на несколько уровней. Обычно самый высокий приоритет у уровня irq_0, и далее приоритет уменьшается с возрастанием номера уровня. Если конфликта нет, то сигнал поступает на схему управления контроллером прерываний, которая формирует сигнал на выводе int. Этот вывод связан со входом микропроцессора INTR. Таким образом, сигнал на входе i8259A достиг микропроцессора. Что происходит далее в микропроцессоре, мы рассмотрим ниже. Сейчас отметим только значимые для данного обсуждения моменты. Итак, при поступлении сигнала на вход INTR в микропроцессоре происходят следующие процессы:

- Анализируется флаг IF. Если вы помните, единичное состояние этого флага говорит о том, что аппаратные прерывания разрешены, нулевое — запрещены.

- Если прерывания запрещены, то запрос на прерывание «повисает» до момента установки IF в единицу.

- Если прерывания разрешены, микропроцессор выполняет следующие действия:

- сбрасывает флаг IF в ноль;

- формирует сигнал подтверждения прерывания на выводе микропроцессора INTA. Этот вывод микропроцессора замкнут на одноименный вывод микросхемы i8259A.

Таким образом, сигнал о прерывании прошел через микропроцессор и вернулся обратно в контроллер прерываний i8259A через вывод INTA. Данный вывод внутри контроллера прерываний замкнут на его схему управления, которая выполняет сразу несколько действий при поступлении этого сигнала:

- Сбрасывает бит в регистре IRR, соответствующий уровню прерывания irq_0.

- Устанавливает в 1 бит 0 регистра ISR, тем самым фиксируя факт обработки прерывания уровня 0 в микропроцессоре.

- Формирует с помощью блока управления номер вектора прерывания, значение которого формируется в буфере данных и далее поступает на выводы i8259A d0...d7. Выводы d0...d7 замкнуты на шину данных, по которой номер вектора поступает в микропроцессор. В микропроцессоре этот номер используется для вызова соответствующей процедуры обработки прерывания.

На данном этапе обработки прерывания, после того как номер прерывания по шине данных поступил в микропроцессор, последнему стало известно все об источнике прерывания. Далее микропроцессор осуществляет процедуру обработки прерывания. Если в это время придет другой сигнал о прерывании того же уровня, то он будет запомнен установкой бита в IRR, и обслуживание этого прерывания будет отложено. Если приходит прерывание другого уровня, то его дальнейшая обработка зависит от приоритета, который оно имеет по отношению к уже обрабатываемым прерываниям. Если приоритет выше, то текущая процедура обработки прерывания останавливается, и вызывается процедура обработки более приоритетного прерывания.

Очень важный момент связан с процессом завершения обработки прерывания. Проблема здесь состоит в следующем. После принятия микропроцессором запроса на обслуживание прерывания в контроллере устанавливается бит в регистре ISR, номер этого бита соответствует уровню прерывания. Установка бита с данным номером блокирует все прерывания уровня, начиная с текущего, и менее приоритетные в блоке-арбитре приоритетов. Если процедура прерывания закончит свою работу, то она сама должна этот бит сбросить, иначе все прерывания этого уровня и менее приоритетные будут игнорироваться. Для осуществления такого сброса необходимо послать код 20h в порт 20h. Есть и другая возможность — установить такой режим работы микросхемы i8259A, когда сброс этого бита будет производиться автоматически. Тонкий момент заключается в том, что происходить такой автоматический сброс будет одновременно с приходом сигнала INTA (то есть извещения о том, что запрос на обработку прерывания принят к обработке микропроцессором). Недостаток автоматического сброса в том, что существует вероятность прихода прерывания того же уровня, который уже обрабатывается в данный момент микропроцессором. В этом случае процедура обработки прерывания должна обладать свойством реентерабельности, то есть допускать повторное обращение к себе до завершения обработки предыдущего обращения. Для того чтобы процедура была реентерабельной, она должна иметь специфическую структуру, в частности, для каждого сеанса обращения к ней создается своя область для хранения переменных и значений регистров, а исполняемая часть процедуры находится в оперативной памяти только в одном экземпляре. Иногда может потребоваться подобный автоматический сброс, но надежнее и проще, конечно, контролировать этот процесс и самостоятельно сбрасывать бит в ISR. Это можно сделать либо в конце работы процедуры, либо в том месте процедуры, начиная с которого можно разрешить рекурсивный вызов данной процедуры, будучи уверенным в том, что она не разрушит никаких данных и работу программы в целом.

Другой не менее интересный момент заключается в том, что микропроцессор при принятии к обработке запроса на прерывание сбросил флаг IF в ноль, тем самым запретив все последующие аппаратные прерывания. Этим обстоятельством программист может пользоваться по своему усмотрению. Вы, конечно, помните, что все запросы на прерывания с приоритетом, равным текущему или меньшим, будут запрещены в любом случае, — это обусловлено логикой работы контроллера i8259A. Поэтому программист должен решить, насколько его замыслам могут помешать запросы на более приоритетные прерывания. Если это некритично, то лучше сразу, в начале процедуры обработки прерывания установить флаг IF в единицу. В большинстве случаев эту операцию нужно делать как можно раньше. Для установки флага IF в единицу в системе команд микропроцессора есть специальная команда, не имеющая операндов:

- sti — разрешить аппаратные прерывания.

Наиболее наглядный пример, показывающий важность своевременной установки IF, связан с отсчетом времени. Если вы не знакомы с тем, как ведется учет времени в компьютере, то уделим этому немного внимания. Как после включения компьютер определяет текущее время суток или как он запоминает информацию о своей конфигурации после выключения? Все дело в том, что компьютер имеет небольшую энергонезависимую память, которая питается от аккумулятора и не зависит от подключения к электросети. Конструктивно эта память выполнена на специальном типе полупроводниковых элементов с так называемой CMOS-структурой (Complementar Metal Oxide Semiconductor — комплиментарная МОП-структура). Особенность таких элементов памяти — в их пониженной по сравнению с обычными микросхемами потребляемой мощности (при этом они являются и более медленными, что в данном случае непринципиально). Аккумулятор кроме CMOS-памяти питает еще и микросхему системных часов, в функции которой входит отсчет текущих даты и времени суток. Таким образом, текущие значения даты и времени постоянно хранятся в CMOS-памяти и поддерживаются в актуальном состоянии даже после выключения компьютера. Кроме того, в CMOS-памяти хранится некоторая другая информация, в частности, о конфигурации компьютера. Во время загрузки компьютера дата и время считываются в область данных BIOS. Дальнейший отсчет времени, после загрузки системы, ведется уже с помощью системного таймера — другой микросхемы на системной плате, в функции которой входит регулярно, примерно 18,2 раза в секунду, генерировать сигнал, который в качестве прерывания подается на уровень irq0 контроллера прерываний i8259A. Во время работы компьютера соответствующая программа BIOS обрабатывает прерывание данного уровня и ведет счет времени. Если терять такты по этому входу, то фактическое время на часах будет отставать, и поэтому в большинстве случаев в обработчиках прерываний есть смысл как можно раньше выдавать команду sti.

Усовершенствованный программируемый контроллер прерываний APIC

- Подробности

- Родительская категория: Ввод-вывод

- Категория: Прерывания

В качестве замены традиционной паре контроллеров прерываний 8259 компания Intel в середине 1990-х годов разработала усовершенствованный программируемый контроллер прерываний APIC (Advanced Programmable Interrupt Controller). Хотя все процессоры, начиная с Pentium, поддерживают APIC, этот контроллер должен присутствовать на системной плате; кроме того, системная BIOS также должна поддерживать APIC. Поддержка APIC реализована на большинстве современных системных плат; контроллер APIC поддерживается операционными системами Windows, начиная с версии Windows 2000. Поддержку APIC можно разрешить или запретить, воспользовавшись программой BIOS Setup.

Контроллер APIC обеспечивает поддержку нескольких процессоров, однако может использоваться и в однопроцессорных системах. Основное преимущество APIC для однопроцессорной системы — поддержка виртуальных прерываний IRQ выше 15. Большинство реализаций APIC поддерживают виртуальные IRQ до 24. Хотя Windows 2000 старается назначать запросы на прерывания PCI IRQ в традиционном для устройств ISA диапазоне 0...15, причем даже при активном контроллере APIC, Windows XP и Vista полностью используют все возможности активного контроллера APIC. Для Windows XP/Vista контроллер APIC ограничивает совместное использование IRQ, что значительно сокращает количество конфликтов устройств. Например, при активном контроллере APIC запросы PCI IRQ могут быть распределены следующим образом.

- PCI IRQ 16. Интегрированный звуковой адаптер/видеоадаптер AGP (совместное использование).

- PCI IRQ 17. Дополнительный адаптер USB 1.1 (совместное использование отсутствует).

- PCI IRQ 18. Дополнительный адаптер USB 1.1 (совместное использование отсутствует).

- PCI IRQ 19. Сетевой адаптер 10/100 Ethernet/дополнительный адаптер USB 2.0 (совместное использование).

- PCI IRQ 21. Интегрированный контроллер USB 1.1 (3)/дополнительный адаптер USB 2.0 (совместное использование).

Традиционные запросы ISA IRQ 0...15 в данной системе использовались только для устройств ISA, тем самым предотвратив конфликты устройств ISA-PCI.

Чтобы обеспечить работоспособность необходимых служб APIC контроллер APIC должен быть активизирован в системной BIOS до установки Windows 2000/XP/Vista.

Примечание!

Контроллер APIC должен быть активизирован в системной BIOS до установки 64-разрядных версий Windows XP, 2003 и Vista.