Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

https://ткжби.рф купить аэродромные плиты паг 18. Магазин спортивной фармакологии анаболические комплексы купить в интернет магазине.

PCI и PCI-X

Специальные регистры устройств PCI-X

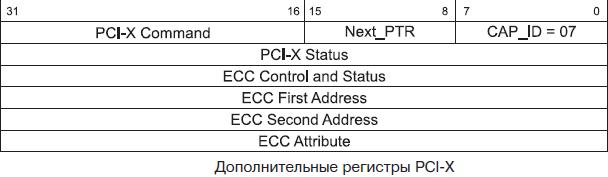

Устройства PCI-X имеют дополнительные регистры (см. рисунок ниже), положение которых определяется через список свойств (Capability ID = 07). Регистры для ECC-контроля появились только в версии PCI-X 2.0.

Регистр PCI-X Command служит для управления новыми свойствами протокола PCI-X:

- бит 0 (RW) — Uncorrectable Data Error Recovery Enable, разрешение попытки восстановления после обнаружения неисправимой ошибки. Если бит не установлен, по обнаружении ошибки четности будет формироваться сигнал SERR#;

- бит 1 (RW) — Enable Relaxed Ordering, разрешение установки признака RO в атрибутах транзакции;

- биты [3:2] (RW) — Maximum Memory Read Byte Count, предел для счетчика байтов в транзакциях чтения памяти: 0 — 512 байт, 1 — 1024, 2 — 2048, 3 — 4096;

- биты [6:4] (RW) — Maximum Outstanding Split Transactions, предельное число незавершенных расщепленных транзакций: 0…7 — 1, 2, 3, 4, 8, 12, 16, 32 транзакции соответственно;

- биты [11:7] — резерв;

- биты [13:12] (RO) — версия возможностей PCI-X (поддержка ECC):

---00 — ECC не поддерживается;

---01 — ECC только в Mode 2;

---10 — ECC в Mode 1 и Mode 2. - биты [15:14] — резерв.

Регистр PCI-X Status содержит идентификатор функции — ее адрес в иерархии конфигурационного пространства, который устройство «подсматривает» на шине, при выполнении операции конфигурационной записи. Этот идентификатор требуется устройству для передачи его в фазе атрибутов. Кроме того, в регистре имеются признаки возможностей устройства, а также индикаторы ошибок, связанных с расщепленными транзакциями. Назначение битов регистра PCI-X Status:

- биты [2:0] (RO) — Function Number, номер функции;

- биты [7:3] (RO) — Device Number, номер устройства, который оно узнает по значению AD[15:11] в фазе адреса конфигурационной записи, обращенной к данному устройству, выбранному линией IDSEL (после сброса устанавливается 1F);

- биты [15:8] (RO) — Bus Number, номер шины, который оно узнает по значению AD[7:0] в фазе атрибутов конфигурационной записи, обращенной к данному устройству (после сброса устанавливается FF);

- бит 16 (RO) — 64-bit Device, признак 64-битной шины AD;

- бит 17 (RO) — 133 MHz Capable, признак поддержки частоты 133 МГц (иначе 66 МГц);

- бит 18 (RWC) — Split Completion Discarded, признак отброшенного завершения расщепленной транзакции (запросчик его отверг);

- бит 19 (RWC) — Unexpected Split Completion, признак неожиданного получения завершения расщепленной транзакции;

- бит 20 (RO) — Device Complexity, признак сложного устройства (моста);

- биты [22:21] (RO) — Designed Maximum Memory Read Byte Count, максимальное число байт в последовательности, инициируемой устройством (его возможности): 0 — 512 байт, 1 — 1024, 2 — 2048, 3 — 4096;

- биты [25:23] (RO) — Designed Maximum Outstanding Split Transactions, предельное число незавершенных расщепленных транзакций: 0…7 — 1, 2, 3, 4, 8, 12, 16, 32 транзакции;

- биты [28:26] (RO) — Designed Maximum Cumulative Read Size, максимальный суммарный объем данных чтения памяти, ожидаемых устройством (запросы отправлены, ответы еще не получены): 0…7 — 8, 16, 32…1024 квантов ADQ;

- бит 29 (RWC) — Received Split Completion Error Message, признак получения сообщения об ошибке завершения расщепленной транзакции;

- бит 30 (RO) — PCI-X 266 Capable, поддержка режима PCI-X 266 (Mode 2);

- бит 31 (RO) — PCI-X 533 Capable, поддержка режима PCIX 533 (Mode 2).

Регистры ECC-контроля служат для управления контролем и диагностики. Регистр ECC Control and Status Register служит для управления ECC-контролем: разрешает ECC в Mode 1 (в Mode 2 ECC обязателен) и разрешает исправление однократных ошибок. В этом же регистре сообщаются признаки обнаружения ошибки, команды и фазы шины, в которой обнаружена ошибка, а также значения синдрома ошибки и атрибутов транзакции. Регистры ECC First Address, ECC Second Address и ECC Attribute Register содержат адрес, при обращении по которому обнаружена ошибка ECC, и атрибуты транзакции.