Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

Куртка druft черная мембрана pvh-membrany.ru. Все подробности жалюзи для домашних окон на нашем сайте.

Ввод-вывод

Шина ISA

Описание сигналов шины

- Подробности

- Родительская категория: Ввод-вывод

- Категория: Шина ISA

OSC: Генератор. Высокочастотные импульсы с периодом 70 нс(14.31818 МГц).

CLOCK: Системная частота (от процессора).

RESET DRV: Этот сигнал используется для сброса или инициализации системной логики при включении питания или при низком уровне напряжения на линии. Он синхронизирован с задним фронтом CLOCK и имеет активный высокий уровень (от процессора ).

SA0-SA19: Биты адреса с 0 по 19. Эти линии используются для адресации памяти и устройств ввода/вывода в системе. 20 адресных линий позволяют адресовать до 1 Мбайта памяти. SA0 — это младший значащий разряд, а SA19 — старший значащий разряд. Сигналы генерируются либо процессором или устройством ПДП. Они имеют активный высокий уровень. (от процессора ).

SD0-SD15: Биты данных с 0 по 15. Эти сигналы служат для передачи данных между процессором, памятью и внешними устройствами. D0 — это младший разряд, а D15- старший. Они имеют активный высокий уровень (двунаправлен).

BALE:Разрешение селекции адреса. Этот сигнал вырабатывается контроллером шины 82288 и используется на системной плате для защелкивания верного значения адреса от процессора. Он доступен на канале ввода/вывода как индикатор того, что значение адреса на магистрали верное (если используется вместе с AEN). Адрес защелкивается по заднему фронту сигнала (двунаправлен).

I/O CH CK: Проверка канала. Этот сигнал обеспечивает процессор информацией об ошибках четности памяти или внешних устройств в канале. Когда этот сигнал переходит в низкое состояние, регистрируется ошибка четности (в процессор).

I/O CHRDY: Готовность канала. Этот сигнал, обычно высокий, — переводится в низкое состояние памятью или внешним устройством для продления цикла обращения. Он дает возможность с минимальными затратами присоединять к системе устройства с низким быстродействием. Любое медленное устройство, используя этот сигнал, должно держать его в низком состоянии до тех пор, пока оно не проведет операцию распознавания адреса и не выполнит команду чтения или записи. Однако этот сигнал не должен оставаться в низком состоянии дольше 10 циклов синхронизации системы. Цикл обращения к памяти или внешнему уст-ройству увеличивается на целое число циклов синхронизации (в процессор).

IRQ3- IRQ15: Запрос на прерывание 3-15. Эти сигналы используются для передачи сообщения процессору о том, что устройство требует обслуживания. Они имеют разный приоритет. IRQ3 — с наивысшим приоритетом, а IRQ15 — с низшим. Запрос на прерывание вырабатывается при переходе сигнала из низкого состояния в высокое и удержании его до распознавания процессором (в процессор ).

IOR: Команда чтения из устройства. Данный сигнал указывает внешнему устройству на необходимость выставить свои данные на шину данных. Он может вырабатываться процессором или устройством ПДП. Активный уровень сигнала — низкий (от процессора ).

IOW: Команда записи в устройство. Этот сигнал сообщает устройству о необходимости ввода данных с магистрали. Он может вырабатываться как процессором, так и внешним устройством. Активный уровень сигнала — низкий (от процессора ).

SMEMR: Команда чтения памяти из пространства 1 Мбайт. Этот сигнал указывает памяти, что она должна выставить свои данные на шину. Он может вырабатываться как процессором, так и устройством ПДП. Активный уровень сигнала — низкий (от процессора ).

SMEMW: Команда записи в память из пространства 1 Мбайт. Данный сигнал указывает памяти на необходимость прочитать данные, выставленные на шину данных. Он может вырабатываться как процессором, так и устройством ПДП . Активный уровень сигнала -низкий (от процессора ).

MEMR : Команда чтения памяти: Этот сигнал указывает памяти, что она должна выставить свои данные на шину. Он может вырабатываться как процессором, так и устройством ПДП. Активный уровень сигнала — низкий (от процессора ).

MEMW: Команда записи в память. Данный сигнал указывает памяти на необходимость прочитать данные, выставленные на шину данных. Он может вырабатываться как процессором, так и устройством ПДП. Активный уровень сигнала — низкий (от процессора ).

DRQ0-DRQ3 DRQ5-DRQ7: Запрос ПДП 0-7. Данные сигналы являются асинхронными запросами канала периферийными устройствами для выполнения операций ПДП. Они имеют различный приоритет. DRQ7 — низший, а DRQ0 — высший. Запрос генерируется переводом соответствующего сигнала в активное (высокое) состояние. Сигнал должен удерживаться в высоком состоянии до тех пор, пока не станет активной соответствующая линия DACK (в процессор).

DACK0 — DACK7: Подтверждение ПДП 0-7. Эти сигналы используются для ответа на соответствующие запросы ПДП (0-7). Они имеют низкий активный уровень (от процессора).

AEN: Разрешение адреса. Данный сигнал используется для отключения процессора и других устройств от канала для проведения цикла ПДП. Когда этот сигнал активен (высокий), контроллер ПДП получает шину адреса, шину данных, а также линии чтения и записи (от процессора).

T/C: Счетчик завершения. На этой линии появляется импульс, когда достигнуто состояние счетчика завершения какого-либо устройства ПДП (от процессора).

REFRESH: Запрос на регенерацию динамической памяти (от процессора).

LA17-LA23: Незащелкиваемые адресные линии А17-А23 (двунаправлен).

SBHE: Показывает что старший байт данных находится на старшей шине данных SD8-SD15 (двунаправлен).

0WS: Сигнал показывает процессору что текущий цикл шины может быть выполнен без дополнительных тактов ожидания (в процессор).

MASTER: Сигнал перехвата управления внешним устройством системной магистрали (в процессор).

MEM CS16: Сигнал, подтверждающий то, что процессор может работать с этой памятью 16-разрядными словами без побайтовой распаковки (в процессор).

IO CS16: Аналогично, только с устройствами ввода/вывода (в процессор).

Помимо описанных сигналов, в канале ввода/вывода имеется ряд линий питания для устройств, подключенных к каналу.

Временные диаграммы

- Подробности

- Родительская категория: Ввод-вывод

- Категория: Шина ISA

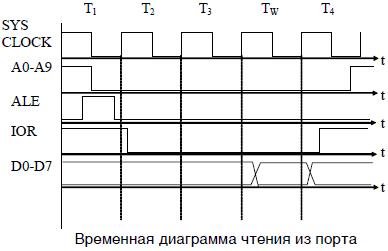

Чтение из порта ввода

Временная диаграмма операции чтения из порта (in port) занимает четыре такта опорной частоты и один такт ожидания (см. рисунок ниже). Само чтение данных происходит в начале четвертого периода. При необходимости удлинения времени чтения подают сигнал I/O CH RDY готовности канала, который увеличивает такт ожидания. Максимальное время ожидания определяется необходимостью регенерации памяти.

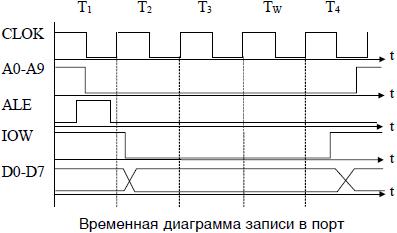

Запись в порт вывода

Временная диаграмма операции записи в порт (out port) занимает то же время, что и чтения из порта (см. рисунок ниже). Данные на шине находятся в течение всей длительности синхросигнала IOW.

В порт можно записывать и соответственно считывать как байт так и слово (два байта). Второй байт может появиться на старших разрядах шины данных или после первого — на младших разрядах. В первом случае внешнее устройство должно сформировать сигнал IO CS16, а процессор записать в (считать из) четный адрес порта. Если сигнал IO CS16 отсутствует, то запись первого и второго байта происходит в последовательные адреса портов, причем увеличение адреса порта на шине адреса происходит автоматически. При обращении к нечетным адресам считывается и записывается младший байт.

Структурная схема модуля на базе шины ISA

- Подробности

- Родительская категория: Ввод-вывод

- Категория: Шина ISA

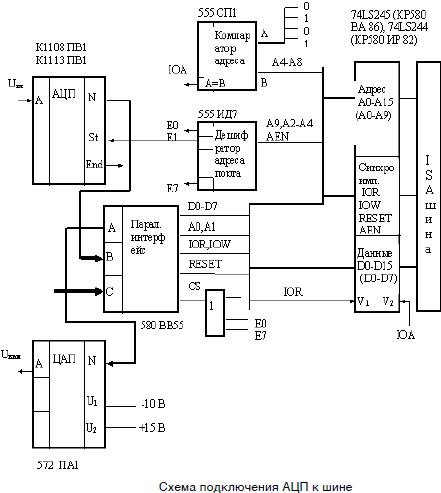

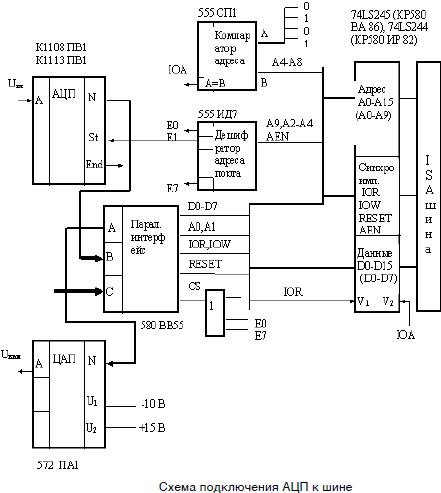

Подробная структурная схема модуля Plug in Data Acquisition Board приведена на рисунке (см. рисунок ниже). На рисунке показаны не только составляющие модуль элементы, но и перечислены микросхе-мы для их реализации.

В модуле можно выделить следующие элементы:

•буфер системной ши-ны,

•схему декодирования адреса порта,

•параллельный ввод-вывод КР580 ВВ55 (Intel 8255),

•микросхемы АЦП и ЦАП.

Буферизация содержимого системной шины. Схема декодирования адреса порта

- Подробности

- Родительская категория: Ввод-вывод

- Категория: Шина ISA

Буферизация содержимого системной шины

Необходимость буферизации определяется следующими причинами:

•Защита канала от больших напряжений, замыканий на землю;

•Защита от большой нагрузки при подключении к каналу большого числа потребителей (более 5), которые увеличивают емкостную нагрузку, вследствие чего изменяют временные параметры.

В качестве буфера можно использовать шинные приемо-передатчики, подключенные к соответствующим линиям канала.

В модуле используются следующие микросхемы:

•однонаправленные приемо-передатчики — 74LS245 (КР580 ВА 86),

•двунаправленные приемо-передатчики — 74LS244 (КР580 ИР 82). Последние применены для буферизации шины данных и включаются по сигналу AEN, а направление передачи определяет сигнал IOW.

Схема декодирования адреса порта

Элемент декодирования адреса порта предназначен для определения порта модулем. Номер порта в модуле задан аппаратно, и при совпадении в процессе декодирования этого номера с пришедшим (по шине адреса) модуль откликается на команду ввода-вывода (происходят те или иные действия).

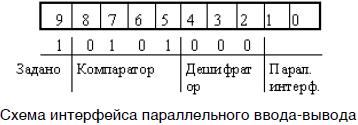

На рисунке ниже (схема подключения АЦП к шине) представлена двухкаскадная схема декодирования адреса. Она включает цифровой компаратор (555 СП1) и дешифратор (555 ИД7). На входе А компаратора жестко задан код 0101, а код адреса дешифратора определяется номером используемого выхода. Разряд А9 включает дешифратор. Младшие разряды А0, А1 задают номер канала параллельного интерфейса.

Адрес порта можно определить в соответствии с приведенной ниже схемой (схема интерфейса параллельного ввода-вывода).

Схема предназначена для подключения нескольких источников (приемников) данных к шине, а также для организации двунаправленного и стробируемого ввода-вывода (см. таблица ниже).

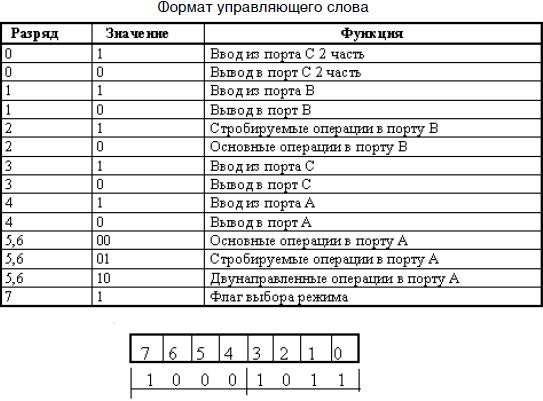

Микросхема параллельного интерфейса поддерживает несколько режимов работы по каждому выходу (А, В, С), выбор режима проводится подачей управляющего слова. Ниже приведен формат управляющего слова ().

Последняя картинка для того, чтобы порт А работал на вывод, а порты В,С — на ввод, необходимо записать управляющее слово.

В результате при работе со схемой (Схема подключения АЦП к шине) необходимо первоначально запрограммировать конфигурацию внутренних портов, а лишь затем считывать из АЦП или выводить в ЦАП информацию. Команды чтения и вывода аналогового сигнала будут иметь вид:

Port [$2A3]:=$8B;

A:=Port[$2A1];

Port [$2A0]:=A;